#### THE UNIVERSITY OF CALGARY

## Implementation of the Functional Architecture TIM

#### BY

` ؛

Michael Johann Hermann

#### A THESIS

### SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

#### DEPARTMENT OF COMPUTER SCIENCE

CALGARY, ALBERTA December, 1991

© Michael Johann Hermann 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Ottawa, Canada K1A 0N4

of Canada

National Library

Service des thèses canadiennes

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-315-75214-9

- - ---

# THE UNIVERSITY OF CALGARY FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled "Implementation of the Functional Architecture TIM", submitted by Michael Johann Hermann in partial fulfillment of the requirements for the degree of Master of Science.

### Ci Butiis le

Dr. G. M. Birtwistle, Supervisor Department of Computer Science

Dr. J. Kendall Department of Computer Science

ice

Dr. P. C. K. Kwok Department of Computer Science

Q. Presintureury

Dr. P. Prusinkiewicz Department of Computer Science

Dr. L. E. Turner, External Examiner Department of Electrical Engineering

Date December 13, 1991

## Abstract

Functional languages have enjoyed increasing popularity over the last few years, due to their advantages from the viewpoint of user, verifier, and implementer. There has likewise been an increase in the demand for special purpose architectures to efficiently execute them.

The abstract functional architecture TIM (Three Instruction Machine) is a developmental culmination in both sides of the dichotomy formed by notational representation for functional languages and procedural evaluation for functional architecture. TIM was proposed by Jon Fairbairn and Stuart Wray at Cambridge University, and is a compact and efficient frame-based graph reduction processor which executes SuperCombinators.

This thesis is an attempt to give TIM a concrete architectural form, with particular emphasis on the general design issues and methods of attack to be addressed in designing a functional architecture for practical application. Improvements in speed, efficiency, and implementability of the abstract machine are made, via changes to the organisation of memory, the structure of physical objects, and the contents of the instruction set.

Finally, I make some arguments as to the accessibility of the architecture, its merits as a research tool and a representative of a new sub-class of functional machine.

## Acknowledgements

I would like to express my deepest appreciation to my supervisor Graham Birtwistle, whose unfailing help and encouragement made this degree possible. Many students have enjoyed the benefit of your support and genuine concern, Graham, and I'm grateful for these *and* your eternal patience and enthusiasm.

A special thanks to my love Patricia Garner, who has supported me during the most difficult times and helped me see the light at the end of the tunnel. Your turn next, Hon.

Thanks to my parents, Gail and Kip, who respectively kept me there and got me there in the first place. A truly bright person is Cindy, who has always cared and will always deny it. The most capable guy I know is Arnold, who has taught me far more about life and people than I can gauge (he also cooks a mean brunch!). And, Paula is a true optimist who showed me the need for a balanced outlook.

Jon Fairbairn and Stuart Wray created the base on which this thesis is built; for this and their early help, I thank them. A lot of folks in the lab have made it interesting and enjoyable: Todd Simpson, Glenn Stone, Inder Dhingra, and Brian Graham. In particular, thanks to Cameron Patterson (an insightful, determined and thoroughly nice guy), for the opportunity to work on the ultimate sieve machine. Sieving über alles! Konrad Slind has been an acerbic wit, and the source of insightful commentary on my ideas and good common sense (sometimes we even talked about work). Simon Williams is an expert without par in VLSI, hardware design, T<sub>E</sub>X and more importantly motorcycles, who initiated me to the finer points of zooming. Thanks to Dan Marken for the early start in hardware, and Mrs. Olive Corriveau for a warm hearth and home.

Last but not least are Masoud Sahebkar, Winslowe Lacesso (hey, Windows!), Ian Olthof, David Pauli and Anja Haman who have been (variously) compatriots, co-conspirators, guides, rogues, confidantes, and always friends.

Financial support for this work was provided by the Alberta Microelectronic Center, the National Sciences and Engineering Research Council of Canada and the University of Calgary.

# Contents

| $\mathbf{A}_{\mathbf{j}}$ | pprov                                   | l Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ii                                                                               |

|---------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| $\mathbf{A}$              | bstra                                   | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iii                                                                              |

| A                         | cknov                                   | edgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iv                                                                               |

| $\mathbf{Li}$             | st of                                   | ables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | viii                                                                             |

| Li                        | st of                                   | igures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x                                                                                |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | duction         'unctional Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>1</b><br>1<br>4<br>7<br>8<br>9                                                |

| 2                         | Fun<br>2.1<br>2.2<br>2.3<br>2.4         | ional Programming         The Lambda-calculus         .1.1       The Pure λ-calculus         .1.2       Practical Aspects         .1.3       Theoretical Implications         .1.4       Strengths and Limitations         .2.1       Strengths and Limitations         .2.1       Strengths and Limitations         .3.1       Lazy Evaluation, Sharing, Strictness Analysis         .3.2       Strictness Analysis         .3.2       Strictness Analysis         .4.1       Strengths and Limitations | 11<br>12<br>13<br>14<br>16<br>18<br>20<br>23<br>24<br>24<br>24<br>25<br>26<br>29 |

|                           | 2:5                                     | unctional Language Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                               |

| 3                         | <b>The</b><br>3.1                       | Chree Instruction Machine         'unctional Architecture         .1.1         Environments and the SECD Machine         .1.2         Graph reduction and the Combinator Machine                                                                                                                                                                                                                                                                                                                         | <ul> <li>33</li> <li>34</li> <li>39</li> </ul>                                   |

|   |      | 3.1.3 Summary $\ldots$ $4$                                                                                |

|---|------|-----------------------------------------------------------------------------------------------------------|

|   | 3.2  | Three Instruction Machine                                                                                 |

|   |      | 3.2.1 The Three Instruction Rationale                                                                     |

|   |      | 3.2.2 Architectural blocks                                                                                |

|   |      | Code memory                                                                                               |

|   |      | Frame Heap $\ldots \ldots 4$ |

|   |      | System stack                                                                                              |

|   |      | 3.2.3 The Basic Instruction Set                                                                           |

|   |      | 3.2.4 TIM code compilation                                                                                |

|   |      | 3.2.5 Ground Types and Operations                                                                         |

|   |      | ALU instructions                                                                                          |

|   |      | 3.2.6 Implementing Laziness                                                                               |

|   |      | 3.2.7 Summary                                                                                             |

|   |      |                                                                                                           |

| 4 | Stru | uctural Optimisations 65                                                                                  |

|   | 4.1  | Optimisations to TIM 6                                                                                    |

|   | 4.2  | Design Philosophy 64                                                                                      |

|   | 4.3  | An Alternative TAKE                                                                                       |

|   | 4.4  | A Stack for Marks                                                                                         |

|   | 4.5  | Context Changes and Closures                                                                              |

|   | 4.6  | Conglomerate Frames                                                                                       |

|   | 4.7  | Conglomerate Frames and Tandem Mark Stack                                                                 |

|   | 4.8  | Summary                                                                                                   |

| 5 | Seco | ondary Optimisations 84                                                                                   |

|   | 5.1  | Frame Design                                                                                              |

|   |      | 5.1.1 The Frame Control Word                                                                              |

|   |      | 5.1.2 Self-Contained Closure Frames                                                                       |

|   | 5.2  | Marks and Updating                                                                                        |

|   | 5.3  | Objects and Direct Instructions                                                                           |

|   |      | 5.3.1 Reimplementing ENTER ARG instructions                                                               |

|   |      | 5.3.2 Eliminating the SELF Instruction                                                                    |

|   | 5.4  | Instruction Format Design                                                                                 |

|   | 5.5  | Summary                                                                                                   |

| ~ | C.   |                                                                                                           |

| 6 |      | nmary and Conclusions 10 <sup>4</sup>                                                                     |

|   | 6.1  |                                                                                                           |

|   | 6.2  | Future Work                                                                                               |

|   | 6.3  | Final Comments                                                                                            |

•

.

.

.

.

.

vi

/

•

### Bibliography

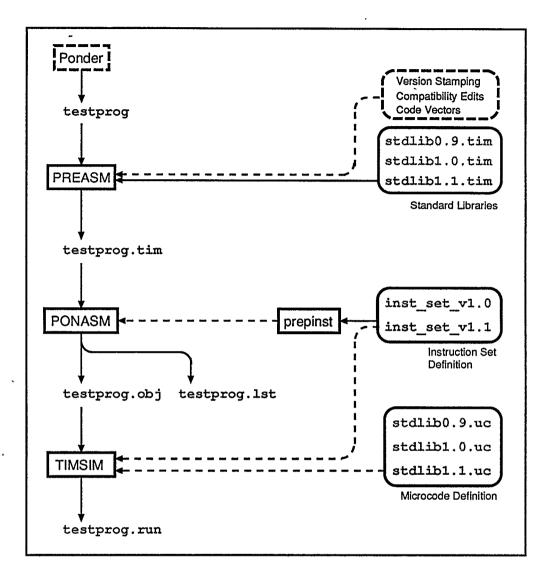

|        |               | Simulation Tool: TIMSIM   | 122 |

|--------|---------------|---------------------------|-----|

| A.1    | Applic        | ation to the TIM          | 122 |

| A.2    | TIMSI         | M Package Characteristics | 124 |

| A.3    | ure of TIMSIM | 126                       |     |

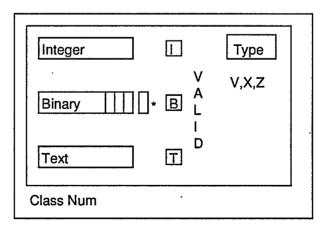

|        |               | Resource: Num             |     |

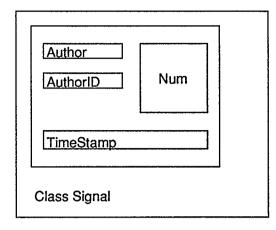

|        |               | Resource: Signal          |     |

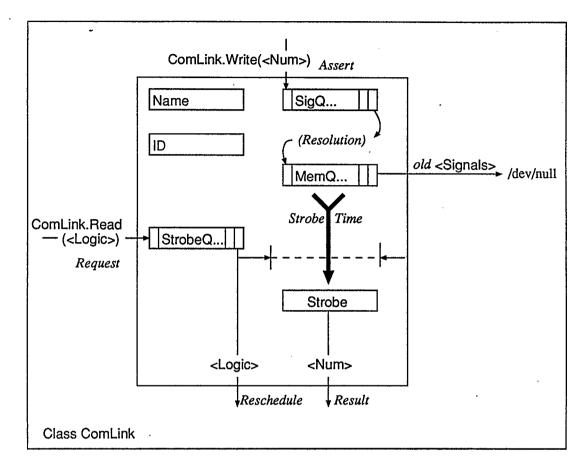

|        | A.3.3         | Entity: ComLink           | 130 |

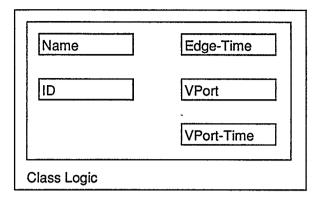

|        | A.3.4         | Entity: Logic             | 133 |

|        |               | Trace Facility            |     |

|        |               | User Interface            |     |

|        |               |                           |     |

| Append | lix B         | Simulation Environment    | 138 |

113

. ·

# List of Tables

| 2.1 | Size Complexity of Combinatory Logic 23                          |

|-----|------------------------------------------------------------------|

| 3.1 | Translation semantics for TIM code                               |

| 3.2 | TIM built-in operators 56                                        |

| 3.3 | TIM instruction set                                              |

| 4.1 | Breakdown of Memory Accesses by Operation                        |

| 4.2 | Overview of Material                                             |

| 4.3 | New TAKE and ALLOC costs                                         |

| 4.4 | Worst-case heap consumption with/out conglomerate suspensions 80 |

| 4.5 | Memory Usage for Conglomerate Frames and Mark Stack 81           |

| 5.1 | Overview of Material                                             |

| -   |                                                                  |

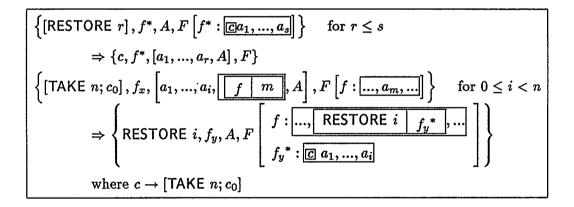

| 5.2 | The Standard TAKE Instruction                                    |

| 5.3 | New RESTORE and TAKE instructions                                |

| 5.4 | Sources of "Direct" Instructions                                 |

| A.1 | class Num interface                                              |

| A.2 | class Signal interface                                           |

| A.3 | Signal Resolution Rules                                          |

| A.4 |                                                                  |

| A.5 | class Logic interface                                            |

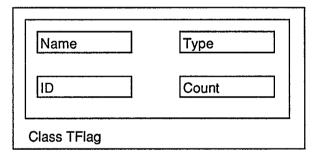

| A.6 | class TFlag                                                      |

|     |                                                                  |

|     | Varieties of Trace Flags                                         |

| А.ð | TIMSIM library package hierarchy                                 |

# List of Figures

.

| 1.1 The simplest TIM program                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.1 Pure $\lambda$ -calculus BNF                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                                                                   |

| 2.2 $\lambda$ -calculus conversions                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                                                   |

| 2.3 $\lambda$ -calculus if-then-else                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                                   |

| 2.4 Impure $\lambda$ -calculus partial BNF                                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                                   |

| 2.5a Developing a non-recursive definition                                                                                                                                                                                                                                                                                                                                                                                                       | 15                                                                   |

| 2.5b Fixed-point equivalence                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                                   |

| 2.5c Evaluation under Y fixed-point operator                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                                   |

| 2.6 Name-Capture                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                                                   |

| 2.7 Combinatory Logic BNF                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                   |

| 2.8 Basic Combinators and $\lambda$ -calculus equivalents                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                   |

| 2.9 SKI $\lambda$ -abstraction rules                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                                   |

| 2.10 Example of SKI abstraction                                                                                                                                                                                                                                                                                                                                                                                                                  | ${22}$                                                               |

| 2.11 Example of Lazy Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                                                                   |

| 2.12 Supercombinator definition                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                   |

| 2.13 Effect of parameter ordering on produced supercombinators                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ~ ~                                                                  |

| 3.1 SECD registers                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                   |

| 3.2 The SECD environment                                                                                                                                                                                                                                                                                                                                                                                                                         | 35                                                                   |

| 3.2 The SECD environment3.3a Function call instructions in SECD                                                                                                                                                                                                                                                                                                                                                                                  | 35<br>36                                                             |

| <ul> <li>3.2 The SECD environment</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                      | 35<br>36<br>36                                                       |

| <ul> <li>3.2 The SECD environment</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                      | 35<br>36<br>36<br>38                                                 |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation                                                                                                                                                                                                                                                                   | 35<br>36<br>36<br>38<br>40                                           |

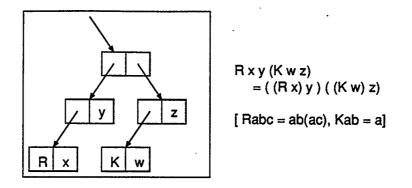

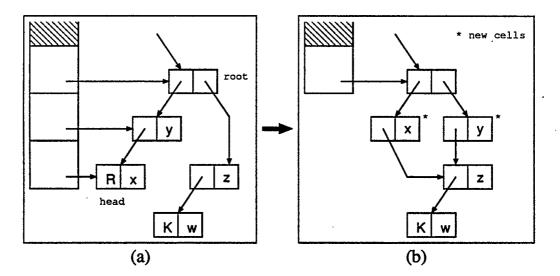

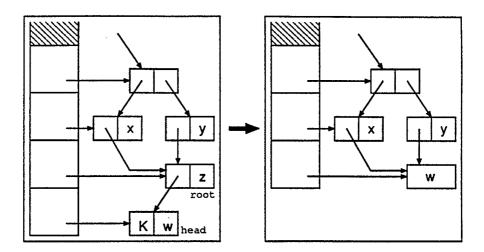

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction                                                                                                                                                                                                                                                 | 35<br>36<br>36<br>38<br>40<br>40                                     |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing                                                                                                                                                                                                                  | 35<br>36<br>36<br>38<br>40<br>40<br>41                               |

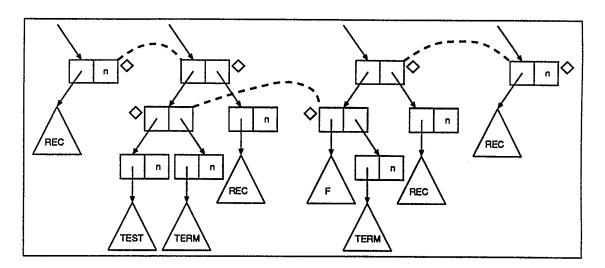

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences                                                                                                                                                                      | 35<br>36<br>36<br>38<br>40<br>40<br>41<br>47                         |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction                                                                                                                                           | 35<br>36<br>36<br>38<br>40<br>40<br>41                               |

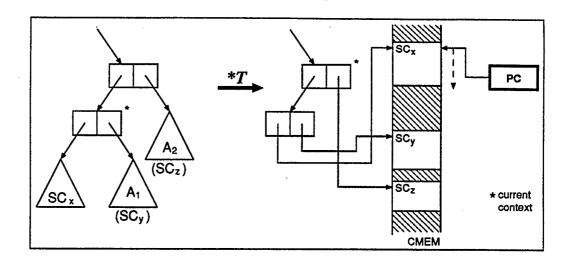

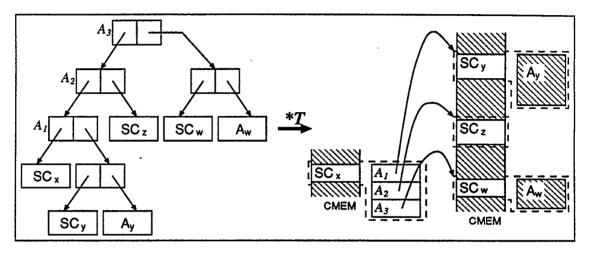

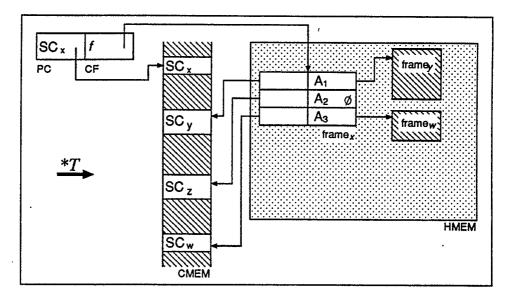

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction3.10Context frames are graph node conglomerates                                                                                            | 35<br>36<br>36<br>38<br>40<br>40<br>41<br>47                         |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction                                                                                                                                           | 35<br>36<br>38<br>40<br>40<br>41<br>47<br>48                         |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction3.10Context frames are graph node conglomerates3.12An example using Turner Combinators                                                     | 35<br>36<br>38<br>40<br>40<br>41<br>47<br>48<br>49                   |

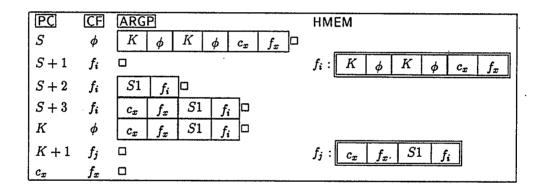

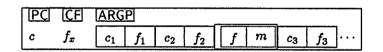

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction3.10Context frames are graph node conglomerates3.11The frame scheme3.12An example using Turner Combinators3.13Supercombinator and TIM code | 35<br>36<br>38<br>40<br>40<br>41<br>47<br>48<br>49<br>50             |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction3.10Context frames are graph node conglomerates3.12An example using Turner Combinators                                                     | 35<br>36<br>38<br>40<br>40<br>41<br>47<br>48<br>49<br>50<br>53       |

| 3.2The SECD environment3.3aFunction call instructions in SECD3.3bFunction preparation and application in SECD3.4Recursive function preparation SECD3.5The Graph Representation3.6Graph Reduction3.7Graph Reduction with Sharing3.8Argument graphs built with code sequences3.9Standard graph reduction3.10Context frames are graph node conglomerates3.11The frame scheme3.12An example using Turner Combinators3.13Supercombinator and TIM code | 35<br>36<br>38<br>40<br>40<br>41<br>47<br>48<br>49<br>50<br>53<br>54 |

.

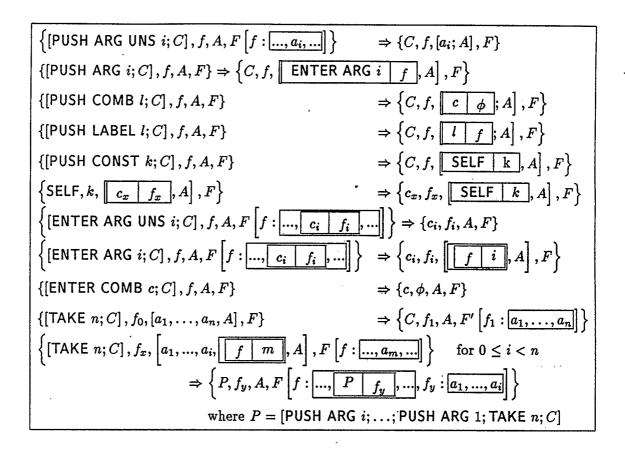

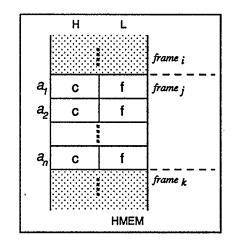

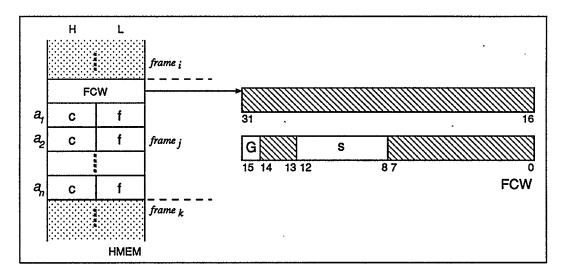

| 4.1  | Basic Logical Memory Structure of TIM 7      | 0        |

|------|----------------------------------------------|----------|

| 4.2  | The reimplementation of TAKE                 | 2        |

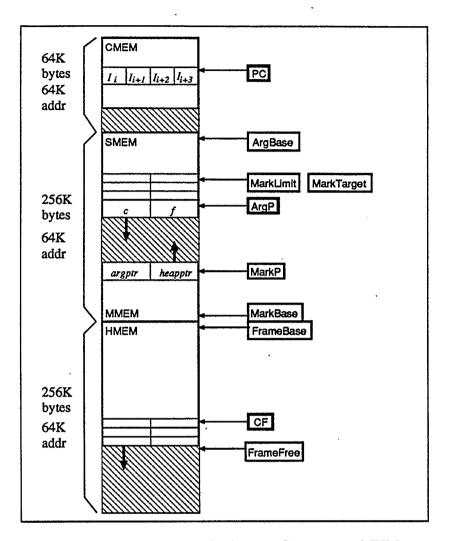

| 4.3  | Mark Storage Methods 7                       | 5        |

| 5.1a | Instruction-level frame structure            | 6        |

| 5.1b | Frame with FCW                               | 6        |

| 5.2  | Suspension restart vectors 8                 | 9        |

| 5.3  | FCW for self-contained frames 89             | 9        |

| 5.4  | Proposed test for degenerate marks 94        | 4        |

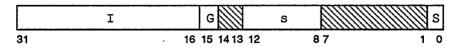

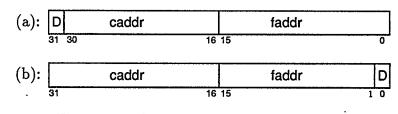

| 5.5  | Options for tag bit placement 99             | 9        |

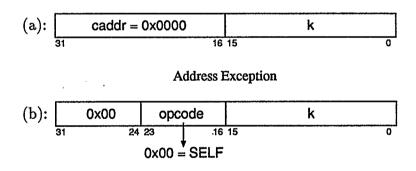

| 5.6  | Forms of the machine value object (SELF) 10  | 1        |

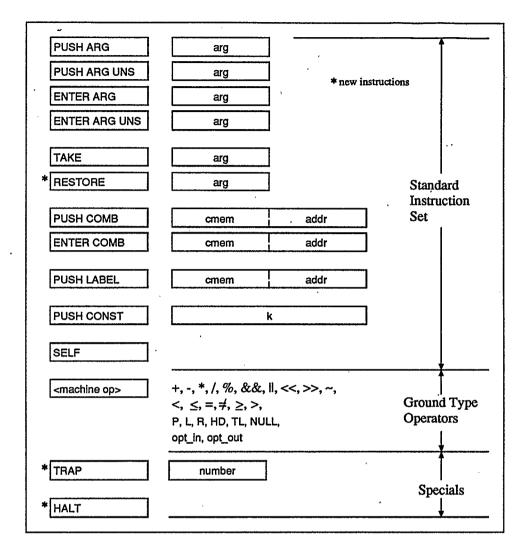

| 5.7  | The TIM instructions                         | <b>2</b> |

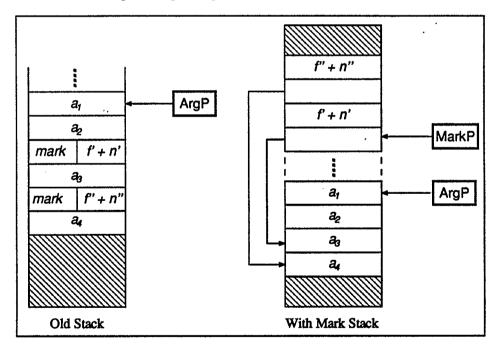

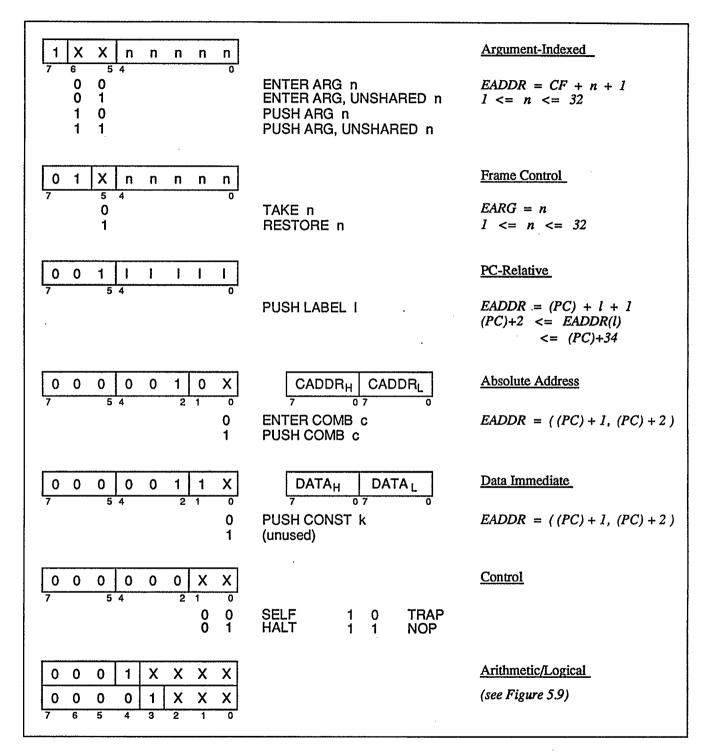

| 5.8  | Main TIM instruction formats and opcodes 104 | 4        |

| 5.9  | TIM ALU instruction opcodes 10               | 5        |

| A.1  | class Num                                    | 8        |

| A.2  |                                              |          |

| A.3  |                                              |          |

| A.4  | Sample Logic block                           |          |

| A.5  | class Logic                                  |          |

| A.6  | class TFlag                                  |          |

| B.1  | Overview of Environment                      | 9        |

| B.2  | Version control information                  |          |

|      |                                              | ÷.       |

,

. •

. •

## Introduction

In this chapter I introduce functional programming languages, outlining the main advantages and drawbacks these have over other programming language styles. From this I explain the need for machines specialised to execute functional languages, and describe the salient features of such functional architectures. The focus of this thesis is the Three Instruction Machine (TIM), of which I give a brief overview, and state the goals of my thesis work on TIM. I conclude with a list of the contributions of this work, and an outline of the thesis text.

#### **1.1 Functional Languages**

Functional programming languages derive their name from the basic operation intrinsic to their structure, that of applying a function to a single argument to produce a result:

$$fa \Longrightarrow r$$

(r may itself be another function). Functional programs consist entirely of such function definitions, which execute exclusively through the application of one to another.

The fundamental difference between functional languages and their ancestors in computer science arises from their mathematical nature: they contain no variables. While *imperative* languages such as Pascal and C use variables to maintain state through assignment, *applicative* languages maintain state only as *local arguments* to the currently executing function. Furthermore, the content of this state remains invariant, and is valid, only during the lifetime of the function call.

A more subtle distinction of functional languages is their strong basis in the

mathematical theory of computation. As opposed to the *post facto* derived mathematical basis of imperative languages, applicative languages have evolved from an abstract notation or *semantics* called  $\lambda$ -calculus. This has bestowed them with some surprising and very beneficial characteristics:

- Convenience The applicative programming environment is very simple to use. The absence of variables removes the effort normally required to define the type and scoping of storage. Functions are "first-class" entities, which may be treated as arguments, produced as results, and applied to other functions. This is a powerful tool that makes programming more intuitive, and makes programs more succinct and expressive. Conventional programming structures such as lists and abstract data types still exist. The result is a class of languages with clearer semantics, fewer details to look at, more compact and expressive operations, and shorter development times.

- Typing and polymorphism These form a hierarchy of compile-time techniques that provide an additional convenience feature to the programmer. Type refers to the class of information represented, ranging from base types (ie. integer) to conglomerate types specifying functions or abstract data structures. The techniques range from simple type checking based on user-specified type information, to type inference in which the compiler automatically resolves all type information itself. Polymorphic types incorporate "wild cards" which match other types, allowing the re-use of single function definitions on multiple types. By rigorously enforcing rules of function application and usage, the compiler quickly flags "type clash" errors, while simultaneously guaranteeing that no (often costly) run-time type errors can occur.

- Nondeterminism and optimised execution This encompasses a number of areas such as *lazy evaluation*, *strictness*, and *sharing analysis*. "Laziness" or nondeterminism allows computations to be postponed until absolutely necessary, preventing unnecessary work and providing bonuses such as infinite structures and partial evaluations. To avoid redundant work, each computation result

may be shared amongst all references to that work. Strictness analysis determines which work *must* be done, so that the extra overhead of laziness and sharing can be avoided where unnecessary, and work may be more optimally scheduled.

- Correctness Software verification is assuming growing importance, but faces difficult complexity problems. Imperative languages suffer from "side-effects" (unforeseen state changes amongst sections of code) and semantic weaknesses that complicate program proofs. In contrast, the lack of variables and applicative semantics of functional languages make them attractive to the verification community.

- Simple parallelism The underlying  $\lambda$ -calculus notation provides some characteristics, illustrated by the lack of "side-effects", which allow for arbitrary execution mechanisms (including n-ary parallelism), and arbitrary partitioning of any functional program. This makes functional languages very attractive for multi-processing environments.

Functional languages have left their infancy as a *de facto* standard set of features and capabilities have emerged. Languages such as Miranda [Tur85], Hope [BMS80] and SML [HMM86, Har86] are far better than their predecessors. Functional languages are still not as competitive as they could be with their imperative counterparts, partly from a lack of exposure in the user community. Improvements in the clarity and versatility of semantic structures, provision of larger standard function libraries, and educating users on the functional programming style will encourage expanded use of functional languages. However, the largest problem is that of providing comparable compiler efficiency and execution performance.

The advantages of functional languages don't come for free. On a first approximation, the use of local state, and the applicative style itself make functional programming more expensive in terms of memory usage and the degree of "copying" (of local state) that is required. In the search for performance, software has traditionally migrated to hardware; with the settling of functional languages, and their unique execution requirements, the design of special-purpose *functional architectures* is a logical undertaking.

#### **1.2 Functional Architectures**

The major business of any architecture is the movement and storage of data. Hardware is simply a crystallisation of algorithm, and a physical machine must reflect the execution behaviour and storage use patterns of the source language which it evaluates. The patterning of physical structure after logical structure is thus central to the success of any architecture.

Backus [Bac78] makes this observation with regard to "conventional" architecture, grouping Von Neumann and Harvard style machines together as variants on the familiar Central Processing Unit (CPU)-Bus-Memory theme. On this alone the argument would fail, as this structure is common to nearly all computer architectures. However, Backus continues by arguing that the imperative programming style on which these machines is based is deeply ingrained in their design. The semantics of imperative programming naturally engender the use of such simple things as single-word wide instruction streams, user-accessible general purpose registers, and so forth. Further, this natural reflection of structure forever colours the character and capabilities of these architectures towards the service of the imperative style.

It follows that functional languages should have their own native style of architecture, which would execute them with greater utility. In many cases, a target non-native architecture can provide unnecessary *obstacles* to the efficient execution of a functional language. These obstacles frequently manifest themselves in instructions that require specialised sequences of non-native operations or unique logical structures; a good illustration is tag manipulation. Thus even a simple implementation of a functional architecture will be better than a non-native machine, if the basic needs of functional languages are being served, and the transistor budget is not being wasted on unnecessary functions.

What are these basic needs? The logical characteristics of functional languages indicate the physical form that a generic native functional architecture should take.

There are a number of observations from which the general nature of a functional architecture is derived:

- Applicative style The functional style encourages short-bodied and short-lived functions. The resulting sustained high rate of function calls predicts a need for rapid context changes, with attendant copying operations and movement of logical entities. This predicates large amounts of storage with fast access times, and extensive CPU support for executing function calls.

- Allocatable store The transient nature of most storage usage, and the additional storage requirements for laziness and sharing, means there must be at least one (and perhaps several) groups of allocatable logical storage elements. There will certainly be firmware/hardware support for allocation and garbage collection, including special control and storage use information. In some instances, the use of multiple physical memories may be beneficial.

- Simple instruction sets Due to the proximity of functional languages to their common ancestor  $\lambda$ -calculus there is a small "semantic gap" [Mye78] between language and machine. Programs typically compile into a handful of basic operations, where the operations themselves usually require only a 0- or 1- operand specification (typically a constant or a reference to memory). Thus, the instruction set of the CPU will be small and limited in scope, there will be no user-reachable general purpose registers, and most details of the CPU will be hidden from the user.

- Complex internal structure In contrast with the last point, while instruction decoding may be simplified, the instructions themselves often represent highly complex operations. When using techniques such as lazy evaluation and sharing, many internal tests and the movement and manipulation of much information is necessary, especially for those instructions controlling context changes. Such instructions will naturally require many clock cycles, the use of internal book-keeping registers, and a correspondingly more complex control unit.

- Limited locality In comparison to their imperative cousins, we can expect applicative languages to exhibit much different memory reference patterns. Spatial and temporal locality will be affected by the rapid function calls, arguing against the utility of hardware accelerators (such as caching) as they are commonly used in conventional architecture. Improving memory performance will present new challenges to the hardware designer.

- Hooks for parallelism With the isolation of functions from each other, parallel execution is made more tenable by the lack of code interdependence. While the scheduling of instructions on a fine-grained multiple execution unit processor would still retain about the same difficulty, breaking the program into functionsized chunks or larger for scheduling on a coarse-grained multiprocessor is much easier.

To summarise, the semantics of functional languages places special emphasis on the quantity and structure of storage, the uses to which it is put, and the efficient movement of data within and between the CPU and memory. Judging by the large numbers of abstract functional architectures that have been designed [Hen80, CGMN80, Tur84, Car84, Joh87, CCM87, Tra85], these lessons have not been lost on the functional programming community. A few of these abstract machines have also been built [Sto85, Sch86, Ram86, GWB<sup>+</sup>89].

A full blown implementation of a functional architecture would be able to make use of the same performance enhancements that have been used in other architectures for years. A speed-optimised machine design would use microcoding for the complex instructions and subsidiary concurrent operations, pipelining to accelerate the data and control paths, virtual memory and hardware allocation/collection of memory for the more storage-consumptive execution, control unit redundancies to hold multiple contexts and enable faster function calls and returns, and instruction and data memory caching. However, while these are all valuable tools to use, the critical effort comes in designing the machine concept properly for the functional programming paradigm.

#### **1.3** The Three Instruction Machine

The Three Instruction Machine (TIM) was proposed by Jon Fairbairn (Cambridge University) and Stuart Wray (Olivetti, UK). TIM is an abstract functional machine tailored to execute a specialised form of  $\lambda$ -calculus called Combinatory Logic (specifically SuperCombinators, see Chapter 2). TIM uses graph reduction as an evaluation mechanism, a technique in which a program is distributed in a logical tree structure, and execution proceeds through a "pruning" process that gradually evaluates portions of the program and replaces them with their results. This is a common mechanism amongst functional architectures, but TIM is distinctive in both the way that it represents programs as graphs, and the method it uses to evaluate them. The major drawbacks with previous graph reduction schemes are the amount of time spent traversing the tree structure, and the amount of memory consumed in its representation. TIM uses an innovative approach to abstract most of the program code from the graph, leaving essentially only the call-structure of the program. This greatly abbreviates the tree structure. In addition, TIM supports nondeterministic evaluation and sharing, addressing the unique control problems of each within the new graph reduction scheme.

The three TIM instructions are called PUSH, ENTER, and TAKE. These roughly represent the three stages in a function call:

- 1. PUSH some number of arguments to the function into temporary storage.

- 2. ENTER (call) the function, the code portion of the new context.

- 3. TAKE the supplied function arguments, as the environment portion of the context.

So for the generic functional program, the instructions operate as in Figure 1.1. There are also a host of built-in ALU operations.

The abstract machine is outwardly simple, but it holds a few surprises for the unwary. "Three Instruction Machine" is a somewhat deceptive title, as there are actually a few variants or "flavours" of both PUSH and ENTER, which specify the type of logical entity being referenced (*ie.* a constant, a combinator "function" reference,

| $fa \Longrightarrow r$ | PUSH a<br>ENTER f<br>TAKE 1 |  |  |

|------------------------|-----------------------------|--|--|

|                        | $\vdots$ (return) $r$       |  |  |

Figure 1.1: The simplest TIM program

or a proper argument). Since TIM implements sharing, there are supplementary arguments to each instruction that provide control information, and specify which computations are shared.

The basic instructions have very different complexity; while some instructions are very simple and execute in one or two machine cycles, others are very complex and can take tens of cycles. Thus some instructions are natural bottlenecks, and will draw heavily on hardware resources to prevent detrimental effects to machine performance.

However, the basic abstract machine is reasonably straightforward. The most complex problems arise from implementing the many architectural optimisations that are discussed in Chapters 4 and 5. TIM holds a number of challenges for the designer charged with implementing the abstract definition as a practical working architecture.

#### 1.4 Contributions of the thesis

The goals of this thesis are:

- 1. to evaluate potential improvements to the abstract architectural definition of TIM, and

- 2. provide a concrete design for selected best optimisations.

The central contributions of the thesis are:

1. evaluation of a number of optimisations to TIM proposed in the literature, and where applicable, comparison of reported results to replicate or refute.

- 2. evaluation of a number of optimisations proposed by the author.

- 3. specification of some improvements to the abstract TIM design.

- 4. design of the instruction format, logical objects and a partitioned memory system to support the storage and high throughput needs of the TIM processor.

- 5. development of a DEMOS-based [Bir79] logic simulation package, with performance measurement instrumentation and design debugging support.

#### 1.5 Structure of this thesis

- Chapter 2 is an introduction to functional languages, their theoretical characteristics, and some practical examples of their use. I quickly examine the underlying notation of  $\lambda$ -calculus, touching on the work of Church and Rosser, the specialisation of  $\lambda$ -calculus to combinators, and place special emphasis on SuperCombinators, the source notation of TIM. A brief discussion of "lazy" evaluation of expressions, sharing analysis and strictness analysis is included.

- Chapter 3 outlines the abstract TIM machine as proposed by the original developers. I initially describe two notable functional architectures which have been built, which represent opposite ends of the spectrum of functional architectures, and illustrate two important components in the TIM architecture. I explain the philosophy of the TIM machine, describe the structures and basic instruction set, additional instructions for ground types, and those used to implement lazy evaluation.

- Chapter 4 begins with a brief overview of the set of possible optimisations, followed by the design issues in TIM, goals I have specified for the design and a design philosophy developed to attain them. The bulk of this chapter discusses structural optimisations surrounding the TAKE instruction, covering aspects of context changes, creation and maintenance of sharing information, and the updating of shared results. Approximately one half of this material is new and original work, in the form of extension and analysis.

- Chapter 5 focuses on lower-level optimisations, and implementation of the TIM machine including the instruction set and use of storage. I propose a new model of the frame heap and a new instruction, used to speed context changes and the use of shared evaluations in TIM. Approximately 90% of this material is new and original.

- Chapter 6 summarises the contributions of this thesis, outlines some possible future work, and gives some final comments.

## **Functional Programming**

Functional programming has developed in the areas of software notations, evaluation strategies, and hardware structures, with growth in one area encouraging growth in the others. This is no accident; in functional programming the notation encodes its own evaluation algorithms, and hardware is simply a hardwired form of algorithm. Thus functional language and special architectural support are intimately related.

In the past, mainly notations and methods of evaluation were explored, and the interest in hardware was limited to the pervasive *abstract machine*. Now that some stable notations and evaluation strategies have settled out of the previous work, real hardware is being more aggressively explored for the next efficiency gains.

The purpose of this chapter is to illustrate key concepts of functional languages, by examining the notational genealogy of the Three Instruction Machine. This will supply the background information necessary for the reader to understand the first two of the three facets of TIM: notation (supercombinators), methods (lazy evaluation, sharing) and structure (stack-based graph reduction), preparatory to concentrating on the third in Chapter 3.1.

I will outline the development of notations up to supercombinators, illustrating the gradual improvements in efficiency and discussing some of the tools used to achieve these gains. A great deal of work has gone into understanding functional languages, how best to apply them to problems, creating type inference mechanisms, and so forth. Much of this work has been aided by the fact that all functional languages have a common mathematical basis, from which each may gain the same power, and be amenable to the same analysis techniques. This basis is the  $\lambda$ -calculus, and it is the intrinsic properties of  $\lambda$ -calculi that are in large part responsible for the success of functional programming languages. The knowledgeable reader may safely skip this chapter. Those who wish to know more are referred to [Hug89], which outlines the arguments for functional programming, and [Kle81], which gives an historical account of its development. [Bar81b] is a comprehensive introduction to the  $\lambda$ -calculus, and [CF58, CHS72] are the standard references for combinatory logic. [HS86] treats theoretical aspects of the above, while [Pau87] and [Sto77] focus on program verification and typing of functional languages, respectively. [Gor88] is a teaching text for semantic analysis which covers  $\lambda$ -calculus, combinatory logic and supercombinators. [BW88], and more so [Pey87] and [FH88] are comprehensive, broad overviews of functional programming, including notations, evaluation strategies and architectures.

#### 2.1 The Lambda-calculus

Functional programming got its start from a simple notation called the Lambda Calculus or  $\lambda$ -calculus. The  $\lambda$ -calculus is a formal abstraction originated by Church [Chu41] to provide a theoretical basis for mathematics, a task for which it proved inadequate [Ros84]. It lay dormant for many years, before computer scientists found that it was useful for reasoning about computation and the semantics of algorithms.  $\lambda$ -calculus could be used to separate program syntax (how an algorithm is written) from program semantics (how the algorithm operates, and what it *does*), isolating the meaningful from the extraneous.

An early exploration by Landin used the  $\lambda$ -calculus to provide an operational semantics for ALGOL60 [Lan65a, Lan65b], with which ALGOL60 programs could be understood and verified correct through "abstract evaluation". This developed from previous work where Landin introduced the use of  $\lambda$ -calculus as a semantic analysis notation, and created an abstract machine called the SECD which could execute the new notation directly [Lan64]. The notion of a language which held both a "program" and the method of its execution implicit in the program definition was to become central to the field of functional programming, and  $\lambda$ -calculus was to become the common denominator in much of the research to follow.

#### 2.1.1 The Pure $\lambda$ -calculus

The "pure"  $\lambda$ -calculus has only three constructs, as they appear in Figure 2.1. These are argument names (any tag symbol V introduced in an abstract function), function applications (read as function  $E_1$  applied to argument  $E_2$ , where E is any  $\lambda$ -expression), and abstract function definitions, in which V is the tag name for zero or more occurrences of an argument in the function body E. These three semantic structures are the simplest expression of the essentials of functional computation, and form the common denominator for all functional languages.

$$E ::= V$$

(argument name)

|  $(E_1E_2)$  (function-argument application)

|  $\lambda V.E$  (abstract function)

Figure 2.1: Pure  $\lambda$ -calculus BNF

To evaluate an  $\lambda$ -calculus expression, it is converted to another semantically equivalent form; the "conversion" rules (see Figure 2.2) governing  $\lambda$ -calculus are likewise few and simple. The first and third,  $\alpha$ -conversion and  $\eta$ -conversion, are used to rename a argument, and to add or delete arguments as needed, respectively. The most important rule is  $\beta$ -conversion, which applies functions to arguments. The notation " $E_1[E_2/x]$ " is short for "the expression  $E_1$  with argument expression  $E_2$ substituted for all free occurrences of x". In other words, reading from left to right this retrieves the outside argument  $E_2$ , "binds" it to the internal argument name x, and replaces free occurrences of the symbol x within  $E_1$  by the expression  $E_2$ .

| $\lambda x.E$        | ⇔                        | $\lambda y.E[y/x]$ | (renaming)<br>where $x$ is not free in $E$ )            |

|----------------------|--------------------------|--------------------|---------------------------------------------------------|

| $(\lambda x.E_1)E_2$ | $\stackrel{\beta}{\iff}$ | $E_1[E_2/x]$       | (function application)                                  |

| $\lambda x.Ex$       | $\stackrel{\eta}{\iff}$  | E                  | (argument abstraction<br>where $x$ is not free in $E$ ) |

#### Figure 2.2: $\lambda$ -calculus conversions

The execution of  $\lambda$ -calculus programs is called "reduction", and uses the left-toright forms of  $\beta$ -conversion and  $\eta$ -conversion with the normal  $\alpha$ -conversion. Execution proceeds as a search for reducible expressions, or "redexes", which are then rewritten using the rules. As an example, consider a simple predicate:

| Operation                                           | Comment                  |

|-----------------------------------------------------|--------------------------|

| if false then A else B                              |                          |

| $\implies (\lambda txy.txy)$ false $A B$            | $(if = \lambda txy.txy)$ |

| $\stackrel{\beta}{\Longrightarrow} (false \ A \ B)$ | $(3 \beta$ -reductions)  |

| $\implies (\lambda xy.y) \land B$                   | $(false = \lambda xy.y)$ |

| $\stackrel{\beta}{\Longrightarrow} (\lambda y.y) B$ | $(eta	ext{-reduction})$  |

| $\xrightarrow{\beta} B$                             | $(eta	ext{-reduction})$  |

Figure 2.3:  $\lambda$ -calculus if-then-else

The process of "reduction" implies that the size of the expression is reduced, but this is not always the case. Program execution is complete when we run out of redexes or further applications of the rules to existing redexes no longer change the expression; this is known as "normal form".

Despite its simplicity, every computable function can be expressed in  $\lambda$ -calculus ("Church's Thesis", [Chu36]). That is, it possesses the same power as any other programming language in use. As with "if-then-else", integers, lists, pairs, datatype constructs and others can all be expressed in terms of the  $\lambda$ -calculus, albeit inefficiently.

#### 2.1.2 Practical Aspects

In practice, a fourth construct (Figure 2.4) is added to the pure  $\lambda$ -calculus. Constants are used for ground types and their atomic operations, such as the natural numbers and the operations  $+, -, x, /.^{1}$

Implementing recursion in the  $\lambda$ -calculus is a sticky problem. Unlike higher-level languages,  $\lambda$ -calculus is *nameless* apart from the tags used for arguments. A recursive

<sup>&</sup>lt;sup>1</sup>Pure  $\lambda$ -calculus is restricted to an inefficient unary integer representation; this is a common practical optimisation.

$\begin{array}{cccc} E & ::= & \dots \\ & | & C & (\text{constant}) \end{array}$

Figure 2.4: Impure  $\lambda$ -calculus partial BNF

function refers to itself, and so cannot be directly expressed in the  $\lambda$ -calculus. We must use a "trick" to provide recursion, by converting recursive functions into a non-self-referential form, in which the function obtains its own definition as an argument. This argument is then used for the "recursive" function call. As an example, consider a recursive multiply function (Figure 2.5a):

$\begin{array}{ll} \mathsf{mpy} = \lambda \ p \ q & if \ ( \ p = 0 \ ) \ then \ 0 \ else \ ( \ q \ + \ ( \ \mathsf{mpy} \ ( \ p \ - 1 \ ) \ q \ ) \ ) \\ \mathsf{let} & \mathsf{M} = \lambda \ f \ p \ q. \ if \ ( \ p = 0 \ ) \ then \ 0 \ else \ ( \ q \ + \ ( \ f \ ( \ p \ - 1 \ ) \ q \ ) \ ) \\ \mathsf{(\beta-conversion)} \\ \mathsf{then} & \mathsf{mpy} = \mathsf{M} \ \mathsf{mpy} \\ \mathsf{and} & \mathsf{mpy} = \mathsf{Y} \ \mathsf{M} \\ \end{array}$

Figure 2.5a: Developing a non-recursive definition

To provide the copies of the function definition as needed, we use the artifice of a "fixed-point operator". Denoted "Y", each time this operator is applied to an argument, it returns a copy of the argument as well as the original application. Thus the initial application pair remains unchanged:

$$\underline{\mathsf{Y}}\underline{f} \stackrel{\beta}{\Longrightarrow} f(\underline{\mathsf{Y}}\underline{f}) \stackrel{\beta}{\Longrightarrow} f(f(\underline{\mathsf{Y}}\underline{f})) \stackrel{\beta}{\Longrightarrow} \cdots$$

The (Yf) pair is a *fixed-point* of M, and is in effect a catalyst for the recursive computation, moderating it but remaining unchanged. To see how a recursive function is translated, we start with the definition of a recursive function called mpy (Figure 2.5a). First  $\beta$ -conversion is used to abstract away the function name, and replace it with an argument; the external parameter "mpy" represents the mpy function definition needed for a recursive call to succeed. The last step is to discard the function name, and add the Y operator to implicitly replace it with the mpy definition. Simplified, the process is as in Figure 2.5b.

Under execution, the fixed-point pair (YM) is applied to the regular function arguments, and immediately rewrites itself as the function M applied to the fixed-

| mpy = mpy-body                                               | $mpy-body = \lambda \ m \ n \ . \ \textit{if} \cdots mpy \cdots$ |

|--------------------------------------------------------------|------------------------------------------------------------------|

| $\Leftrightarrow \overset{\beta}{\longleftrightarrow} M mpy$ | $M = \lambda f. \text{ mpy-body } [f / \text{mpy }]$             |

| = Y M                                                        |                                                                  |

| = M (Y M)                                                    | proof: invoke Y                                                  |

| = M mpy                                                      | proof: $mpy = Y M$                                               |

|                                                              |                                                                  |

Figure 2.5b: Fixed-point equivalence

point pair and the other arguments. Execution continues with the body of M. See Figure 2.5c.

```

mpy 3 2

YM 32

=

M(YM)32

_

(invoke Y)

[\lambda f p q . if (p = 0) then 0]

else (q + (f(p-1)q)) (YM) 32

if (= 30) then 0 else (2 + ((YM)(3-1)2))

=

(apply arguments)

2 + ((Y M) 2 2)

=

(resolve predicate)

2 + (M(YM) 2 2)

=

(invoke Y)

2 + ([\lambda f p q] \cdot if \cdots f (p-1) q] (Y M) 2 2)

=

(the full definition)

2 + (2 + (2 + ((Y M) 0 2)))

=

```

Figure 2.5c: Evaluation under Y fixed-point operator

Mutually recursive functions are handled by encapsulating the definitions as a single argument, to be extracted for function calls as needed.

One  $\lambda$ -expression definition<sup>2</sup> for Y is  $(\lambda h.(\lambda x.h(xx))(\lambda x.h(xx)))$  and others have been suggested by [CF58, CHS72, Bar81b]. [Hud89] states that fixed-point operators are inadequate for typed  $\lambda$ -calculi and non-standard evaluation mechanisms, and suggests other methods of implementing recursion.

#### 2.1.3 Theoretical Implications

The mathematical basis of  $\lambda$ -calculus is responsible for many of the assets of functional languages, mainly through the ease of developing and extending formalisms. The greatest asset of the  $\lambda$ -calculus is derived from a set of basic results called the

<sup>&</sup>lt;sup>2</sup>from [Pey87], pg. 26

"Church-Rosser" properties [CR36]<sup>3</sup>, which address the evaluation of  $\lambda$ -expressions and their convertibility one to another:

Theorem 1 (Church-Rosser) Given two  $\lambda$ -expressions X and Y, if  $X \iff Y$ , then there exists a  $\lambda$ -expression Z such that  $X \Longrightarrow Z$  and  $Y \Longrightarrow Z$ .

Corollary 1 (Church-Rosser) No expression can be converted to two distinct normal forms.

**Theorem 2 (Church-Rosser)** If A red B, and B is in normal form, then there exists a normal order reduction from A to B.

Theorem 1 states that any two interconvertible (" $\iff$ " denotes any  $\alpha$ -,  $\beta$ - or  $\eta$ -conversions) expressions will have a common result expression through reduction (" $\Longrightarrow$ " using  $\beta$ , $\eta$ -reduction). More generally, a single expression may be evaluated in many different ways, but all the interim results are interconvertible, and so will (eventually) reduce down to a single result. An inductive argument on theorem 1 states this clearly in corollary 1, where *normal form* means "fully evaluated".

Theorem 2, or the "Normalisation Theorem", states if an expression can be reduced down to its normal form, then there is a well-defined method of reduction that always attains the normal form. *Normal-order* reduction always applies  $\beta$ -reduction to the leftmost-outermost redex first, until no more such redexes exist.

Taken together, these three statements provide two guarantees:

- 1. evaluate the redexes of an expression in any order. If the evaluation produces a result (doesn't loop infinitely), the result is correct.

- 2. if you evaluate a (terminating) expression in normal order, you will terminate with a result, and that result will be correct.

The same holds for any operations we split in pieces and do in parallel (the most obvious place being amongst arguments at a function application).

The practical upshot of the Church-Rosser theorems as they apply to  $\lambda$ -calculus, and by extension to all functional programming languages, is that the evaluation

<sup>&</sup>lt;sup>3</sup>more accessible proofs are available in [CF58, HLS72, HS86]

mechanism we use is immaterial to our results. We can break a program up in any way we want, execute the pieces in any order, and if we get a result, it is guaranteed to be correct.

In other words, functional programs can be broken up and mapped onto a parallel processor in any arbitrary manner, so we can attain the benefits of concurrent evaluation without the typical costs of partitioning and communication. The  $\lambda$ -calculus asset of cheap parallelism is precisely what motivates much of the continued interest in functional programming.

#### 2.1.4 Strengths and Limitations

There are a few practical problems involved when considering the  $\lambda$ -calculus as a notation that would be executed in a real or abstract machine. The size of  $\lambda$ -calculus programs increases compared to that of the original source program. Even when ground types and associated operations are included, the nameless nature of  $\lambda$ -calculus requires that function bodies be replicated wherever they are called. Even so,  $\lambda$ -calculus code expansion is not that much worse, symbol for symbol, than with imperative-style machine code on Von Neumann machines.

$\lambda$ -calculus programs consist of many very small-bodied functions, and this translates to an abundance of function calls, all of which are short. Aside from ground type operations, evaluating  $\lambda$ -calculus programs consists almost entirely of function calls. Qualitatively, this means that most effort is spent rearranging complex expressions simply to filter arguments "down" to where they are needed. In addition, the use of fixed-points for recursion is expensive, as each recursive call requires that the function be copied in its entirety.

The largest cost is the use of  $\beta$ -reduction to evaluate each function call, as it is inherently expensive. Substituting arguments requires a time-consuming search for variable names throughout the body of the  $\lambda$ -expression, which can be several thousand symbols at the start of a program.  $\beta$ -reduction is also susceptible to the "name-capture" problem [Pey87], which arises when one or more symbols in a substituted expression become erroneously bound to remaining parameters. As illustrated on the left in Figure 2.6 below.

| With capture                                            |              | Without capture                                                               |              |

|---------------------------------------------------------|--------------|-------------------------------------------------------------------------------|--------------|

| $(\lambda x.(\lambda y. + x y)) y 3$                    | $\checkmark$ | $(\lambda x.(\lambda y. + x \ y)) \ y \ 3$                                    | $\checkmark$ |

| $ \stackrel{\beta}{\implies} (\lambda y. + y \ y) \ 3 $ | !            | $\stackrel{\alpha}{\Longrightarrow} (\lambda x.(\lambda w. + x \ w)) \ w \ 3$ |              |

| $\stackrel{\beta}{\implies}$ +3 3                       | Х            | $\stackrel{\beta}{\implies} (\lambda w. + y \ w) \ 3$                         |              |

| $\implies 6$                                            | Χ            | $\stackrel{\beta}{\Longrightarrow}$ +y 3                                      | $\checkmark$ |

Figure 2.6: Name-Capture

The argument y is substituted for the locally free argument name x in the first  $\beta$ -reduction and has become bound to the local parameter y. It should remain a "free variable" at this level (although it may be bound by a surrounding expression). To prevent this name clash,  $\alpha$ -conversion is used to rename y prior to substitution, as shown on the right in Figure 2.6. Thus,  $\beta$ -reduction is made more expensive by having to detect name clashes and apply  $\alpha$ -conversion as needed. Performing this task over an entire program is very expensive in time and memory usage.

Of course, many of these problems may be reduced by an intelligent implementation of the evaluation methods. A machine architecture proposed by DeBruijn [DeB72] uses annotated variable names and an environment-lookup method to track the positions of argument symbols in the body of an expression, to avoid searching and quickly detect name clashes. Aiello and Prini [AP81] maintained expensive runtime variable scoping lists for each expression, and extensively applied  $\alpha$ -conversion to avoid name-capture. Both of these machines resorted to reincarnating information that the  $\lambda$ -calculus had originally abstracted out, and using more intelligent evaluation mechanisms than simple term-rewriting. However, the real problem is with the notation; the use of  $\beta$ -reduction, and the raw numbers of function calls must be avoided.