#### THE UNIVERSITY OF CALGARY

## **SECD:**

# The Design and Verification of a Functional Microprocessor

$\mathbf{B}\mathbf{Y}$

5

Brian T. Graham

A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

#### DEPARTMENT OF COMPUTER SCIENCE

CALGARY, ALBERTA June, 1990

© Brian T. Graham 1990

National Library of Canada Bibliothèque nationale du Canada

Service des thèses canadiennes

Canadian Theses Service

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-61962-7

# THE UNIVERSITY OF CALGARY FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled "SECD: The Design and Verification of a Functional Microprocessor" submitted by Brian Thomas Graham in partial fulfillment of the requirements for the degree of Master of Science.

CBit

Supervisor, Dr. G.M. Birtwistle Department of Computer Science

Dr. B.R. Gaines Department of Computer Science

Dr. L. Higham Department of Computer Science

Dr. J.W. Haslett Department of Electrical Engineering

Dr. S.J. Curry Bell Northern Research Ltd.

Date \_\_ 1990-06-20

### Abstract

The subject of this thesis is a silicon implementation of Landin's SECD machine. The starting point was an abstract specification defined by instruction transitions. Work completed includes the evolution of the design by transformation from the abstract specifications down to microcode, laying out the design in silicon, and the formal verification of its functional correctness using the HOL proof assistant.

A top level specification for the SECD system as well as an implementation level definition are generated using the HOL system. The intended operating conditions are formally defined, and installed as constraints in a machine-assisted proof of correctness stating that the computation effected by the implementation model meets the specification. The specification raises issues of the representation of S-expression data structures with destructive operation on shared structures. A solution which defines an abstract memory data type which can embed the data structures is used in the formal specification. Several issues related to the representation of temporal aspects of the chip function are analysed.

The SECD chip is one of the most complex devices subjected to formal verification to date, and is unique in combining the design and layout with the formal specification and verification of an integrated circuit. The problem size prevents presentation of either the specification or proof in their entirety, however techniques used to help manage the inherent complexity are presented in conjunction with a representative sampling of the specifications and proofs.

## Acknowledgements

I have been assisted by many people throughout the years of work on this project. My greatest debt is to my supervisor, Graham Birtwistle, who has patiently supported and guided my work, and whose unwavering confidence has been a vital encouragement to strive for greater challenges. He has been instrumental in making this lab a very stimulating environment in which to work.

I owe a particular debt of gratitude to Tom Melham and Inder Dhingra, without whose gracious assistance with HOL I could not have succeeded. Thanks also to Ian Mason, whose work on the Semantics of Lisp provided key ideas for the formal SECD specification.

Many thanks to the past and present members of the VLSI and Verification group at the University of Calgary who have always been a pleasure to work with, including the original SECD team of Mark Brinsmead, Jeff Joyce, Wallace Kroeker, Breen Liblong, and Simon Williams, and past and present colleagues Tom Fukushima, Ganesh Gopalakrishnan, Mike Hermann, Rajagopal Nagarajan, Paliath Narendran, Cameron Patterson, Todd Simpson, Konrad Slind, Sue Stodart, Glen Stone, and Mark Williams.

This work could not have been completed without the support of the Alberta Microelectronics Centre, NSERC, CMC, and the Communications Research Establishment.

I especially thank my parents for their support and encouragement that gave me the opportunity to pursue this goal. Last but hardly least, I would like to thank my wife Jean for her support and patience over the years, and Timothy and Christopher, who have been a very special part of my life.

# Contents

5

| A  | proval Page                                                                                                                                                                                                                                                                                                                                 | ii                                                 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Ał | stract                                                                                                                                                                                                                                                                                                                                      | iii                                                |

| Ad | knowledgements                                                                                                                                                                                                                                                                                                                              | iv                                                 |

| Co | ntents                                                                                                                                                                                                                                                                                                                                      | $\mathbf{v}$                                       |

| Li | t of Tables                                                                                                                                                                                                                                                                                                                                 | viii                                               |

| Li | t of Figures                                                                                                                                                                                                                                                                                                                                | ix                                                 |

| 1  | Introduction1.1 The Impetus for Formal Methods1.2 Formal Methods and Verification1.3 The Nature of this Research1.4 The Structure of the Thesis                                                                                                                                                                                             | <b>3</b><br>3<br>5<br>7<br>10                      |

| 2  | Hardware Verification and Formal Methods2.1Why Higher Order Logic2.2A Brief Introduction to HOL                                                                                                                                                                                                                                             | <b>11</b><br>12<br>13                              |

| 3  | LispKit and the SECD Architecture3.1 The Syntax of LispKit3.2 The Interpretation of LispKit3.3 SECD Architecture3.4 Compiling LispKit to SECD Machine Code3.5 Summary                                                                                                                                                                       | 17<br>18<br>21<br>30<br>35<br>39                   |

| 4  | SECD Architecture: Silicon Synthesis         4.1 Project Context         4.2 Levels of the Design         4.3 External Architecture         4.3.1 Abstract Machine         4.3.2 Abstract System: the First Refinement         4.3.3 The Top FSM Level         4.4 Internal Architecture         4.4.1 The Abstract Register Transfer Level | 40<br>41<br>43<br>43<br>43<br>44<br>46<br>48<br>48 |

|   |     | 4.4.2 The Concrete Register Transfer Level                                                                                                                    |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.4.3 The Mossim Level                                                                                                                                        |

|   |     | 4.4.3.1 Memory Elements and Clocking                                                                                                                          |

|   |     | 4.4.3.2 Control Unit                                                                                                                                          |

|   |     | 4.4.3.3 Datapath                                                                                                                                              |

|   |     | 4.4.4 Layout                                                                                                                                                  |

|   |     | 4.4.4.1 Floorplanning                                                                                                                                         |

|   |     | 4.4.4.2 Design Guidelines                                                                                                                                     |

|   |     | 4.4.4.3 Shift Registers                                                                                                                                       |

|   |     | 4.4.4.4 Padframe                                                                                                                                              |

|   | 4.5 | Summary and Status                                                                                                                                            |

| 5 | For | mal Specification of SECD 71                                                                                                                                  |

|   | 5.1 | Modelling Hardware                                                                                                                                            |

|   | 5.2 | The Top Level Specification                                                                                                                                   |

|   | 5.3 | The Low Level Definition                                                                                                                                      |

|   | 5.4 | Register Transfer Level Specification                                                                                                                         |

|   |     | 5.4.1 Temporal representation                                                                                                                                 |

|   |     | 5.4.2 The Datapath Specification                                                                                                                              |

|   |     | 5.4.3 The Control Unit Specification                                                                                                                          |

|   |     | 5.4.4 The Padframe                                                                                                                                            |

|   |     | 5.4.5 Composing the Whole                                                                                                                                     |

|   | 5.5 | Relating the Levels                                                                                                                                           |

|   |     | 5.5.1 Memory Abstraction                                                                                                                                      |

|   |     | 5.5.2 Temporal Abstraction                                                                                                                                    |

|   | 5.6 | Summary                                                                                                                                                       |

| 6 | Ver | ification of the SECD Design 100                                                                                                                              |

|   | 6.1 | Constraints                                                                                                                                                   |

|   | 6.2 | Structure of the proof $\ldots \ldots \ldots$ |

|   | 6.3 | Unfolding the System Definition                                                                                                                               |

|   | 6.4 | Phase Level: Effect of Each Microinstruction                                                                                                                  |

|   | 6.5 | Microprogramming Level: Symbolic Execution                                                                                                                    |

|   |     | 6.5.1 The initial transition                                                                                                                                  |

|   |     | 6.5.2 The general approach: LDF                                                                                                                               |

|   |     | 6.5.3 Proving the complex sequences                                                                                                                           |

|   | 6.6 | Liveness                                                                                                                                                      |

|   | 6.7 | Relating the Computations over Abstraction                                                                                                                    |

|   | 6.8 | Summary                                                                                                                                                       |

|   |     |                                                                                                                                                               |

.

| 7 | Con | clusions                              | 139  |

|---|-----|---------------------------------------|------|

|   | 7.1 | What has been accomplished            | 139  |

|   | 7.2 | Putting the proof result into context | 142  |

|   | 7.3 | Retrospective Improvements            | 145  |

|   | 7.4 | Hardware Verification: the future     | 147  |

| _ |     |                                       | - 40 |

#### References

.

,

.

.

# List of Tables

| 3.1                        | Well Formed LispKit Expressions                                                                                                                                                | 19                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.2                        | LispKit Interpreter Written in Franz Lisp                                                                                                                                      | 22                   |

| 3.3                        | Machine Instruction Definitions                                                                                                                                                | 32                   |

| <b>3.4</b>                 | SECD Machine Code Generated for Well-Formed Expressions                                                                                                                        | 36                   |

| 3.5                        | LispKit to SECD Compiler Written in LispKit                                                                                                                                    | 38                   |

| $4.1 \\ 4.2 \\ 4.3 \\ 4.4$ | Initial RTL Microcode Sequence for AP InstructionIntermediate RTL Microcode Sequence for AP InstructionFinal Microcode Sequence for AP InstructionLevels of Definition Summary | 51<br>55<br>57<br>70 |

| 5.1                        | Primitive Operations on Abstract Memory Data Type                                                                                                                              | 76                   |

| 7.1                        | Comparison of Viper and SECD proofs                                                                                                                                            | 142                  |

4

# List of Figures

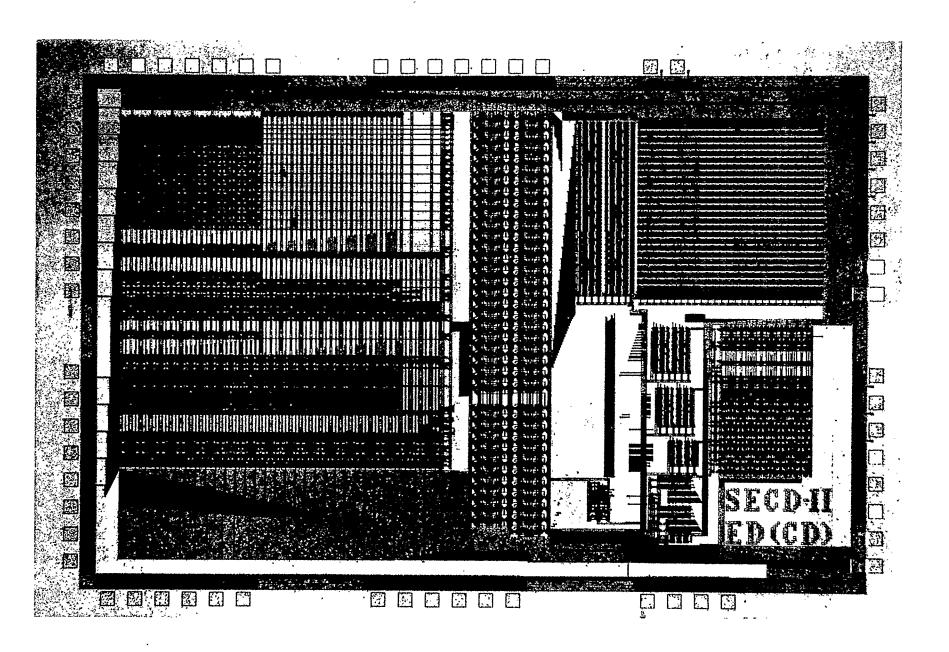

| 0.1  | The SECD Chip: Microphotograph of Second Version                                                                 | 1   |

|------|------------------------------------------------------------------------------------------------------------------|-----|

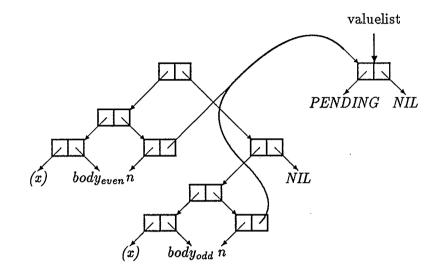

| 3.1  | Valuelist Structure Before Destructive Operation                                                                 | 29  |

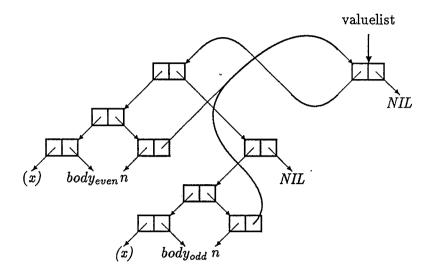

| 3.2  | Circular Valuelist Structure After Destructive Operation                                                         | 30  |

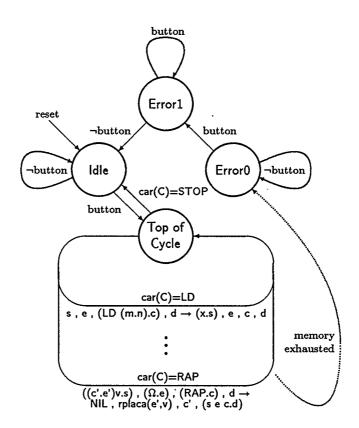

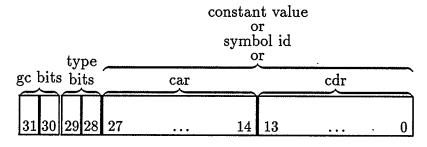

| 4.1  | Top Level Finite State Machine View of SECD                                                                      | 46  |

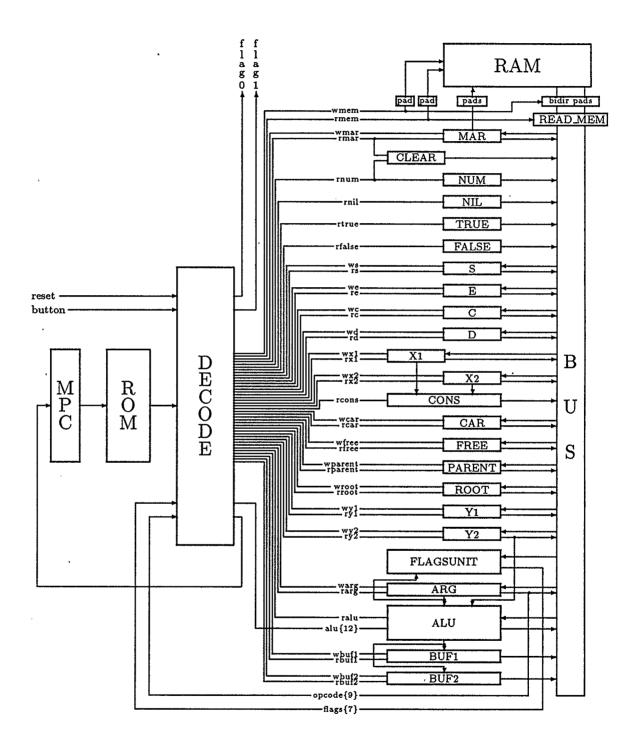

| 4.2  | Register Transfer Level View of SECD Machine                                                                     | 53  |

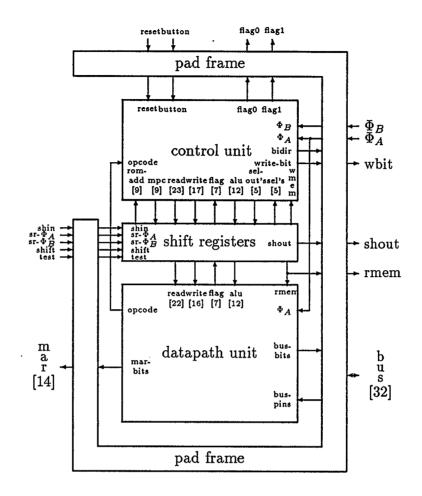

| 4.3  | SECD Chip Major Subcomponents                                                                                    | 68  |

| 5.1  | Transition for LDF Instruction                                                                                   | 77  |

| 5.2  | Top Level Specification                                                                                          | 78  |

| 5.3  | Control Unit and Datapath Register Schematics and Definitions                                                    | 82  |

| 5.4  | Relating low and RTL times                                                                                       | 83  |

| 5.5  | Definition of the DP Component                                                                                   | 89  |

| 5.6  | Definition of the CU Component                                                                                   | 93  |

| 5.7  | Definition of the PF Component                                                                                   | 94  |

| 5.8  | Definition of the SECD SYS Component                                                                             | 95  |

| 5.9  | Temporal Abstraction Function Definitions                                                                        | 96  |

| 6.1  | $RTL \supset top level goal \ldots \ldots$ | 107 |

| 6.2  | Base_thm: the RTL definition simplified                                                                          | 111 |

| 6.3  | Theorem for execution of microcode instruction at address 97                                                     | 113 |

| 6.4  | Microprogramming level theorems for LDF instruction                                                              | 120 |

| 6.5  | Microprogramming level theorems for consx1x2 subroutine                                                          | 122 |

| 6.6  | Decision Tree for Recursive Microprogramming Level Proof Function                                                | 123 |

| 6.7  | Theorems for n iterations through loop1                                                                          |     |

| 6.8  | 1 0 0                                                                                                            |     |

| 6.9  | Microprogramming level Next theorem for LD instruction                                                           |     |

| 6.10 | Abstract Memory Theorems                                                                                         |     |

| 6.11 | The Correctness result for the LDF instruction                                                                   | 134 |

Figure 0.1: The SECD Chip: Microphotograph of Second Version

# Chapter 1

### Introduction

Great strides in the technology of fabrication of physical devices in integrated circuits have created a gap between production capability and the ability to manage the complexity that such devices invite. These advances have also extended the range of integrated circuit applications, so that today any device requiring a control mechanism will almost inevitably utilize integrated circuits. The future promises continued growth in both capability of discrete components as well as the range and complexity of tasks to which they are applied. Mounting evidence of failures of integrated circuit based systems and resulting costs has focussed attention on methods of increasing their reliability. In this context, the use of formal methods has been advanced as a means of dealing with one aspect of system reliability, that of guaranteeing functional correctness of a design.

#### **1.1** The Impetus for Formal Methods

As the smallest feature size of integrated circuit devices drops, the number of transistors that can be integrated into a single design increases. Current microprocessor designs have in excess of one million transistors on a single chip<sup>1</sup>. Quite apart from simple transistor count, the devices are themselves increasingly complex and the development of massively parallel systems promises that this trend will continue. Reasoning about things of such complexity demands a high degree of formalism in

<sup>&</sup>lt;sup>1</sup>The Intel 80486 with 1.1 million and the Motorola 68040 with 1.2 million transistors were expected to be available in mid 1990, but when the 80486 was marketed in late 1989, production was suspended when an error was discovered in the floating point unit despite "hundreds of thousands of hours" of testing.

order to ensure the behaviour of the device is understood. The informal methods used for design in the past are not always adequate for today's designs.

The decrease in cost coupled with the increasing functionality of integrated circuit devices has led to a rapid growth in their range of application. Today we find them in such diverse locations as the control systems of aircraft, automobiles, ships, and trains; medical devices such as pacemakers and artificial limbs; imbedded within "smart cards" for banking, medical records, and other applications; industrial control systems including nuclear generating stations; remote sensing systems on pipelines; as well as assorted military systems.

The potential for a flawed design to cause economic disaster or loss of life is very real. Numerous documented cases of risk and actual loss connected with computer systems and related technology have appeared in the pages of the ACM SIGSOFT quarterly, Software Engineering Notes, spread over many issues. Peter Neumann has produced a summary of these cases with over 500 entries [Neu89]. Loss and risk categories include loss of life, potentially life-critical, loss of resources, and security/privacy/integrity problems. Behaviours to which the losses are attributed include intentional misuse; accidental misuse; misinterpretation/confusion at a manmachine interface; flaws in system concept, requirements, design, or implementation; improper maintenance/upgrade; and hardware malfunction attributable to system deficiencies, electronic or other interference, the physical environment, acts of God, etc.

The traditional method of ensuring the correctness of designs is simulation. This entails defining a model of the behaviour of the primitive components of the design, and exhaustively determining that the behaviour for each possible input condition was as desired. As the number of cases is exponential in the number of input bits for combinational circuitry, the increasing device size has made total coverage simulation too time consuming to be acceptable. Devices which maintain internal state are far

#### CHAPTER 1.

more difficult (to the point of impossible) to simulate exhaustively for each state and each input condition. Thus products are being produced today without a desirable level of assurance of behaviour over the range of all input conditions.

Formal methods, entailing the description of and reasoning about systems within a formal logic, are being applied to all levels of systems design, including both software and hardware components, in an effort:

... to increase the quality of the systems developed and to increase our confidence that the systems will behave in a predictable manner.<sup>2</sup>

#### **1.2** Formal Methods and Verification

Formal methods generally involve representing an implementation and a specification within a formal theory. Verification compares the representations within the formal theory, reasoning that under particular constraints the implementation ensures the specification is (or is not) met.

For application to hardware, a circuit is represented in terms of primitive components, such as primitive logic gates, with levels of electrical potential abstracted to a limited number of discrete values. A primitive logic gate is expressed as a relation between its inputs and outputs. In the case of memory elements, the relation includes its state as well. Specifications are often defined in terms of more abstract data objects, in order to describe the complex behaviour in a way that may be examined for agreement with what we understand is desired. Verification involves proving that, under stated constraints representing assumptions about the operating conditions of the circuit for example, the implementation guarantees the behaviour described by the specification over all inputs and states. By using a mechanized proof system, we gain a higher degree of confidence that the proofs are indeed valid.

<sup>&</sup>lt;sup>2</sup>Dan Craigen in [Cra89].

The use of verification must be understood in terms of its practical limitations. One obvious limitation is the accuracy of the model chosen for primitive components. As an example, consider possible transistor models. The transistor can be defined by a simple switch model, where the transistor is either on or off, depending on the gate input. This model is appropriate for CMOS, where signals are guaranteed to be strong, but will not accurately capture the behaviour of pullup transistors or transistors with weak gate signals, and could lead to an incorrect conclusion. On the other extreme, a transistor model could be as complex as the one used in SPICE. This model will give us a much higher degree of accuracy, but complexity of the proof becomes simply unmanageable for anything other than a trivial circuit. Clearly, one must choose a model appropriate for the subject, and make explicit the assumptions under which the model can capture the subject behaviour. The exceedingly complex behaviour of transistors suggests that a higher level view of the design would be more suitable for modelling. The choice of primitive logic gates and latches as the lowest level components used to model fully complementary CMOS circuits combines simplicity with accurate capture of behaviour, given the assumption that all signals have enough time to settle to stable values. Full simulation of the primitive components using such tools as SPICE can establish the detailed operating constraints under which the model will be valid.

Aside from representing primitive component behaviours, the circuit connections must themselves be correctly captured in the model. There is a need to integrate the formal model with design tools to ensure that this correspondence is maintained.

Production of a correct design requires both that the design itself meets the specification of the desired behaviour, and the desired design is actually produced in the chip. The former is the realm of verification, while the latter is in the realm of testing of the product. While the two realms can be viewed as distinct, the formalism of the design process may well offer insight in determining an appropriate test suite

for the design. Formal methods could also be used to reason about the behaviour of an assembly of exhaustively tested subcomponents.

There is necessarily a gap between the lowest level of representation and the physical hardware device, just as geometry only describes abstractions of physical objects. At the other end of the spectrum, the specification is a representation of some designer's intention, which cannot be entirely captured within a formal logic. Nor can we ever prove the validity of the specification as a representation of these intentions. These gaps are not unique to formal methods, but their presence defines the limits of what formal methods can contribute to assurance of correct design. Thus the term "partial" should be assumed whenever the words "verification" or "correctness" appear in this thesis.

#### **1.3** The Nature of this Research

The goal of this research was to examine the application of formal methods to the design of complex integrated circuits. For this purpose, a microprocessor implementation of the functional SECD architecture, first described by Landin [Lan64] and elaborated by Henderson [Hen80], was designed, specified, and partially verified.

This work was part of a larger project on the use of formal methods in systems design at the University of Calgary. The design of hardware is only one part of producing reliable systems. It is equally important to assure the correctness of the software which will run on the system, and most important of all is the interface between the two. It is most desirable if a common formalism can be used to express both. At Calgary, the VLSI group chose to restrict its attention to functional languages running on functional architectures. It is not that the hardware is any easier to verify, but proofs of program correctness certainly are, as is the verification of the translation process. The key points in the approach are:

- 1. Use a functional programming language. Since they are based upon the  $\lambda$ calculus they are expressive. They are also very succinct and amenable to

proof.

- 2. Use a sugared variant of  $\lambda$  as the compiler target language. Since functional constructs are easy to express in terms of  $\lambda$ , it is relatively straightforward to express the semantics of the translation scheme and to prove its correctness.

- 3. Convert from  $\lambda$  to machine code. This step is relatively trivial if we choose a functional architecture, e.g. SECD which supports  $\lambda$ , or a graph reduction machine which will execute combinators.

- 4. Run the code on verified hardware.

Choosing  $\lambda$  as the common thread considerably simplifies all the above step-by-step transitions. In particular, it is possible to verify software and hardware with the same proof checker, to adopt a single proof style, and to reuse proofs.

The work is part of a long term effort in verification that started in 1985. The VLSI group chose to work with Lispkit [Hen80, HJJ83a, HJJ83b, SBGH89], and Henderson's version of Landin's abstract SECD machine [Hen80]. [Bur75, FH88, Hen80, HBGS89] explain the workings of varieties of eager and lazy SECD machines. [FH88] sketches Plotkin's [Plo75] proof of correctness of an eager SECD machine. Thus the choice of SECD was deliberate — there was much work to build on. To date the project group has

- designed, fabricated and is presently testing version II of the chip,

- constructed a rig and associated software, including compilers from Lispkit to SECD so that we can download Lispkit programs and run them on SECD,

- completed a (hand) proof that the abstract SECD machine executes Lispkit programs correctly (see [SGB89] for a full version of the proof), and

#### CHAPTER 1.

• substantially completed a machine assisted proof in HOL [Gor85, Gor88a, Gor89] of the SECD design, see [GWS89] and [BGS+89].

The formalism chosen for this study is a higher-order logic, which has been implemented in the HOL proof assistant by Mike Gordon of Cambridge University. The use of a higher-order logic permits specifications to be succinct and often elegant, making it easier to assure through visual inspection that the specification captures the intention. The lengthy period of time required to become adept at use of this system, combined with the availability of experienced circuit designers at the start of the project, resulted in a reversal of the intended project execution, with the chip design completed before the formal specification was prepared. This has shifted attention from the impact of formal methods on the design process to methods of specifying and verifying complex designs. Only after the fact can we speculate how revelations arising from the formal work could have contributed to a better and more reliable design.

My thesis research focuses on several aspects of the larger project:

- Development of a working integrated circuit design from a highly abstract description. The design is developed through several increasingly detailed models.

- The design of the system specification within a formal logic.

- Imbedding a model of the implementation within the same logic.

- Making the assumed operating conditions explicit within the logic.

- The proof of correctness that under the given constraints, the computation effected by the implementation matches the specified behaviour.

This work has several unique properties. The integration of circuit design and specification/verification in this project has led to a close resemblance between the formal specifications and the informal models that are used in the design process.

The choice of a functional architecture subject provided increased complexity in defining the effect of machine instruction execution, and required the representation of abstract S-expression data structures, so that the specification operates well above the level of *bits*.

One of the most significant aspects of the project has been the size and complexity of the subject system. Because of the complexity of the SECD chip, it is not possible within the scope of a thesis to give more than an outline of most of its component specifications and the proofs: they are simply too large to be included in their entirety. All we can do is give a flavour of the work. Despite this incompleteness, the critical concepts in designing the specification are presented in detail, and the description of the proof strategy is augmented with representative samples of results, and quite detailed descriptions of the methodology. The impact of the project size, particularly on proof management, is a recurring theme. The huge size of the proof meant that many original proof management techniques had to be developed. The achievement of the proof alone stands as a significant result. The SECD chip is one of the largest examples to date in the field of hardware verification.

#### 1.4 The Structure of the Thesis

Chapter 2 describes other work in the field of hardware verification, and describes the HOL system which was used for the formal definition and verification in this study. In chapter 3, the SECD architecture is described, showing how it can support the execution of a Lisp-like high level language. Chapter 4 describes the evolution of the SECD design to the physical layout stage. A formal specification for the SECD system is defined in Chapter 5, as well as a lower level view closely related to the layout. The proof of correctness relating two levels is described in Chapter 6. The final chapter comprises conclusions and continuing and future work.

10

# Chapter 2

## Hardware Verification and Formal Methods

The first significant achievement in hardware verification was Gordon's machine assisted proof of the correctness of a small microprocessor with a microcoded control unit [Gor83b]. This 8 instruction machine was specified at the register transfer level, and the correctness of this model meeting a higher level specification was proved. This work was done in the LCF-LSM system [Gor83a], a predecessor of the HOL system.

Warren Hunt specified and proved the correctness of the FM8501 microprocessor [Hun85], a traditional von Neumann architecture comparable to a PDP-11 in complexity. The specification and verification was done in the first-order Boyer-Moore logic, and proven using the associated automated theorem prover.

Jeff Joyce designed the TAMARACK microprocessor based on Gordon's original example, specified and verified it in HOL [Joy88]. He has extended this work to the transistor level [Joy89b], added a configurable memory timing interface and parameterized the specification datatypes and operations [Joy89a], and has since verified the correctness of a TINY compiler generating code for TAMARACK [Joy89c]. TINY (see chapter 3 in [Gor79]) is a toy imperative language which includes assignments, conditionals, and while statements.

Perhaps the largest single verification effort to date has been the VIPER microprocessor by RSRE [Cul88] and Cohn [Coh88, Coh89b]. This work is distinguished by the fact that formal methods were applied to a commercially available product, and the considerably larger size and complexity of the device and verification effort compared to the previous examples. The chip is hard wired rather than microcode controlled, and was defined at roughly a register transfer level with detailed implementation of data operations, at a major state level which described the operation of the chip in terms of a graph traversal, and at a more abstract top level. The correspondence of the two upper levels was fully verified, but the extension to the lowest of the three levels is incomplete, although a significant analysis of the implementation through proof techniques was accomplished.

Other significant efforts include the flooding sink local area network broadcast message eliminator by Melham [BJL+86], the Sobel image processing chip by Narendran and Stillman [NS89], and the Cayuga microprocessor by Sekar and Srivas [SS89]. Dhingra [Dhi88] has formalized and validated CLIC, an integrated circuit design style, in HOL.

Significant work at Computational Logic followed from Warren Hunt's work on the FM8501 described above. Bevier [Bev87] has gone on to implement and verify a multi-tasking operating system kernel for a 16-bit von Neumann architecture which includes process scheduling, response to error conditions, message passing primitives, and character I/O. Moore [Moo88] has specified the PITON language and mechanically verified its implementation on the FM8502 architecture via a compiler, assembler and linker. PITON is an assembly language designed for verified applications and includes recursive subroutine support, stack based parameter passing, and several abstract data types. Finally Young [You88] has mechanically verified a code generator for Gypsy 2.05 down to PITON.

### 2.1 Why Higher Order Logic

The choice of the HOL system and the use of a higher-order logic offers an expressive power that other formalisms lack. Clearly this is at some cost, as proof automation is an even more difficult problem than for a first-order logic such as the one used by

#### CHAPTER 2.

Boyer and Moore [BM79]. The expressive power is essential to capture a wide range of views of a device, and to be able to relate them in understandable ways. Without this power of expression, both the specifications and the meaning of the correctness proofs may become too obscure to be useful.

The HOL system is a very widely used proof assistant in hardware verification. Not only has it been proven a reliable tool, but there is a growing body of worked examples and a large and growing library of supporting work, including extensive sets of theorems characterising defined datatypes such as integers and bit strings. Additionally, assistance in learning HOL was readily and well provided by colleagues at Cambridge, for which the author is grateful.

#### 2.2 A Brief Introduction to HOL

This chapter closes with a brief look at the HOL system used for the formal representation and verification of the SECD system. The following owes much of its organization to the example of [Coh89b]. A full description is beyond the scope of this work, and the reader is referred to [Cam89a, Cam89b, Cam89c] for full documentation.

HOL is a machine implementation of a conventional higher-order logic in which problems can be expressed, and interfaced to the programming language ML in which proof procedures and strategies can be encoded. The type discipline of ML ensures that the only way to creating objects of type *thm* is by the application of inference rules to other theorems or axioms. Theorems are identified by the turnstyle symbol  $\vdash$ , with assumptions to the left, and conclusion to the right.

New types, constants and axioms can be introduced by the user, and are organised in logical *theories*. Proved theorems may be saved in and retrieved from the theories, which are organized into hierarchies in which types, constants, axioms, and theorems are inherited from ancestor theories.

The HOL system uses the ASCII characters  $\tilde{}, / \backslash, \vee, ==>, <=>, !, ?, @, and \ to represent the logical symbols <math>\neg, \land, \lor, \supset, \equiv, \forall, \exists, \epsilon \text{ and } \lambda$  respectively. Throughout this thesis, the symbols  $\tilde{}, \backslash, / \backslash$  and  $\backslash /$  will be replaced by the conventonal logical symbols. A *term* of higher-order logic can be one of the following:

- A variable;

- A constant, including natural numbers, the boolean values T and F, etc;

- A function application of the form t1 t2;

- An abstraction of the form  $\lambda x.t$ ;

- A negation of the form  $\neg t$ ;

- A conjunction of the form  $t1 \wedge t2$ ;

- A disjunction of the form  $t1 \lor t2$ ;

- An equality of the form t1 = t2;

- An implication of the form t1 ==> t2;

- A universal quantification of the form !x.t;

- An existential quantification of the form ?x.t;

- An ε-term of the form Qx.t,<sup>1</sup> expressing some arbitrary value x such that the predicate t is true;

- A conditional of the form t=>t1|t2, expressing if t then t1 else t2;

- A local declaration of the form let x = t1 in t2;

<sup>&</sup>lt;sup>1</sup>Q is a higher-order version of Hilbert's choice operator.

- A list of the form [t1; t2; t3;...;tn] where all elements have the same type;

- A pair of the form (t1,t2), where t1 and t2 may each be of any type.

Double quotes distinguish HOL terms in the ML interface, and a typewriter font will be used for HOL terms consistently throughout this thesis. The ML antiquotation operator ^ permits ML identifiers bound to HOL terms to be included within HOL terms. ML comments are enclosed within % characters.

All terms in HOL have a *type*. The expression t:ty means t has type ty. Builtin types include :bool and :num for *booleans* and *natural numbers*. Three type operators are ->, +, and #, for describing function types, sum types, and product types respectively. Types may be parameterized, for example :(bool)list is the type of *boolean* lists. Polymorphism is allowed, and type variables are typically \*, \*\*, and so on. Nonempty new types may also be defined by mapping to an existing type within the logic. Types will consistently be shown preceded by a colon.

Many constants are built into the HOL system, including the boolean constants and natural numbers, arithmetic operators +,-,\*,<,<=,>,>=, DIV, MOD, EXP, SUC, and PRE, the list operations CONS, HD and TL, and FST and SND selectors on pairs to name some of the more commonly used ones. The reader's attention is particularly directed to the infix function composition operator o, which is used repeatedly in abstraction functions.

There are two general approaches to proof within HOL: forward and backward. Forward proof works by applying inference rules to existing theorems and axioms to derive a desired result in the form of a new theorem. Where to start on a large complex proof is problematic, and managing the many branches involved is oftentimes exceedingly difficult. An alternative methodology, backward proof, starts with a statement of the theorem you would like proved (a goal), which the user incrementally splits into smaller, more manageable subgoals. The HOL system manages the state of the proof on a goal stack, and when each subgoal is reduced to a theorem, it assembles the entire proof and returns the desired theorem. This methodology does not provide a distinct means of construction of *thm* type objects, rather it allows the user to generate the proof, which will use the same inference rules as the *forward* proof methodology with a top-down approach, leaving the system to manage the details. Both methods have advantages and both are used in this work. The choice of *forward* or *backward* proof will often be an important consideration in the methodology.

The HOL notation will be used for the formal definition of the SECD system, but first is a description of the abstract SECD architecture, and the development of the SECD chip design.

## Chapter 3

### LispKit and the SECD Architecture

This chapter introduces LispKit, a high-level programming language, defines the abstract SECD architecture, and shows how the architecture can support execution of programs written in the high-level language. The definitions of LispKit and SECD given by Henderson [Hen80] are used. Henderson also defines a LispKit interpreter, and a LispKit to SECD compiler.

LispKit is a pure functional subset of the Lisp language. A pure functional subset means that LispKit has no destructive assignment operation, so that the value of an expression is uniquely determined by the value of its constituent parts, and identical expressions always have the same value. S-expressions are defined, and then a syntax for LispKit is given. This is followed by an informal semantics for the language, defined within Franz Lisp as an interpreting function. Issues fundamental to supporting the language with a hardware system such as bindings and representation of function-valued objects are discussed.

The SECD machine architecture is described by its machine instructions and state transitions effected by each, giving a semantics for the machine language. Following this, a translation schema for well-formed LispKit expressions into SECD machine code is the basis for a LispKit compiler, and defines an operational semantics for LispKit.

To ease distinguishing between the different languages presented, different fonts will be used: Sans Serif Italics for LispKit expressions, Roman Italics for Franz Lisp expressions, and Sans Serif for SECD machine code expressions.

#### 3.1 The Syntax of LispKit

Fundamental to the Lisp programming world is the class of objects known as symbolic expressions, or S-expressions for short. These are defined recursively as:

S-expression ::= atom | ( S-expression . S-expression )

Atoms are of two types: numeric and symbolic. A numeric atom is a possibly signed sequence of digits, which is taken as representing a decimal integer. Symbolic atoms,  $\cdot$  either constants or variables, appear as a series of letters or digits or other characters, beginning with a character. There are three special symbolic atoms: *NIL*, *T*, and *F*, which are symbolic constants and have a particular meaning attached to them.

A dotted pair is the result of a Lisp cons operation on two S-expressions. If a and b are S-expressions, then (cons a b) produces a dotted pair (a . b). The dot notation used here is often replaced by the list form where possible. The rules for transforming from dot to list notation are simply:

- (a. NIL) may be written as (a)

- (a. (b)) may be written as (a b)

where a and b may be any S-expressions. NIL is interpreted as the empty list.

LispKit provides sixteen primitive operators which are reserved symbolic constants. In order to distinguish constants from variables, constants are represented by the dotted pair whose first component is the QUOTE operator. Structural operators are CONS, CAR, CDR, and ATOM, which perform the standard list operations common to all Lisp variants. Arithmetic operators include ADD, SUB, MUL, DIV and REM. The relational operators are limited to EQ and LEQ. In addition, there is the conditional operator IF, the  $\lambda$  operator LAMBDA, used for defining functions, and two block defining operators, LET and LETREC, the latter being used for recursive bindings.

| x                                          | variable               |

|--------------------------------------------|------------------------|

| (QUOTE s)                                  | constant               |

| $(ADD e_1 e_2)$                            |                        |

| $(SUB e_1 e_2)$                            |                        |

| $(MUL e_1 e_2)$                            | arithmetic expressions |

| $(DIV e_1 e_2)$                            | -                      |

| $(REM e_1 e_2)$                            |                        |

| $(EQ e_1 e_2)$                             |                        |

| $(LEQ e_1 e_2)$                            | relational expressions |

| (CAR e)                                    |                        |

| (CDR e)                                    |                        |

| $(CONS e_1 e_2)$                           | structural expressions |

| (ATOM e)                                   |                        |

| $(IF e_1 e_2 e_3)$                         | conditional form       |

| $(LAMBDA (x_1 x_n) e)$                     |                        |

|                                            | $\lambda$ -expression  |

| $(f e_1 \ldots e_k)$                       | function call          |

| $(LET \ e \ (x_1.e_1) \dots (x_k.e_k))$    | simple block           |

| $(LETREC \ e \ (x_1.e_1) \dots (x_k.e_k))$ | recursive block        |

|                                            |                        |

| where $e, e_i$ are well-formed exp         | pressions,             |

| $x$ , $x_i$ are symbolic atoms             | s (variables),         |

| s is any S-expression,                     |                        |

| f is a $\lambda$ -expression.              |                        |

Well-formed expressions in LispKit form a subset of the set of S-expressions, as determined by the derivation rules of Table 3.1.

Table 3.1: Well Formed LispKit Expressions

• Constants may be other than just numbers, as the restriction to S-expressions implies. However, all constants must be preceded by the QUOTE operator. The arithmetic and relational operators are all binary operators, unlike those in many variants of Lisp. The structural expressions are typical of most Lisps.

Y

- The conditional form takes three arguments, the first of which is the conditional expression. The second argument is evaluated only if the conditional expression evaluates to *T*, otherwise the third is evaluated.

- Lambda expressions are used for defining functions of one or more arguments. A list of λ-bound variables is followed by an expression which will usually include all occurrences of these variables.

- Function calls follow the form of primitive operators, with a function-valued expression being the first item in a list, followed by the values to be bound to its local variables.

- Blocks are another means of creating local bindings. The expression containing the bound variables follows immediately after the *LET* operator, followed by any number of dotted pairs of variables and expressions to be bound to the variables. The only difference between the *LET* and the *LETREC* is that the expressions to be bound to the variables in the *LETREC* may include (recursive) references to any of the bound variables, while in a *LET* they do not reference any of the locally bound variables. We shall see, in fact, that the *LET* form is unnecessary, as it is equivalent to the function call of a *LAMBDA* expression. The *LETREC*, however, is needed to define recursive functions. Furthermore, each expression  $e_i$  bound to a variable within a *LETREC* must evaluate to a function-valued object. The meaning of a function-valued object will become clear when the interpretation of LispKit is discussed below. This restriction eliminates meaningless expressions such as: (*LETREC* x (x ADD (QUOTE 1) x)) wherein an attempt is made to define x as its own successor.

Despite the derivation rules above, those expressions which will give rise to meaningful computations have not as yet been precisely defined. For the most part, the primitive operators, as well as any functions we may define, are partial. For example, (ADD (QUOTE 2) (QUOTE (A B C))) is not meaningful in LispKit, because ADD requires integer-valued arguments. Similarly, (CAR (QUOTE NIL)) is not meaningful, since the CAR operation is only defined on dotted pairs. For a complete denotational semantics of LispKit see [SGB89].

#### 3.2 The Interpretation of LispKit

A full interpreter for the LispKit language adapted from [Hen80] to Franz Lisp is given in Table 3.2. A brief description of its more interesting features follows. Two sample programs give a taste of the language in use.

Bindings of variables within LispKit are represented using the concept of contexts. A context consists of a set of bindings that associate variables with values, implemented using corresponding lists of variable names and values. The value of a variable is the value located in the corresponding position in the valuelist to the location of the variable in the namelist, with the added restriction that if the variable occurs more than once, the location closest to the front of the list is used. This permits new bindings to override existing bindings within a context. For example, the namelist and valuelist:

namelist: ((x y) (z x))

valuelist: ((1 3) (5 NIL))

represent the bindings:  $x \leftrightarrow 1$ ,  $y \leftrightarrow 3$ ,  $z \leftrightarrow 5$ . The second occurrence of x is rendered inaccessible in this example. This environment could have been generated by a LispKit program of the form:

| (def EVAL                                                                                                                                                          |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| (lambda (e n v))                                                                                                                                                   |             |

| (if (atom e)                                                                                                                                                       | ; variable  |

| (assoc é n v)                                                                                                                                                      | ,           |

| (let ((key (car e)))                                                                                                                                               |             |

| (if (eq key (quote QUOTE))                                                                                                                                         | ; constant  |

| (let ((const (cadr e)))                                                                                                                                            | ,           |

| (if (eq const 'NIL)                                                                                                                                                |             |

| nil                                                                                                                                                                |             |

| (if (eq const 'TRUE)                                                                                                                                               |             |

| t                                                                                                                                                                  |             |

| (if (eq const 'FALSE) nil const))))                                                                                                                                |             |

| (if (eq key (quote ADD)) (+ (EVAL (cadr e) n v) (EVAL (caddr e) n v))                                                                                              |             |

| (if (eq key (quote SUB)) (- (EVAL (cadr e) n v) (EVAL (caddr e) n v))                                                                                              |             |

| (if (eq key (quote MUL)) (* (EVAL (cadr e) n v) (EVAL (caddr e) n v))                                                                                              |             |

| $(if (eq key (quote DIV)) \qquad (/ (EVAL (cadr e) n v) (EVAL (cadr e) n v))$                                                                                      |             |

| (if (eq key (quote REM)) (rem (EVAL (cadr e) n v) (EVAL (caddr e) n v))                                                                                            |             |

| (if (eq key (quote EQ)) (eq (EVAL (cadr e) n v) (EVAL (caddr e) n v))<br>(if (eq key (quote LEQ)) (< (EVAL (cadr e) n v) (EVAL (caddr e) n v))                     |             |

| $\begin{array}{ll} (if (eq key (quote LEQ)) & (\leq (EVAL (cadr e) n v) (EVAL (caddr e) n v)) \\ (if (eq key (quote CAR)) & (car (EVAL (cadr e) n v)) \end{array}$ |             |

| (if (eq key (quote CDR)) (cdr (EVAL (cadr e) n v))<br>(if (eq key (quote CDR)) (cdr (EVAL (cadr e) n v))                                                           |             |

| (if (eq key (quote CONS)) (cons (EVAL (cadr e) n v)) (EVAL (caddr e) n v))                                                                                         |             |

| (if (eq key (quote ATOM)) (atom (EVAL (cadr e) n v))                                                                                                               |             |

| $(if (eq key (quote IF)) \qquad (let ((e1 (cadr e)) (e2 (caddr e)) (e3 (cadddr e)))$                                                                               |             |

| (v ((o1 (v)                                                                                                                    |             |

| (if (eq key (quote LAMBDA))(cons (cons (cadr e) (caddr e)) (cons n v))                                                                                             |             |

| (if (eq key (quote LET)) (let ((y (vars (cddr e))) (z (evlis (exprs (cddr e)) n v)))                                                                               |             |

| (EVAL (cadr e) (cons y n) (cons z v)))                                                                                                                             |             |

| (if (eq key (quote LETREC)) (let* ((y (vars (cddr e)))                                                                                                             |             |

| (v1 (cons (quote PENDING) v))                                                                                                                                      |             |

| (z (evlis (exprs (cddr e)) (cons y n) v1)))                                                                                                                        |             |

| (EVAL (cadr e) (cons y n) (rplaca v1 z)))                                                                                                                          |             |

|                                                                                                                                                                    | application |

| (EVAL (cdar c) (cons (caar c) (cadr c)) (cons z (cddr                                                                                                              | c)))        |

|                                                                                                                                                                    |             |

| (def APPLY                                                                                                                                                         |             |

| (lambda (f x))                                                                                                                                                     |             |

| (let ((c (EVAL f nil nil)))                                                                                                                                        |             |

| (EVAL (cdar c) (cons (caar c) (cadr c)) (cons x (cddr c))))))                                                                                                      |             |

|                                                                                                                                                                    |             |

Table 3.2: LispKit Interpreter Written in Franz Lisp

LispKit expressions will always be evaluated within some context. New bindings are added to the existing context by LET and LETREC operators. Thus, the interpretation of a variable x in a context (n,v), is simply the value in the location in v that corresponds to the location of x in n. The interpretation of a LET expression is the interpretation of the expression part in the current context extended by adding the list of bound variables to the front of the variable namelist, and adding the values, obtained by evaluating the value expressions in the existing context, to the front of the valuelist. Thus

$$(EVAL (LET e (x_1.e_1)...(x_k.e_k)) n v) =$$

$$(EVAL e ((x_1...x_k).n)(((EVAL e_1 n v)...(EVAL e_k n v)).v)$$

Function definitions may contain both free and bound variables within the body of the lambda expression. Bindings are defined to be static, in that values bound to free variables within a  $\lambda$ -expression are determined from the context in which they are defined, rather than in the context in which the function is called. To facilitate this, the notion of a closure is introduced for the interpretation of a function. The closure will consist of the defining context, along with the list of  $\lambda$ -bound variables, and the body of the LAMBDA expression.

$$(EVAL (LAMBDA (x_1 \dots x_n) e) n v) = (((x_1 \dots x_n) e) (n v))$$

The defining context consists of the namelist and valuelist. The namelist is the collection of bound variable names, and the valuelist is the corresponding collection of the values associated with each variable name. When the expression is applied to a list of arguments, the list of  $\lambda$ -bound variables will be added to the namelist. The evaluated arguments are added to the valuelist, creating a new context for evaluating the body of the function, in which the local variables are defined.

In a *LETREC* expression, the variables are to be bound to (possibly mutually) recursive functions, thus the context in which these functions are evaluated must include the values of the functions themselves. This is accomplished by evaluating the expressions in a context which has the values of the recursively bound variables still pending. In practice, an empty list is used as a place-holder at the beginning of the valuelist. Since each expression is required to evaluate to a function-valued object, each will evaluate to a closure, with the context part of all being identical. Thus, a single destructive *rplaca* operation can be used to alter the pending value of

#### CHAPTER 3.

the valuelist to instead point to the list of closures that are created. A circular data structure is thus created. A simplified example illustrates the idea.

$(EVAL (LETRECe (f_1.e_1)...(f_k.e_k)) n v) = (EVAL e (y.n) (rplaca v' z)$ where  $y = (f_1...f_k)$ where v' = (PENDING.v)where  $z = ((EVAL e_1 (y.n) v')...(EVAL e_k (y.n) v'))$

The reader should recognize that the use of a destructive Lisp operation in defining the interpretation of the LispKit expression does not conflict with the status of LispKit as a purely functional language. The LispKit programmer does not have a destructive operator to use in programming; the destructive operator is only used in creating a context to represent recursive function definitions.

To complete the interpretation, the interpretation of each well-formed LispKit expression is given.

- Constants are represented by a dotted pair with the atom QUOTE as the car. Regardless of its context, it will evaluate to the cadr of the pair. Thus (QUOTE 2) evaluates to 2, and (QUOTE (a b c)) evaluates to (a b c). The three special symbolic atoms, NIL, T, and F are mapped to the Franz Lisp values of nil, t, and nil respectively in the interpreter.

- The arithmetic operators work as one would expect. For example,  $(ADD e_1 e_2)$  in the context (n,v) will evaluate to the sum of the values of  $e_1$  and  $e_2$ , both evaluated in (n,v). SUB, MUL, DIV, and REM work similarly.

- The relational operators, EQ and LEQ, evaluate their arguments in the same fashion as the arithmetic operators. However, EQ is interpreted as working the same way as the eq function in Franz Lisp<sup>1</sup>, in that two S-expressions are equal

<sup>&</sup>lt;sup>1</sup>This differs from the definition given in [Hen80] pp. 22, 53, which defines EQ only when at least one of its arguments is an atom.

if they are both atoms and they evaluate to the same value, or if they are both dotted pairs and they are both pointers to the same cons cell.

- The structural operators, CAR, CDR, CONS and ATOM are interpreted as performing the same operations as the corresponding car, cdr, cons and atom operations in Franz Lisp, when applied to the interpreted arguments. Again, arguments are evaluated as for arithmetic operators.

- The conditional form evaluates its first argument in the given context, and if this evaluates to T, then the second argument is evaluated; otherwise the last argument is evaluated. This form evaluates only one of the two branches, permitting, for example, testing for terminating conditions of recursive function definitions.

- The function call is interpreted by adding the value of the function's arguments, interpreted in the current context, to the start of the valuelist in the context part of the closure. Similarly, the list of bound variables is added to the start of the namelist in the context part of the closure, and the body of the closure is evaluated in the thus extended context.

Finally, the top level program must evaluate to a function-valued object which is applied to a list of arguments. Free variables are not permitted in the top level program, so that our starting context consists of a pair of empty lists.

#### Example 1

The first example is a nonrecursive function that takes a function as an argument and returns a function-valued object:

(LET (twice double) (twice LAMBDA (f) (LAMBDA (x) (f (f x)))) (double LAMBDA (x) (ADD x x)))) Let E represent this expression, and  $e_1$  and  $e_2$  the expressions to be bound to *twice* and *double* respectively.

$(EVAL E () ()) \implies (EVAL (twice double)) \\ ((twice double)) \\ (list (cons (EVAL e_1 nil nil)) \\ (cons (EVAL e_2 nil nil)) \\ nil))))$

The two expressions,  $e_1$  and  $e_2$ , evaluate to function closures as follows:

$(EVAL \ e_1 \ nil \ nil) \\ \implies (((f) \ LAMBDA \ (x) \ (f \ (f \ x))) \ nil) \\ (EVAL \ e_2 \ nil \ nil) \\ \implies (((x) \ ADD \ x \ x) \ nil)$

The next stage evaluates the application (twice double) in the context extended with the new variables and values. It is expected that the first item in the application will evaluate to a function valued object, and both it and the single argument are evaluated in the context extended with e1 and e2, and then the body of the function valued object (LAMBDA (x) (f (f x))) is evaluated in a new context extended with the variable f and the value of double, producing a closure as a result.

$$\implies (EVAL '(LAMBDA (x) (f (f x))))$$

$$\stackrel{'((f))}{\stackrel{'(((((x) ADD x x) nil))))}{\implies}$$

$$\implies (((x)$$

$$f (f x)))$$

$$(((x) ADD x x) nil))))$$

A valid LispKit program requires a list of arguments to which a function is applied. The argument list (7) will be used for this example. Thus evaluating the previous function applied to the argument list causes the body of the function to be evaluated in an environment with bindings for both x and f.

$$\implies (EVAL (f (f x))) \\ ((x) (f)) \\ ((7) ((((x) ADD x x) nil))))$$

The variable f is bound to a function closure, but its argument f x must be evaluated. This is done in the same context, so that f is bound to the function closure of double and x to 7.

$$(EVAL (f x) ((x) (f)) (((x) ADD x x) nil)))) \Rightarrow (EVAL (ADD x x) ((x))((7))) \Rightarrow (+ (EVAL x ((x))((7))) (EVAL x ((x))((7)))) \Rightarrow (+ 7 7) \Rightarrow 14 .$$

The result of this evaluation is installed in the context as the value to be bound to x when the outer function application is evaluated.

$$\begin{array}{c} (EVAL \ (f \ (f \ x)) \\ ((x) \ (f)) \\ ((7) \ ((((x) \ ADD \ x \ x) \ nil)))) \\ \implies (EVAL \ (ADD \ x \ x) \ ((x)) \ ((14))) \\ \implies (+ \ (EVAL \ x \ ((x)) \ ((14)))) \\ (EVAL \ x \ ((x)) \ ((14)))) \\ \implies (+ \ 14 \ 14) \\ \implies 28 \end{array}$$

# Example 2

The next example is the even function, defined using mutually recursive functions:

even =

$$\lambda x. if(x = 0)$$

then TRUE else (odd  $(x - 1)$ )

odd =  $\lambda x. if(x = 0)$  then FALSE else (even  $(x - 1)$ )

(LETREC even (even LAMBDA (x) (IF (EQ x (QUOTE 0)) (QUOTE TRUE) (odd (SUB x (QUOTE 1))))) (odd LAMBDA (x) (IF (EQ x (QUOTE 0)) (QUOTE FALSE) (even (SUB x (QUOTE 1)))))))

To apply the function to the argument list (1), first evaluate the LETREC expression. Each of the two items bound therein is evaluated in a context with the namelist augmented by (even odd) and the initially empty valuelist onto the start of which is cons'ed the special PENDING atom. Since both expressions are  $\lambda$ -expressions, they will evaluate to function closures, both containing identical contexts (pointers to the same context), with PENDING as the first item in the valuelists.

The body of the LETREC, the bound variable even, is then evaluated in the same context, but modified by destructively replacing the *PENDING* atom with the list of closures obtained for the  $\lambda$ -expressions above. This will create a circular valuelist structure, so a graphical representation will be used.

```

\begin{array}{l} (EVAL \ example-2 \ nil \ nil) \\ \Longrightarrow (EVAL \ even \\ ((even \ odd)) \\ (rplaca \ (PENDING) \\ ((((x) \\ IF \ (EQ \ x \ (QUOTE \ 0)) \\ (QUOTE \ TRUE) \\ (odd \ (SUB \ x \ (QUOTE \ 1)))) \\ ((even \ odd)) \\ PENDING) \\ (((x) \\ IF \ (EQ \ x \ (QUOTE \ 0)) \\ (QUOTE \ TRUE) \\ (even \ (SUB \ x \ (QUOTE \ 1)))) \\ ((even \ odd)) \end{array}

```

PENDING)))

Figure 3.1: Valuelist Structure Before Destructive Operation

The important thing to note in Figure 3.1 is that the atom *PENDING* occurs in only one place, with pointers to it from several places. Thus, doing a destructive *rplaca* operation on the list with *PENDING* as the first item, will change the value of *PENDING* in all locations, and create a circular list structure, so that references to the recursive functions within the body of the functions, properly refer to the closure value used to represent the function.

The next step consists of evaluating the expression *even*. This returns a closure from the valuelist bound to this name. Evaluating the application of this function to the argument list (1), the body of *even* is evaluated in a context augmented with the binding 1 to the lambda bound variable x. It should be readily apparent from the valuelist of Figure 3.2 that recursive references to *even* and *odd* are possible as the appropriate function closures are included.

Figure 3.2: Circular Valuelist Structure After Destructive Operation

Once the circular environment structure has been established, the remainder of the function evaluation continues in a similar fashion to the previous nonrecursive example.

In summary, the LispKit language has been described, and its syntax and its semantics defined, the latter by means of an interpreter. The concept of closures to represent the value of a function object, and the use of context to define bindings, was illustrated by two examples, using both higher order and recursive functions.

## **3.3 SECD Architecture**

Now follows a detailed description of a machine architecture, called the SECD architecture, that will support the execution of programs compiled from LispKit Lisp. A complete description of the machine instructions and state transitions effected by each will define the semantics of the machine language. The SECD architecture, so named because of its four principal registers, was invented by Landin [Lan64] and described in detail by Henderson [Hen80]. Each of the four registers is referred to as containing an S-expression, which in the actual implementation will be a pointer to a data structure representing the expression. The term "stack" is used to refer to the data structure "within" a register. The four registers are:

- S stack holds intermediate computation results

- E environment holds values bound to variables during evaluation

- C control list holds the machine-language program being executed

- D dump saves values of other registers on calling a new function.

It is important to note that the entire state of the machine can 'be denoted by giving the content of its four registers. Thus instructions are defined by state changes, enabling an interpreter to be developed by pattern matching, and the use of structural induction in proofs about the machine execution.

Each instruction is defined in terms of its effect on the machine state. For example, the ADD instruction definition is:

(a b.s) e (ADD.c) d  $\rightarrow$  (b+a.s) e c d

This instruction expects two arguments on top of the S stack. After execution, the two arguments are replaced by their sum, which is *cons*'ed onto whatever was below the arguments on the stack. The E and D registers are unaltered, but the C stack contains the rest of the control list that followed the ADD instruction.

Similarly to the interpreter presented previously, a means of storing bindings is provided by a valuelist stored in the environment stack E, which is, as before, a list of lists. Instead of an associated namelist, variable names are replaced with a LD instruction and a pair of arguments telling it where to find the value in the environment. The first determines which list and the second which element from that list to retrieve. Two auxiliary functions, *index* and *locate*, are defined:

$$index(n,s) = if (n=0)$$

then  $(car(s))$  else  $(index(n-1, cdr(s)))$

$locate(i,e) = index (cdr(i), index(car(i).e))$