#### THE UNIVERSITY OF CALGARY

# A GLOBAL TEST GENERATION SYSTEM FOR SEQUENTIAL CIRCUITS

bу

Bin Du

#### A DISSERTATION

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES

IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE

DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA DECEMBER, 1997

© Bin Du 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-34670-6

#### ABSTRACT

With the rapid progress of VLSI technology, integrated circuit complexity increases greatly. The reliability of a chip is very important to VLSI engineering and even our daily life. Due to the increase in size and complexity of circuits placed on a chip. it is very difficult to test a chip at an affordable cost.

Automatic Test Pattern Generation (ATPG) plays an important role in VLSI technology. Reduction in test application time and test set size is highly desirable for the reduction of the overall cost in integrated circuit fabrication and testing. Testing of digital circuits involves the generation of a set of test vectors and their application to detect faults in the circuits. An important part of testing is the creation of effective test vectors. The test generation problem for sequential circuits is known to be a difficult task. It is difficult to achieve a significant breakthrough in realizing efficient ATPG algorithms to test large sequential circuits.

A global test generation approach for sequential circuits, called GLOBALTEST. is presented in this dissertation. Global test generation is formulated as the problem of tracing different sensitive paths from the primary inputs and present state lines to the primary outputs and next state lines in a circuit. It consists of two parts: a fault-independent test generation algorithm and a fault-oriented test generation algorithm. At first, a new backward assignment method is presented to extract the ON/OFF sets of the primary outputs and next state lines by partitioning circuits. The combinational test vectors can be extracted at the same time. State justification and

state differentiation are efficiently performed using the ON/OFF sets of the primary outputs and next state lines. To enhance the efficiency of state differentiation in the existing three-phase ATPG, a backward deterministic method for state differentiation is proposed and the order of next state lines in state differentiation is presented. The fault-independent test generation algorithm can detect most of the testable faults in the sequential circuits. A disadvantage of the method is that it can not determine the redundant faults.

The fault-oriented test generation algorithm is developed to detect the remaining faults and determine the redundant faults. The recent advances in combinational test generation based on Boolean satisfiability and transitive closure provide a powerful method for test generation. We extend Boolean satisfiability and transitive closure to sequential circuit test generation.

Test compaction is an important part in test generation. We formulate the test compaction problem as the set covering problem. An efficient set covering algorithm (HICOMPACT) is proposed to compact test vectors. It attempts to select the necessary test vectors for the faults detected and eliminate other redundant test vectors so the original fault coverage is not compromised. This method generates a compact testing sequence for a given fault.

The global test generation algorithm for sequential circuits is tested using the IS-CAS'89 sequential benchmark circuits. The proposed algorithm has yielded a high fault coverage and provided time efficient procedures to generate tests for large sequential circuits. The experimental results are compared with other existing test generation systems.

#### Acknowledgement

First of all. I want to thank my supervisor, Professor Jun Gu. for his advice and support during my graduate study. It is my greatest fortune to have Jun as my advisor. I have benefited tremendously from his guidance and insight over the years. I have learnt a lot of engineering optimization methods, and these methods are quite effective. I have been convinced that Jun is a dedicated educator and first class researcher. I am very grateful for his constant encouragement and his perspectives on life at large.

I would like to thank Professor Dave Halliday, Professor Jim Haslett. Professor Guojun Liu. and Professor Xiaoling Sun for their careful reading of the dissertation and many helpful suggestions. I want to specially thank all the faculty members at the department of electrical and computer engineering for providing an excellent education and a rewarding experience. In particular, I thank Professor R. A. Stein for his help over the years. I am also grateful to Professor Danny H.K. Tsang for many valuable discussions.

I have made a number of good friends during my stay in Hong Kong. I thank all my friends for their friendship, in particular, Wei Xiong, Yong Sun, Lixin Wang. We witnessed the transition of Hong Kong to China together.

I am greatly indebted to my wife, Xiaoying Liu for her encouragement and support over these years. I also thank the Liu family for their constant support.

Finally, I specially thank my family for their love and support. Mere words can not express my gratitude to my parents. My mother and father have given me everything

it takes to be here. My sisters have been a source of inspiration and given me a lot of support.

То

my Mom. Dad. Xiaoying, Kaixiang, Wen. Heng, and Min

## TABLE OF CONTENTS

| ΑI | PR   | OVAL    | PAGE                                                            | ii   |

|----|------|---------|-----------------------------------------------------------------|------|

| Αŀ | 3ST) | RACT    |                                                                 | iii  |

| AC | CKN  | OWLE    | EDGEMENT                                                        | v    |

| DI | EDIC | CATIO   | N                                                               | vii  |

| TA | BL   | E OF (  | CONTENTS                                                        | viii |

| LI | ST ( | OF TA   | BLES                                                            | xi   |

| LI | ST ( | OF FIG  | GURES                                                           | xiii |

| CI | HAP  | TERS    |                                                                 |      |

| 1. | INI  | RODU    | UCTION                                                          | 1    |

|    | 1.1  | Backgr  | round                                                           | 2    |

|    | 1.2  | Fault 2 | Models                                                          | 3    |

|    |      | 1.2.1   | Faults in VLSI Systems                                          | 3    |

|    |      | 1.2.2   | Fault Models                                                    | 5    |

|    |      | 1.2.3   | Fault Equivalence and Dominance                                 | 6    |

|    | 1.3  | Test C  | Generation and Its Problems                                     | 7    |

|    |      | 1.3.1   | NP-Completeness of Combinational Test Generation                | 7    |

|    |      | 1.3.2   | Test Generation Problems in Sequential Circuits                 | 8    |

|    | 1.4  | Appro   | aches to Test Generation Problems Presented in the Dissertation |      |

|    | 1.5  |         | ization of the Dissertation                                     | 10   |

| 2. | ov   | ERVIE   | EW OF EXISTING METHODS                                          | 12   |

|    | 2.1  | Overv   | iew of Test Generation for Combinational Circuits               | 12   |

|    |      | 2.1.1   | Structural Methods                                              | 12   |

|    |      | 2.1.2   | Algebraic Methods                                               | 14   |

|            | 2.2  | Overvi          | iew of Test Generation for Sequential Circuits                  | 16 |

|------------|------|-----------------|-----------------------------------------------------------------|----|

|            | 2.3  | Overvi          | iew of Test Compaction                                          | 21 |

|            | 2.4  | Summ            | ary                                                             | 23 |

| 3.         | PRI  | ELIMI           | NARIES                                                          | 24 |

| 4.         | GLO  | OBAL            | TEST GENERATION FOR SEQUENTIAL CIRCUITS                         | 37 |

|            | 4.1  | Observ          | vations                                                         | 38 |

|            | 4.2  | The M           | lodel of Global Test Generation                                 | 39 |

|            | 4.3  | The G           | lobal Test Generation System for Sequential Circuits            | 41 |

|            | 4.4  | The Fa          | ault-Independent Test Generation Algorithm                      | 44 |

|            |      | 4.4.1           | Cover and Excitation Vector Extraction                          | 45 |

|            |      | 4.4.2           | State Justification                                             | 48 |

|            |      | 4.4.3           | State Differentiation                                           | 49 |

|            |      | 4.4.4           | Fault Simulation                                                | 53 |

|            | 4.5  | The Fa          | ault-Oriented Test Generation Algorithm                         | 54 |

|            |      | 4.5.1           | Pseudo-Combinational Circuit Test Generation                    | 58 |

|            |      | 4.5.2           | Determination of Redundant Faults                               | 60 |

|            | 4.6  | Summ            | ary                                                             | 61 |

| =          | EV'  | TRAC'           | TION OF COVER SETS AND COMBINATIONAL EX-                        |    |

| <b>С</b> ] | ITAT | IIIAO           | VECTORS                                                         | 63 |

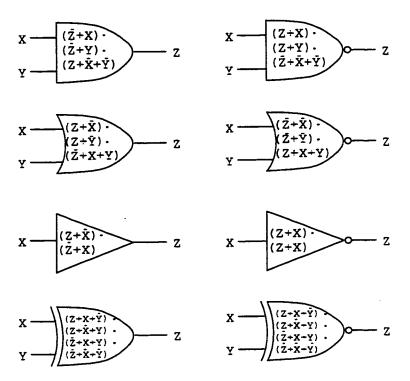

|            | 5.1  | Backw           | vard Assignment Rules (B-rules)                                 | 64 |

|            | 5.2  | Consis          | stency and Constraints                                          | 70 |

|            | 5.3  | Partit          | ioning Sequential Circuits                                      | 72 |

|            | 5.4  |                 | ation of Combinational Excitation Vectors from Cover Extraction | 75 |

|            | 5.5  |                 | lgorithm of Cover Extraction and Combinational Excitation Vec-  | 76 |

|            | 5.6  | Pseud<br>Syster | o-Combinational Circuit Test Generation for Fault-Oriented ATPG | 79 |

|            |      | 5.6.1           | Circuit Representation                                          | 80 |

|            |      | 5.6.2           | Signal Dependencies                                             | 84 |

|            |      | 5.6.3           | Pruning the Search Tree                                         | 86 |

|            |      | 5.6.4           | Combinational Circuit Test Generation Procedure                 | 90 |

|            | 5.7  | Summ            | nary                                                            | 90 |

| 6.           | STA  | TE JUSTIFICATION AND STATE DIFFERENTIATION 92                            |

|--------------|------|--------------------------------------------------------------------------|

|              | 6.1  | State Justification                                                      |

|              | 6.2  | State Differentiation                                                    |

|              | 6.3  | Summary                                                                  |

| 7.           | TES  | ST COMPACTION OF SEQUENTIAL CIRCUITS                                     |

|              | 7.1  | Introduction                                                             |

|              | 7.2  | The Formulation of Test Compaction Problem to Set Covering Problem 11    |

|              | 7.3  | A Multispace Search Algorithm for Test Compaction of Sequential Circuits |

|              | 7.4  | Summary                                                                  |

| 8.           | EX   | PERIMENTAL RESULTS 12                                                    |

|              | S.1  | ISCAS'89 Benchmark Circuits                                              |

|              | 8.2  | Evaluation of the Proposed Test Pattern Generator                        |

|              | 8.3  | Experimental Results of Test Compaction                                  |

|              | 8.4  | Summary                                                                  |

| 9.           | СО   | NCLUSIONS AND FUTURE WORK 13                                             |

| $\mathbf{R}$ | efe: | RENCES                                                                   |

|              |      |                                                                          |

## LIST OF TABLES

| 3.1 | Cube intersection operation                                                                                                               | 34  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Sharp product operation                                                                                                                   | 35  |

| 6.1 | Initial state justification process                                                                                                       | 96  |

| 6.2 | Final state justification process                                                                                                         | 97  |

| 6.3 | The ON and OFF sets of primary output G17                                                                                                 | 106 |

| 6.4 | The process of exciting the fault $G2$ s-a-0 to primary output $G17$                                                                      | 107 |

| 6.5 | State differentiation process for the fault $CLRB \rightarrow UC\_17VD$ s-a-0 in circuit s382 from ISCAS'89 sequential benchmark circuits | 110 |

| 7.1 | An example ex1 of test compaction for sequential circuits with three test sequences and six faults                                        | 114 |

| 7.2 | The original there sequences in the example ex1 can be divided into eight subsequences                                                    | 115 |

| 8.1 | ISCAS'89 sequential benchmark circuit characteristics                                                                                     | 122 |

| 8.2 | Real execution performance of our algorithm GLOBALTEST on a SUN Sparc 20 with the ISCAS'89 sequential benchmark circuits with reset.      | 124 |

| 8.3 | Test generation comparison with STEED and VERITAS on ISCAS'89 benchmark circuits                                                          | 125 |

| 8.4 | Real execution performance of our algorithm HICOMPACT on a SUN Sparc 20 with the ISCAS'89 sequential benchmark circuits                   | 128 |

| 8.5 | Test generation comparison with other procedures on the ISCAS'89 sequential benchmark circuits                                            | 130 |

| 8.6 | Real execution performance of HICOMPACT on a SUN Sparc 20 with     |     |

|-----|--------------------------------------------------------------------|-----|

|     | randomly generated set covering problem instances. The cost is the |     |

|     | total number of test vectors needed to detect the faults           | 131 |

## LIST OF FIGURES

| 1.1 | Three input AND gate with its truth table                                                                                 | 5  |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | A sequential circuit.                                                                                                     | 24 |

| 3.2 | An equivalent pseudo-combinational iterative array to the sequential circuit in Fig. 2.1.                                 | 25 |

| 3.3 | The meaning of logic values $FD$ , $F\overline{D}$ , $TD$ , $T\overline{D}$ ,                                             | 27 |

| 3.4 | A general pseudo-combinational circuit is obtained from the corresponding sequential circuit by disabling all flip-flops. | 29 |

| 3.5 | A sequential circuit s27 from ISCAS'89 benchmarks.                                                                        | 31 |

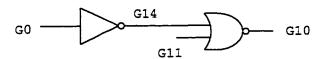

| 3.6 | The input cone of the primary output G17 in circuit s27                                                                   | 31 |

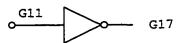

| 3.7 | The input cone of the next state line G10 in circuit s27                                                                  | 32 |

| 3.8 | The input cone of the next state line G11 in circuit s27                                                                  | 32 |

| 3.9 | The input cone of the next state line G13 in circuit s27.                                                                 | 32 |

| 4.1 | One output is set to logic value $D$ and the combination of logic values on the inputs is the $D$ set of the output       | 39 |

| 4.2 | One sensitive path between one input and one output.                                                                      | 41 |

| 4.3 | GLOBALTEST: The global test generation system for sequential circuits.                                                    | 42 |

| 4.4 | The fault-independent test generation algorithm for sequential circuits                                                   | 46 |

| 4.5 | General iterative array model for state justification                                                                     | 48 |

| 4.6 | State transition graph for state justification                                                                            | 49 |

| 4.7  | Iterative array model for state differentiation                                                                                    | ÐÜ |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.8  | State transition graph for state justification and state differentiation                                                           | 50 |

| 4.9  | The fault simulation algorithm.                                                                                                    | 55 |

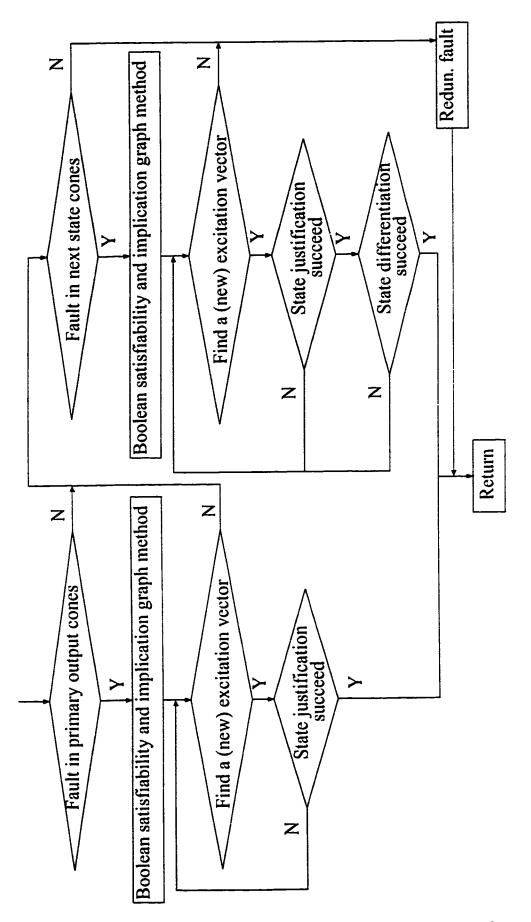

| 4.10 | The fault-oriented test generation algorithm for sequential circuit                                                                | 56 |

| 4.11 | The flow chart of the fault-oriented test generation algorithm for sequential circuits.                                            | 62 |

| 5.l  | The backward assignment rules (B-rules) of AND gate                                                                                | 65 |

| 5.2  | The backward assignment rules (B-rules) of NAND gate                                                                               | 65 |

| 5.3  | The backward assignment rules (B-rules) of OR gate                                                                                 | 66 |

| 5.4  | The backward assignment rules (B-rules) of NOR gate                                                                                | 66 |

| 5.5  | The backward assignment rules (B-rules) of XOR gate                                                                                | 67 |

| 5.6  | The backward assignment rules (B-rules) of XNOR gate                                                                               | 67 |

| 5.7  | Extraction of $D$ set of an output in a combinational circuit                                                                      | 69 |

| 5.8  | The consistency constraint of logic values.                                                                                        | 71 |

| 5.9  | The input cones of the primary output and next state lines in circuit s27 after the node G11 is considered as a virtual input node | 74 |

| 5.10 | The Algorithm of Cover Extraction and Combinational Excitation Vector Generation.                                                  | 78 |

| 5.11 | The CNF formulae of basic gates                                                                                                    | 82 |

| 5.12 | The CNF formula of 3-input NAND gate.                                                                                              | 82 |

| 5.13 | Implication graph of an AND gate                                                                                                   | 83 |

| 5.14 | Formula extraction of a simple circuit S1.                                                                                         | 84 |

| 5.15 | Formula extraction of the simple circuit S1 with a fault $G$ s-a-0                                                                                                                                                                                                                                                               | 85   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.16 | The XOR of the unfaulted and faulted circuits should be 1                                                                                                                                                                                                                                                                        | 85   |

| 5.17 | The procedure of signal dependency computation                                                                                                                                                                                                                                                                                   | 87   |

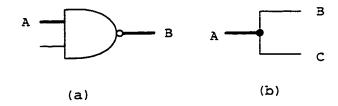

| 5.18 | (a). If A is sensitized, B must be sensitized: $(\overline{EX_A} + EX_B)$ . (b). If A is sensitized, either B or C must be sensitized: $(\overline{EX_A} + EX_B + EX_C)$ .                                                                                                                                                       | 88   |

| 6.1  | State justification procedure                                                                                                                                                                                                                                                                                                    | 94   |

| 6.2  | The procedure of obtaining fan-in states of present state                                                                                                                                                                                                                                                                        | 95   |

| 6.3  | Three kinds of faults defined in our algorithm                                                                                                                                                                                                                                                                                   | 98   |

| 6.4  | The procedure of single-vector state differentiation.                                                                                                                                                                                                                                                                            | 101  |

| 6.5  | The procedure of multi-vector state differentiation.                                                                                                                                                                                                                                                                             | 102  |

| 6.6  | The backward deterministic procedure for single-vector state differentiation                                                                                                                                                                                                                                                     | .105 |

| 6.7  | A general state differentiation process.                                                                                                                                                                                                                                                                                         | 108  |

| 7.1  | An example of the set covering problem                                                                                                                                                                                                                                                                                           | 113  |

| 7.2  | The formulation of test compaction for sequential circuits as the set covering problem                                                                                                                                                                                                                                           | 117  |

| 7.3  | In the value space, a traditional search process (dashed line) cannot pass a "wall" of high cost search states (hatched region). It fails to reach the final solution state. F. A multispace search process (solid lines) scrambles across different search spaces. It could bypass this "wall" through the other search spaces. | 118  |

#### CHAPTER 1

#### INTRODUCTION

Very Large Scale Integration (VLSI) is the process of integrating hundreds of thousands of semiconductor components and interconnections into a monolithic integrated circuit. As a result of the continuous progress in integrated circuit fabrication techniques, the complexity of digital systems which can be implemented on a single micro-electronic chip has increased. A major problem, one which is growing in importance, is testing. Since VLSI has been widely used in many application areas, ranging from consumer products to critical controllers, the reliability of VLSI circuits is of paramount importance. The problems associated with testing of VLSI circuits have been exacerbated with the rapid advances in VLSI technology. With little or no increase in the number of input/output (I/O) pins, more logic must be accessed with almost the same number of I/O pins, i.e., reduction in the pin-to-gate ratio, making it much more difficult to test a VLSI chip.

As a consequence of growing circuit complexity, testing is taking an increasingly larger proportion of total product cost. Ironically, the very software design tools that make it possible to put more circuits on a chip at a reduced cost are effectively increasing the cost of circuit testing. The advantages of VLSI are reduced system cost, good performance, and great reliability. These advantages would be lost unless VLSI devices can be tested economically.

#### 1.1 Background

The manufacturing of a VLSI chip consists of fabrication and testing. Testing is required in order to discover defects in the VLSI chip. Design and test development precede manufacture. Test activities are interwoven with the VLSI design process. Architectural design consists of the partitioning of a VLSI chip into realizable blocks. With the increase in complexity of the VLSI system, architectural design becomes more and more important. Either the logic should be synthesized in a testable form or the synthesized logic should be analyzed and improved for testability.

The objectives in testing a VLSI design are twofold. The first is to verify logic correctness and timing behavior of the circuit before fabrication. The second is to determine, after fabrication, whether components and interconnections on the chip are fabricated correctly. The testing after fabrication is, by far, the most pressing problem confronting both designers and test engineers. It is considered as the major obstacle to the full exploitation of the benefits obtained from realizing extremely complex VLSI systems [55]. These tests should thoroughly check every node in the circuit and ideally, cover all faults that can possibly occur during fabrication. In this dissertation, we concentrated on the second kind of tests.

In VLSI circuit design, the testing process is referred to as test generation and fault simulation. The goal of test generation is to obtain test vectors of high quality at an affordable cost. The quality of a set of test vectors is measured by fault coverage (a fraction of the modeled faults detected by the test vectors) and by test length (the number of vectors in the test set). Given a set of faults and a set of test vectors. the goal of fault simulation is to determine which faults can be detected by the test vectors. Both test generation and fault simulation rank equally in importance and complement one another. Test vectors capable of distinguishing between good circuits

and faulted circuits do not become effective until these vectors are simulated so that their effects can be determined. Conversely, extremely accurate simulation with very precise models, and poor test vectors, will not effectively detect many defects.

Various factors contribute to testing and its cost. Testing cost is determined mainly by the cost of real time test pattern generation and test application. The cost of test pattern generation depends on the computer time required to run the test pattern generation program. The cost of test application is determined by the cost of equipment plus the testing time required to apply the test. The testing time may be assumed to be directly proportional to the number of tests. For combinational circuits, a test is a test vector. For sequential circuits, a test is a sequence of test vectors.

A straightforward method for determining the testability of a circuit is to use an Automatic Test Pattern Generation (ATPG) program. It generates test vectors and determines the fault coverage. The running time of the program, the number of test patterns generated, and the fault coverage provide a measure of the testability of the circuit.

#### 1.2 Fault Models

Fault models are a means of describing the effects of defects in a circuit. The accuracy of the fault models in emulating the operation of the circuit under fault conditions alters the effectiveness of test patterns in detecting faulty devices. The test fault models are identified and formulated in this section.

## 1.2.1 Faults in VLSI Systems

The testing of a digital logic circuit involves the application of stimuli to the circuit and the measurement of the response to determine whether the circuit is

functionally correct. An important part of testing is the creation of effective stimuli. A fault is a physical or intellectual defect such as an open circuit, a short circuit, or a ground in a circuit, component, or line [38]. A defect in a circuit may cause either a permanent fault or an intermittent fault. Usually, testing is performed primarily to detect permanent faults. The most commonly occurring faults are modeled. The fault model is a computer model of the circuit that has been modified to conform to some premise or conjecture about real physical defects. Then, input stimuli are created which can distinguish between the fault-free and the faulted models. This approach has a number of advantages [40]:

- It is effective to create specific tests for faults most likely to occur.

- The effectiveness of the test set can be measured by determining how many faults can be covered by the set of test vectors.

- Specific defects can be associated with specific test patterns. If a circuit under test responds to a test pattern incorrectly, the information indicates that the defects exist.

This method has become a standard approach to developing tests for digital logic failures.

It is desirable to describe faults at various levels of abstraction in VLSI systems. A fault which is described at a very low level, e.g., the transistor level, may accurately describe the physical phenomena causing the fault, but one of the difficulties with this level is the tedious task of analyzing each individual component in the circuit. Further complicating the task is the fact that there are several technologies in use and each has its own way to perform digital logic operations.

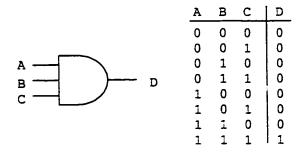

Logic symbols have long been used to represent logic circuits. These symbols reduce the complexity of the logic circuit drawings and have the advantage of being technology-independent. Consider the logic diagram of an AND gate and its truth table as an example, as shown in Figure 1.1.

Figure 1.1. Three input AND gate with its truth table.

With these symbols, the circuits can be logically represented at a higher level, i.e., the gate level. The faults can be described at the gate level and it would be simpler to consider the faults at that level. An important advantage of this representation is the fact that a computer algorithm can be designed upon these logic operators, which are, for most part, independent of the particular technology chosen to implement the circuits.

#### 1.2.2 Fault Models

Fault models are used to describe the effect of a defect or failure in a circuit. The development of a suitable fault model is a complex task and requires a knowledge of circuit design, logic design, and fault testing. One of the earliest and still widely used fault models at the gate level of abstraction is the *stuck-at* model. In this model, it is assumed that physical defects and faults will result in the lines at the logic gate level of the circuit being permanently stuck at logic value 0 or 1. This model is popular

since many defects at the transistor level can be modeled at the gate level. It has proven to be an effective measure of test quality.

It is impractical to test the combinations of all the stuck-at faults in a circuit. This has led to the adoption of the *single-fault* assumption. When a test is attempted, it is assumed that only a single fault exists at a time.

Consider a circuit containing nodes which interconnect various components in the circuit. At one time, each node may have only one of the following results:

- Fault-free.

- Stuck-at-1. i.e., s-a-1.

- Stuck-at-0. i.e., s-a-0.

The stuck-at-1 fault inhibits the node from switching to a 0. while the stuck-at-0 fault inhibits switching to a 1. The single stuck-at fault model is adopted in this dissertation.

#### 1.2.3 Fault Equivalence and Dominance

In building fault lists, it is often observed that some faults are indistinguishable from others. In Figure 1.1, faults A, B, or C stuck-at 0 would result in the output D being permanently 0 and, therefore, it is impossible to distinguish between an input stuck-at 0 from the output stuck-at 0. These faults are said to be equivalent. There is no test that can distinguish between them. More precisely, if  $T_a$  is the set of tests which detect fault a and a and a is the set of tests which detect fault a and a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and if a is the set of tests which detect fault a and a is the set of tests which detect fault a and a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect fault a is the set of tests which detect f

When we test for inputs, e.g., A, B or C s-a-1, we simultaneously test for the output D s-a-1. A s-a-1 fault on the output, however, prevents one from testing any of the input s-a-1 faults. It is said that the output D s-a-1 fault dominates the input s-a-1 fault. In general, fault a dominates fault b if  $T_b$  is included in  $T_a$ . According to this definition, if fault a dominates fault b, then any test which detects fault b will detect fault a.

Since circuit testing time is affected by the size of the fault list, the reduction of the fault list, a process called *fault collapsing*, can reduce test generation and simulation time. Therefore, fault equivalence and dominance relations can be used to reduce the size of fault lists.

## 1.3 Test Generation and Its Problems

The objective of test pattern generation is to derive input vectors to the circuit which will excite the circuit in such a way that if any faults are present in the circuit the output response of the circuit will differ from that of the fault-free circuit. With the progress of VLSI technology, the problem of fault testing for logic circuits is becoming increasingly difficult. Different approaches and much research work have been applied to deal with the test problem. Despite the maturity of test generation. the testing of VLSI circuits is still considered to be an area with a number of unsolved problems [37].

## 1.3.1 NP-Completeness of Combinational Test Generation

Ibarra and Sahni [28] showed that test generation for combinational circuits belongs to the class of NP-complete problems. This strongly suggests that no test generation algorithm with a polynomial time complexity is likely to exist. The problem of combinational circuit test generation can be viewed as a finite space search

problem [19]. For a combinational circuit with m primary inputs, there exist  $2^m$  combinations of input assignments. Therefore, it is impossible to exhaust all the combinations for large size circuits.

In practice, test generation algorithms for combinational circuits appear to be able to achieve lower average time growth by using heuristic search techniques. Up to now, some well-known test generation algorithms for combinational circuits, such as D-algorithm [53], PODEM [19], FAN [16], NEMESIS [32], and TRAN [9], have been developed. Some of them perform well for certain circuit structures.

#### 1.3.2 Test Generation Problems in Sequential Circuits

Test generation for sequential circuits has long been recognized as a difficult task [7, 39]. It remains to be a challenge in spite of a history of attempts dating back to the late 1960s. One new factor which complicates the task of creating tests for sequential circuits is the presence of memory elements. The outputs of the sequential circuit depend not only on the primary input vectors but also on the present states of the circuit.

For combinational circuits, it is possible, but not necessarily reasonable, to create a complete test for logic faults by applying all possible binary combinations to the inputs. This is not true for sequential circuits with memory elements. Not only may they require more than  $2^m$  tests, they are also sensitive to the *order* in which stimuli are applied. It has been shown [7] that a fault in a general synchronous sequential circuit may require a test sequence of up to  $2^{n+1}$  input test vectors, where n is the number of memory elements in the sequential circuits. Therefore, the search space for sequential circuit test generation is very large.

## 1.4 Approaches to Test Generation Problems Presented in the Dissertation

This dissertation presents a new global search approach for test generation of sequential circuits. The approach traces different sensitive paths taken by a fault at a primary output or next state line by justifying the fault to the primary inputs and present state lines. Therefore, all fault patterns at the primary inputs and present state lines are generated. During the global test generation process, many faults are considered as candidates to be tested simultaneously. Such process aims at utilize common search spaces for different faults to generate common test sequences. The approach consists of two parts: a fault-independent test generation algorithm and a fault-oriented test generation algorithm.

The fault-independent test generation algorithm is independent of individual fault. It considers all faults simultaneously. At first, by partitioning circuits, a new backward assignment method is presented to extract the ON/OFF sets of the primary outputs and next state lines. The combinational excitation vectors can also be extracted at the same time. So cover extraction and excitation vector generation are combined into one phase. State justification and state differentiation are performed using the ON/OFF sets of the primary outputs and next state lines. To enhance the efficiency of state differentiation in the existing three-phase ATPG, a backward deterministic method for state differentiation is proposed and the order of choosing next state lines in state differentiation is presented. The fault-independent test generation algorithm can detect most of the testable faults in the sequential circuits. A disadvantage of the method is that it is difficult to determine all redundant faults.

The fault-oriented test generation algorithm is developed to detect the remaining faults and determine the redundant faults. Each time, it considers one fault at a

time. The Boolean satisfiability and the implication graph algorithms are extended to the sequential circuit test generation. A three-phase test generation for sequential circuits is used in this algorithm.

Test compaction is an important part in test generation. The test compaction problem is formulated as the set covering problem. An efficient set covering algorithm is proposed to compact test vectors. It attempts to select the necessary test vectors for the faults detected and eliminate other redundant test vectors, so the original fault coverage is not compromised. A local reduction and expansion algorithm is then used to further compact the test set. This method generates compact test sequences for the given faults.

## 1.5 Organization of the Dissertation

The dissertation is organized as follows: Previous work in test generation for combinational circuits and sequential circuits is reviewed in Chapter 2. Some related work in test compaction is also presented.

Chapter 3 introduces the related test generation terminologies used in this dissertation.

In Chapter 4, observations that initiated this research work in test generation for sequential circuits are given. A global search test generation system for sequential circuits is presented. Then the steps of cover extraction, combinational circuit test generation, state justification, and state differentiation used in the system are briefly introduced. The algorithms used in these steps are described in Chapters 5 - 6 in detail.

A backward assignment algorithm for cover extraction is described in detail in Chapter 5. It can efficiently extract the ON/OFF sets of the primary outputs and

next state lines and the combinational excitation vectors. A method of partitioning circuits is proposed to enhance the efficiency of extraction.

In Chapter 6, state justification and state differentiation are described. To enhance the efficiency of state differentiation in the existing ATPG system. a backward deterministic algorithm for state differentiation is developed and the order of choosing next state lines in state differentiation is studied.

Test compaction for sequential circuit test generation is discussed in Chapter 7. First, the test compaction problem is formulated as a set covering problem. Then an efficient set covering algorithm is proposed to compact test vectors. A local reduction and expansion algorithm is used to further compact the test vectors.

Experimental results with ISCAS'89 benchmarks are presented in Chapter 8. These results are compared to existing test generation systems. Our algorithm has obtained close to the maximum fault coverage on the most benchmarks.

Chapter 9 concludes this dissertation and discusses possible future work.

#### **CHAPTER 2**

#### OVERVIEW OF EXISTING METHODS

In this chapter, an overview of the work previously done toward test generation is presented. Previous work on the test compaction problem is then reviewed.

Since test generation methods for combinational circuits and sequential circuits are related to each other, previous work on combinational circuit test generation is first briefly discussed.

#### 2.1 Overview of Test Generation for Combinational Circuits

A theoretical study suggests that no test generation algorithm for combinational circuits with polynomial time complexity is likely to exist [28]. Though test generation for combinational circuits is NP-complete, some efficient test generation systems have been developed.

Up to now, some well-known test generation algorithms for combinational circuits have been developed and perform well for certain circuit structures. The existing test generation systems for combinational circuits are divided into two classes: structural methods, such as PODEM [19], and algebraic methods.

#### 2.1.1 Structural Methods

The structural methods derive test vectors from a topological gate description of the circuit. The path sensitization method is one of the frequently used techniques. Among structural search methods in test generation for combinational circuits. the D-algorithm. developed by Roth [53], is one of the oldest and the best known test generation algorithms. This algorithm adopts a five-valued 0, 1,  $X, D, \overline{D}$  calculus to carry out the sensitization and the line justification procedures in a very formal manner. The faulty line is assigned a D or  $\overline{D}$  depending on the fault on the line. The calculus and the circuit structure information are used to determine values on the other lines so that D or  $\overline{D}$  can be sensitized to the primary outputs. A line justification step is then carried out to justify the values assigned in the preceding step. Both the sensitization and the line justification steps may have to be applied many times before a test vector is obtained.

A class of circuits for which the D-algorithm performs particularly poorly are those containing exclusive-or trees. Degradation in performance arises due to an excessive amount of backtracking. This observation motivated Goel [19] to devise a new test generation algorithm called path oriented decision making (PODEM). A branch and bound technique was used in PODEM. The algorithm starts by assigning a value of 0 or 1 to a selected primary input (PI) line, and then determines its implication on the propagation of D or  $\overline{D}$  to a primary output. If no inconsistency is found, it again selects another PI line and assigns a 0 or 1 to it, and then repeats the process, which is referred to as branching. If an inconsistency is determined in the branching, the branching stops and bounding starts. The PI line which was most recently assigned a binary value is assigned the complimentary value, and branching starts again. The complete process stops when either a test vector is found or when the fault is determined to be undetectable. PODEM implementations are known to run an order of magnitude faster than the D-algorithm on most circuits.

Fujiwara and Shimono [16] described techniques to further accelerate a path-

sensitization algorithm like PODEM. Their algorithm, called FAN, does extensive analysis of the circuit connectivity in a preprocessing step to minimize backtracking. FAN has employed a better heuristic in the bounding-and-branching steps to speed up the test generation process. Schulz, Trischler, and Sarfert [57] presented a unique sensitization method and an improved multiple backtrace method to further improve the performance of FAN. Their system, called SOCRATES, improved the implication procedure.

In these structural methods, backtracking, which is a branch procedure terminated by a bound step, is the most computationally expensive step in the process of searching for a test vector. The branching step goes as deep in the binary search tree as possible, while the bound step backs up in the binary search tree to the most recent node with an unused alternative assignment.

### 2.1.2 Algebraic Methods

Instead of performing a search on a data structure representing a circuit. algebraic methods produce an equation describing all possible tests for a particular fault and then simplify the resulting equation. A typical algebraic method is the Boolean difference method, proposed by Sellers et al. [58]. Once the Boolean difference formula for the testing problem is obtained, it is simplified by using the basic laws of Boolean algebra or using identities specific to the Boolean difference. The tedious nature of the algebraic manipulations involved in solving formulae using the Boolean difference led to its disfavor as a practical tool for test pattern generation [40].

Recently. Larrabee [32] proposed a Boolean satisfiability (SAT) method for generating test vectors for single stuck-at faults in combinational circuits. This new method generates test vectors in two steps. First, it constructs a formula expressing

the Boolean difference between the fault-free and faulty circuits. Secondly, instead of performing symbol manipulation, it applies a SAT algorithm to satisfy the formula. This method has, in practice, produced good results for the problem of combinational circuit test generation. Many existing SAT algorithms can be used to solve large size SAT formulas [20, 21, 24, 26].

Later. Chakradhar. Agrawal. and Rothweiler [9] developed a transitive closure algorithm for combinational circuit test generation. A Boolean difference equation is derived from the model of the circuit incorporating necessary conditions for fault activation and path sensitization and then a test vector is obtained by determining signal values that satisfy the equation. The method consists of two main steps that are repeatedly executed: transitive closure computation and decision-making. The transitive closure contains global pairwise (or binary) logical relationships among all signals. Higher-order signal relationships are represented as additional ternary and M-ary (M>3) relations. A key feature of the algorithm is that signal dependencies derived from the transitive closure are used to reduce ternary relations to binary relations that in turn dynamically update the transitive closure. The signals are either determined from the transitive closure or are enumerated until the Boolean equation is satisfied.

An efficient ATPG system for combinational circuits has been implemented in SIS [59]. It consists of two parts: random test generation and deterministic test generation, which is based on the algorithm reported in [32]. Both fault equivalence and fault dominance are used to reduce the fault list.

Cox and Rajski [15] developed a mathematical basis for the identification of necessary and nonconflicting assignment. The algorithmic assignment identification can be used to reduce or eliminate backtracking.

## 2.2 Overview of Test Generation for Sequential Circuits

Though adequate test generation systems exist for combinational circuits. the same cannot be said for sequential circuits. The major difficulty in test generation for sequential circuits is that the outputs of a sequential circuit depend not only on the primary input vectors but also on the present states of the circuit.

The earlier algorithms modeled sequential circuits as iterative combinational circuits. Some test generation algorithms for combinational circuits were extended to test sequential circuits [31, 41]. An algorithm based on this method has been programmed into a commercial package called LASAR [61]. Several approaches [36, 60] based on extensions of the classical D-algorithm were presented to solve the test generation problem for sequential circuits. Shteingart. Nagle. and Grason [60] gave an efficient technique for modeling sequential components. Although some progress was made in these attempts, an effective solution for circuits with more than a few hundred gates and large sequential depths was not available at that time.

Due to the relative ineffectiveness of these ATPG systems, many large digital systems are being designed in compliance with design-for-testability rules which attempt to reduce the complexity of the test problem. The objective of design-for-testability is to provide guidelines which ensure the creation of testable designs. A popular approach is to make the memory elements controllable and observable, i.e., a scan design [1]. The flip-flops and/or latches are designed to be able to operate in either parallel load or serial shift mode. In the normal mode of operation, flip-flops and latches are configured for parallel load. The flip-flops are switched to a serial shift mode for testing purposes. In serial mode, any needed test values can be loaded by serially shifting in the desired values. In a similar fashion, any values in the flip-flops can be observed by shifting out their contents while in the serial shift mode.

Scan design approaches have been successfully used to reduce the complexity of the problem of sequential circuit test generation by transforming the problem into one of combinational circuit test generation. However, in some cases, the cost in terms of area and/or performance and/or extra numbers of I/O pins is unaffordable.

For sequential circuit test generation, some progress has been made in the past several years. A heuristic, simulation-based test generation algorithm was presented by V.D. Agrawal, K.-T Cheng, and P. Agrawal [2]. At first, initialization sequence is generated to bring flip-flops to known states. Then, test generation for a group of faults and a single fault is performed separately. All functions are accomplished through a simulator using different cost functions. Vectors are generated to minimize the cost.

Ma. Devadas. Newton. and Sangiovanni-Vincentelli [35] described a PODEM-based deterministic approach to sequential circuit test generation, called STALLION. It first extracts a partial state transition graph (STG) of a sequential circuit. The construction of the partial STG is based on an efficient state-enumeration algorithm that aims at finding paths from the reset state to different valid states (states reachable from the reset state) in the STG. Then test sequences for line stuck-at faults can be generated using the two-phase ATPG system: fault excitation and propagation. and state justification.

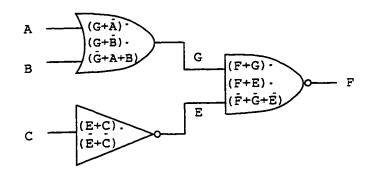

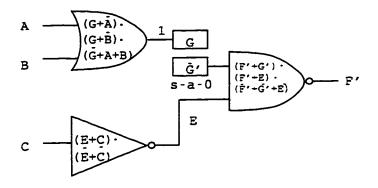

Later, a new system, STEED, was proposed by Ghosh. Devadas, and Newton [18] to improve STALLION. STEED decomposes the problem of sequential circuit test generation into three subproblems: excitation vector generation, state justification, and state differentiation. Given a fault under test, it first generates a combinational excitation vector that propagates the effect of the fault to the primary outputs or the next state lines. Combinational excitation vector generation is based on a PODEM-

like algorithm. A justification step is then performed to find a justification sequence for the excitation state. This step is carried out using a sequence of cube intersections on the complete or partial ON/OFF sets of the next state lines. If the effect of the fault has been propagated to the next state lines alone, the true-faulty state pair is generated by the excitation vector. A differentiation sequence for this true-faulty state pair is obtained using another sequence of cube intersections on the ON/OFF sets of the primary outputs. The three-phase ATPG system is shown to be an efficient method. STEED significantly improved STALLION in terms of computing time for the same fault coverage. Random test generation has been used as a front end of deterministic test generation. Therefore, random seed has effects on the performance of the random test generation.

Cho. Hachtel, and Somenzi [12] have recently given an efficient algorithm. VERITAS for sequential circuit test generation. VERITAS is based on implicit state enumeration and a three-phase ATPG. The approach identifies sequential redundancies through reachability analysis of sequential circuits. It constructs the product machine of two sequential circuits to be compared. Reachability analysis is performed by traversing the finite state machine to find any difference in I/O behavior. When an output difference is detected, the information obtained by reachability analysis is used to generate a test sequence. As the product machine traversal (PMT) is quite resource-demanding, a three-phase ATPG system is used first to deal with most of the faults. PMT is used only for the faults for which the three-phase ATPG fails to generate test sequences. VERITAS further improved STEED in terms of running time, test vector length, and fault coverage. It is difficult, however, for VERITAS to handle large size sequential circuits.

These approaches above are capable of generating tests for sequential circuits with

1000-3000 gates. Due to the difficulty of test generation for sequential circuits. significant improvements are needed for very large scale sequential circuits.

Niermann and Patel [42] presented HITECT. a sequential circuit test generator without a reset state. A targeted D element technique is used to increase the number of possible mandatory assignments and reduce the over-specification of state variables. The state knowledge of previously generated vectors for state justification, without the memory overhead of a state transition diagram. is presented.

Lee and Sajula [34] presented a PODEM-based algorithm for sequential circuits. called FASTEST. The iterative array model and nine-valued logic are used. Each iteration is called a time-frame. The FASTEST algorithm determines the number of time-frames required to find a test for a fault and then expends time-frames based on the state of test generation failure.

Prinetto. Rebaudengo, and Reorda [48] developed a genetic-based algorithm. GATTO. for very large sequential circuits. The algorithm starts with a number of random generated sequences. Two operators are used in evolution process: cross-over and mutation. The cross-over operator selects two parent sequences and builds a new sequence composed of the first  $x_1$  vectors of the first sequence and the last  $x_2$  vectors of the second sequence (here  $x_1$  and  $x_2$  are two random numbers). The mutation operator randomly selects a sequence and complements a single bit within it.

Chen and Bushnell [11] proposed a test generator (SEST) for sequential circuits. They observed that test generation for different faults may share identical justification decision sequences represented by identical decision spaces. Since justification decomposition represents the collective effects of prior justification decisions. it is used to identify previously explored justification decisions.

Test cultivation is used for generating test vectors for both combinational and sequential circuits [56]. This method is based on continuous mutation of a given input sequence and on analyzing the mutated vectors to select the test set. The test cultivation algorithms are simulation-based and a test set can be cultivated for any circuit which can be simulated logically.

Marchok, EI-Maleh, Maly, and Rajski [37] investigated the complexity of sequential ATPG systems. Three sequential circuit test generators are used in the investigation. It is found that an circuit attribute, termed density of encoding, is a key indicator of the complexity of structural, sequential test generation. Density of encoding is the fraction of the total number of possible states which are valid.

Pomeranz and Reddy [45] analyzed undetectable and redundant faults in sequential circuits. Faults are classied into three sets: detectable, partially detectable, and operationally redundant. The last two classes are dependent on the operation mode of the circuit. Partially detectable faults are the fault for which a test sequence does not exist; however, under certain initial conditions (or initial states) of the circuit, faulty behavior may be observed. The notion of redundancy cannot be separated from the operation mode of the circuit. Two operation modes are considered: synchronization mode and free mode.

Recently, hybrid sequential circuit test generation methods are often adopted. Rudnick and Patel [54] combined deterministic algorithms for fault excitation and propagation with genetic algorithms for state justification. Deterministic algorithms for state justification are used if the genetic approach is failed, so it allows for identification of untestable faults and to improve the fault coverage. Hsiao, Rudnick, and Patel [27] developed an ATPG system for sequential circuits, called ALTTEST, where two phases of test generation are used. The first phase uses a simulated-based genetic

algorithm and the second phase uses a deterministic algorithm HITEC.

## 2.3 Overview of Test Compaction

Test compaction is very important in test generation for both combinational circuits and sequential circuits. since it allows reduction in test application time and test vector storage requirements of VLSI testers. The test compaction process can be performed either statically or dynamically. In static compaction, the merging process is performed after the test generation phase is completed. In dynamic compaction, test vectors are merged during the test generation phase.

Several combinational and sequential test generators aimed at generating small test sets for the stuck-at fault model have been developed. I. Pomeranz, L.N. Reddy, and S.M. Reddy [44] presented two test vector compaction methods for combinational circuits: maximal test compaction and rotating backtrace in COMPACTEST. Maximal test compaction unspecifies some primary input values specified as 1 or 0 in a test vector for a fault, even if the resulting vector is not a test vector for the fault. The rotating backtrace increases the potential of detecting additional faults by selecting different paths for backtracing.

L.N. Reddy, I. Pomeranz, and S.M. Reddy [51] developed the COMPACTEST-II system to generate compact test sets for combinational circuits. Single transition and CMOS stuck-open faults are considered. Vectors for different faults are dynamically overlapped, either fully or partially, to reduce the test set size. In ROTCO [52], the test vectors are processed in reverse order of generation. Test vectors are allowed to be modified in the detection of faults detected by earlier vectors and the test vector length is reduced.

Kajihara, Pomeranz, Kinoshita, and Reddy [30] presented a cost-effective method

for finding maximum independent fault sets in combinational circuits. A dynamic fault ordering technique was introduced using independent fault sets and a double technique that leads to the minimal test sets. Later, they [29] compacted test vectors for stuck-at faults in combinational circuits by addition and removal of test vectors. Each test vector which is added to the test vectors allows the removal of two or more test vectors. Aourid and Kaminska [4] proposed a neural network method for the set covering problem, which can be applied to the test compaction for combinational circuits.

Test vector compaction for sequential circuits is significantly more difficult than for combinational circuits. Based on sequential testability and iterative model. Ben-Hamida. Kaminska. and Savaria [5] discussed a pseudo-random vector compaction technique for sequential circuits in order to conserve the sequences of vectors that detect faults. Sequential testability measures are used to predict the optimum amount of circuit duplication which is used in test compaction.

Raghunathan and Chakradhar [49] present several accelerating techniques for dynamic test compaction for sequential circuits. These techniques are based on the identification of support sets, target fault switching, and use of dynamic equivalent and untestable fault analysis. They [10] also proposed a dynamic vector compaction and test cycle reduction algorithm to identify bottlenecks that prevent compaction and cycle reduction.

Niermann. Roy. Patel, and Abraham [43] used the compatibility of test sequences to compact test vectors for sequential circuits. The compaction technique has effect on the original fault coverage.

Pomeranz and Reddy [46] presented a procedure to generate short test sequences

for sequential circuits by selecting one input combination at a time. The procedure switches between a fault-independent phase and a fault-oriented phase. Later. they [47] used some static compaction techniques, such as omission and insertion, to do dynamic test compaction for sequential circuits.

### 2.4 Summary

Up to now, some well-known test generation algorithms for combinational circuits have been developed and perform well for certain circuit structures. Existing ATPG systems for combinational circuits fall into two classes: structural and algebraic methods. Both Boolean satisfiability and transitive closure methods have produced good results on popular test pattern generation benchmarks [32, 9].

For sequential circuit test generation, some progress has been made in the past several years [18, 42, 12, 11]. The three-phase ATPG system is shown to be an efficient method. Due to the difficulty of test generation for sequential circuits, significant improvements are needed for very large scale sequential circuits.

Test compaction is an important part in an ATPG system for both combinational and sequential circuits. There are two kinds of methods to perform test compaction: static and dynamic test compaction [51, 30, 49].

### CHAPTER 3

### **PRELIMINARIES**

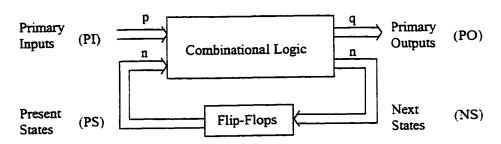

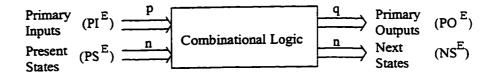

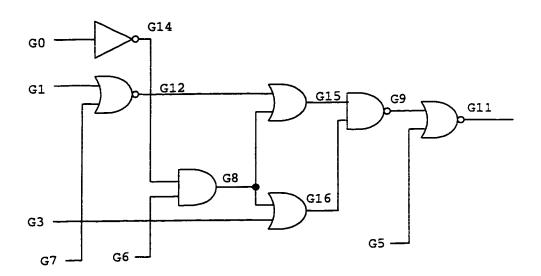

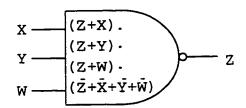

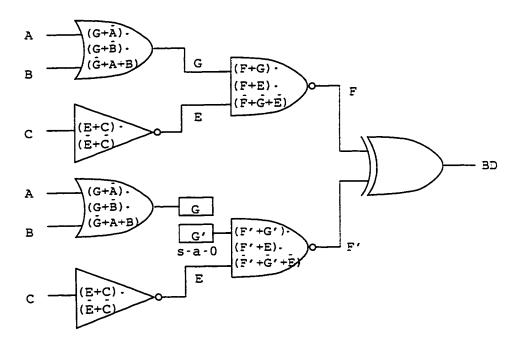

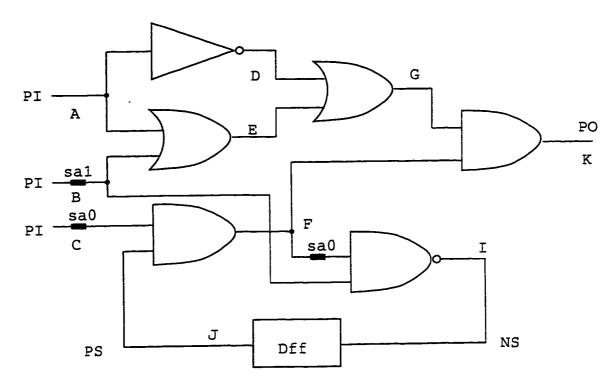

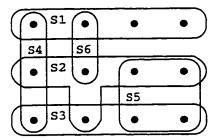

In this chapter, common terminology related to test generation is introduced. A sequential circuit is shown in Figure 3.1. The circuit consists of a combinational

Figure 3.1. A sequential circuit.

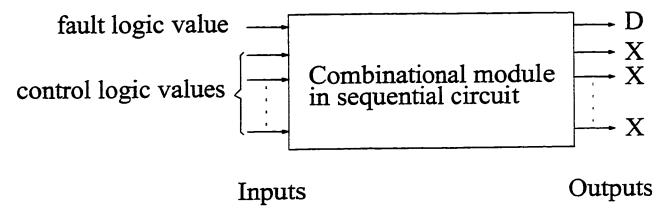

logic block and some feedback flip-flops. The inputs and outputs of flip-flops are the next state and present state lines, respectively. There are p primary inputs, n present state lines, n next state lines, and q primary outputs. The primary outputs are the functions of the primary inputs and present state lines. It is assumed that the present state and next state lines are neither controllable nor observable. The goal of test generation for sequential circuits is to find primary input sequences which can propagate the faults in the sequential circuit to the primary outputs.

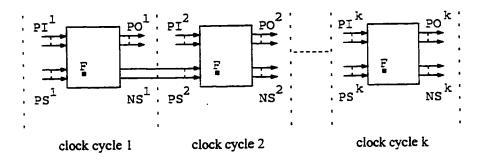

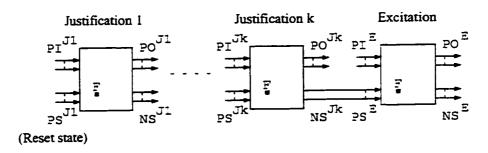

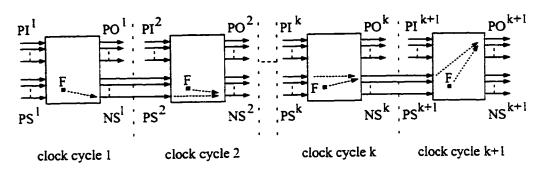

A conventional iterative array model [7], as shown in Figure 3.2. is used to illustrate the test generation process of sequential circuits. The iterative array in

Figure 3.2. An equivalent pseudo-combinational iterative array to the sequential circuit in Fig. 2.1.

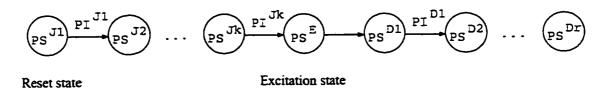

Figure 3.2 is logically equivalent to the sequential circuit shown in Figure 3.1. If an input sequence  $PI^1$ ,  $PI^2$ , ...,  $PI^k$  is applied to the sequential circuit in initial present state  $PS^1$ , it generates a primary output sequence  $PO^1$ ,  $PO^2$ , ...,  $PO^k$  and the next state sequence  $NS^1$ ,  $NS^2$ , ...,  $NS^k$  ( $PS^{i+1} = NS^i$ ,  $1 \le i < k$ ).

Assume there is a fault, F, in the combinational logic block of the sequential circuit shown in Figure 3.1. The combinational block is duplicated in terms of each clock cycle, i.e., time-frame. Two iterative array models are considered in test generation: the fault-free and faulty array models. In the faulty array model, the fault under test exists in every time frame. The behavior difference between the fault-free and faulty array models is the effect of the fault on the primary outputs, since other nodes besides the primary outputs are neither observable nor controllable. The fault is propagated to the primary output along a sensitized path through each time frame.

**Definition 3.1** Beginning with the present state in clock cycle 1.  $PS^1$ , we set the reset state values and wish to produce a primary input sequence.  $PI^1$ .  $PI^2$ . ....  $PI^k$ . which, when applied to clock cycles  $1, 2, \dots, k$ , propagates the effect of the fault F to the primary outputs,  $PO^k$ , during the kth clock cycle. This primary input sequence is called a *test sequence* for the fault.

Unlike combinational circuits, where only one input test vector is needed to test a fault, a sequential circuit may require a test sequence of up to  $2^{n+1}$  input test vectors, where n is the number of memory elements (flip-flops) in the sequential circuits [7].

In sequential circuit testing, a state is a bit vector. Its length is equal to the number of memory elements in the sequential circuit. In general, a state is a cube, i.e., the values at the different bit positions may be 0.1 or X (don't care). A minterm state is a state with only 0's or 1's as bit values. A cube state is a group of minterm states. A universal cube is a cube with all X entries.

**Definition 3.2** State  $S_1$  implicates state  $S_2$ , if and only if, every state contained in  $S_1$  is also contained in  $S_2$ . That is, state  $S_2$  covers state  $S_1$ .

For example, state (1, 0, 0) is a minterm state, and state (1, 0, X) is a cube state. There are two minterm states (1, 0, 0) and (1, 0, 1) in the state (1, 0, X), so state (1, 0, 0) implicates state (1, 0, X), (X, X, X) is a universal cube.

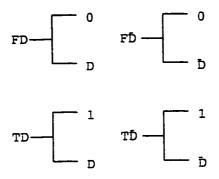

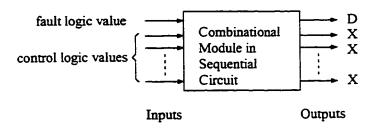

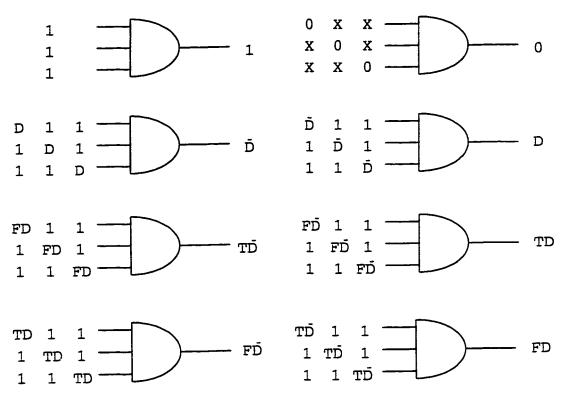

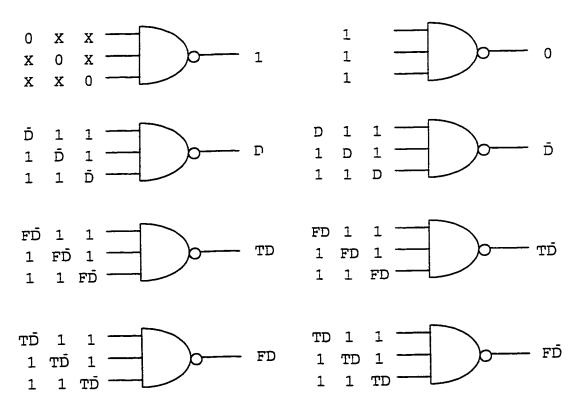

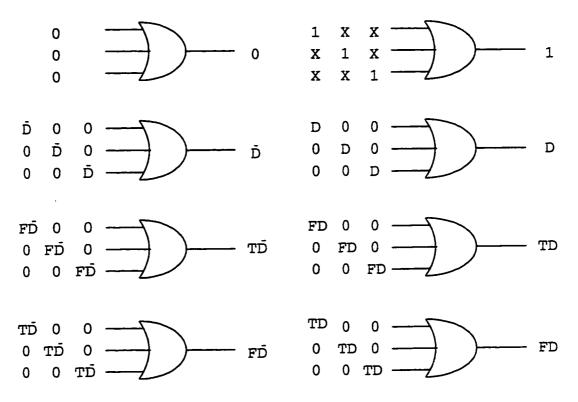

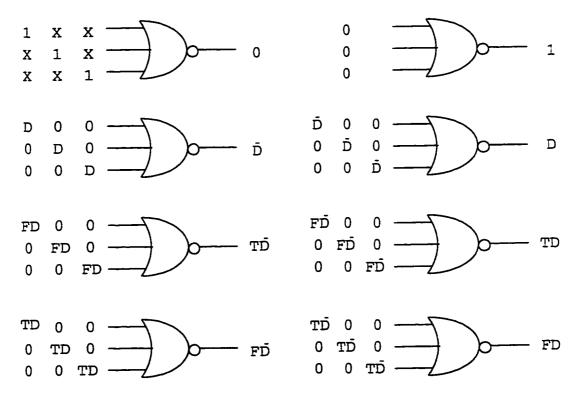

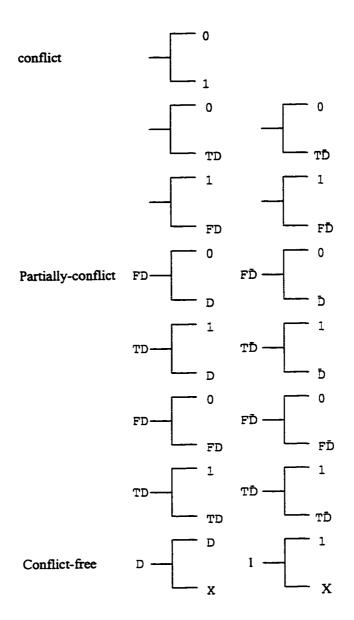

A nine-value logic  $(0. 1. X. D. \overline{D}. FD. F\overline{D}. TD. T\overline{D})$  is used to describe the circuit behavior. The logic value D represents a logic value 1 for a node in a fault free circuit and a logic value 0 for the same node in the faulty circuit. The logic value  $\overline{D}$  is the complement value of D. The logic value FD is the consistent value of the logic value D and the logic value D. The logic value D is the consistent value of the logic value D and the logic value D. The logic value D is the consistent value of the logic value D and the logic value D and

**Definition 3.3** The logic values 0, 1, and X are referred to as the *control logic values*. The logic values  $D, \overline{D}, FD, F\overline{D}, TD, T\overline{D}$  are referred to as the *fault logic values*.

Figure 3.3. The meaning of logic values FD,  $F\overline{D}$ , TD,  $T\overline{D}$ .

The sequential circuits discussed here are assumed to have a reset state. All test sequences are applied to the sequential circuit with the reset state as the starting state. Some faults in the circuit may be redundant, i.e., their existence does not change the behavior of the circuit. There are two kinds of redundant faults. combinational redundant and sequential redundant.

**Definition 3.4** A combinational redundant fault is a fault which cannot be propagated to the primary outputs or the next state lines, beginning from any state, with any input vector.

**Definition 3.5** A sequential redundant fault is a fault which cannot be excited or whose effect cannot be propagated to the primary outputs using any sequence of input vectors starting from the reset state.

Definition 3.6 An excitation vector for a fault is a test vector that propagates the fault to either the primary outputs or the next state lines. The test vector consists of two parts, the primary input and the present state. The present state part of an excitation vector is called an excitation state. The primary input part of an excitation vector is an excitation input.

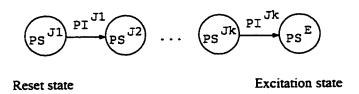

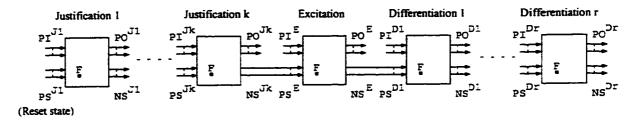

**Definition 3.7** The process of finding a primary input sequence which takes a circuit from the reset state into the excitation state is called *state justification*. The corresponding input sequence is a *justification sequence*.

There are two kinds of state justification. forward state justification and backward state justification. In forward state justification, the search is done from the reset state to the excitation state; and vice versa for backward state justification. Usually, backward state justification is used to perform state justification. If the excitation vector propagates the fault to the next state lines, state differentiation is required.

**Definition 3.8** State differentiation is the process of propagating the effect of a fault on the next state lines to the primary outputs. A differentiation sequence for a pair of states, fault-free state  $S^T$  and faulty state  $S^F$ , which differ in at least one bit, is a primary input sequence such that, if the circuit is initially in  $S^T$ , the last vector in the sequence produces a different logic value in at least one primary output than if the circuit were initially in  $S^F$ .

In sequential circuit test generation, the complete test sequence is obtained by combining the justification sequence, the excitation vector, and the differentiation sequence.

**Definition 3.9** When all flip-flops in a sequential circuit are disabled, the sequential circuit becomes a *pseudo-combinational* circuit. The primary inputs and present state lines are considered as the inputs of the pseudo-combinational circuit. The primary outputs and next state lines are the outputs of the pseudo-combinational circuit.

A general pseudo-combinational circuit is shown in Figure 3.4.

Figure 3.4. A general pseudo-combinational circuit is obtained from the corresponding sequential circuit by disabling all flip-flops.

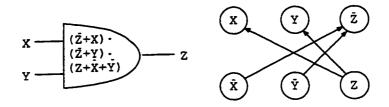

Definition 3.10 The *input cone* of a primary output is a portion of a circuit which includes the primary output and its subtree from the primary output to the primary inputs and present state lines. Any fault site in this subtree is a *node* in the input cone. The *input cone* of a next state line is a portion of a circuit which includes the next state line and its subtree from the next state line to the primary inputs and present state lines. The *input cone* of a node is a portion of a circuit which includes the node and its subtree from the node to the primary inputs and present state lines. The *size* of a node is the number of nodes in its input cone.

The concept of the input cone is suitable for any node in a circuit and includes the input cones of primary outputs and next state lines.

**Definition 3.11** Assuming a fault site in the circuit is a node in the input cones of r primary outputs, the input cones of these r primary outputs are referred to as the primary output fault region for the fault under test. Similarly, if a fault site in the logic circuit is a node in the input cones of s next state lines, the input cones of these s next state lines compose the next state fault region for the fault under test.

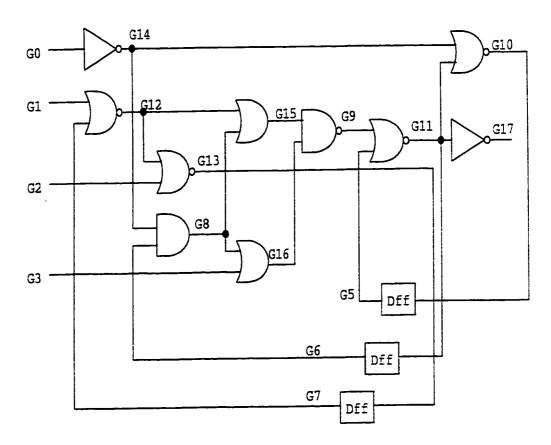

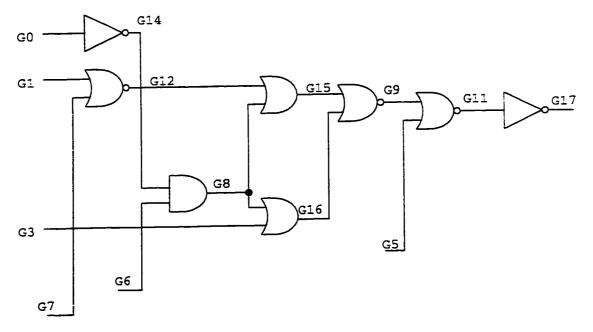

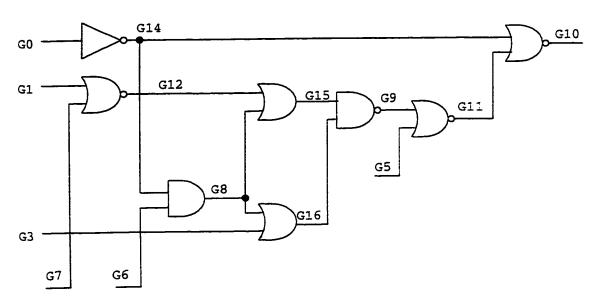

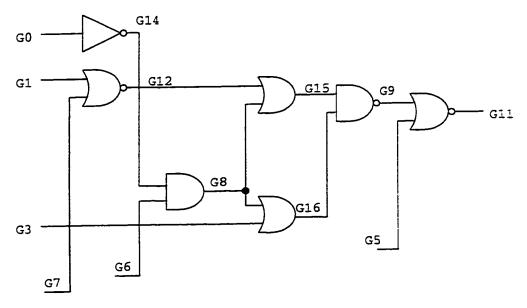

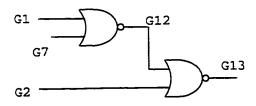

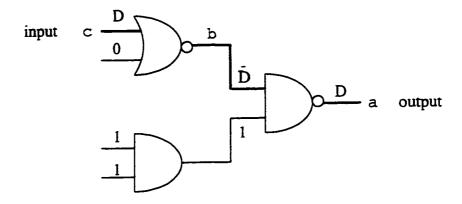

To illustrate the idea of an input cone. consider a simple sequential circuit s27 from the ISCAS'89 benchmarks, as shown in Figure 3.5. There is only one primary output G17, and its input cone is shown in Figure 3.6. There are three next state lines G10, G11, and G13. The input cones of the next state lines G10, G11, and G13 are shown in Figure 3.7 - 3.9. Consider a fault on G15. Since G15 is a node in the input cone of the primary output G17, its primary output fault region is the same as the input cone of G17 shown in Figure 3.6. Though G15 is a node in the input cones of the next state lines G11 and G10, if the fault is propagated to G10, it must be propagated to G11 first. Therefore, the next state line G11 only needs to be

Figure 3.5. A sequential circuit s27 from ISCAS'89 benchmarks.

Figure 3.6. The input cone of the primary output G17 in circuit s27.

Figure 3.7. The input cone of the next state line G10 in circuit s27.

Figure 3.8. The input cone of the next state line G11 in circuit s27.

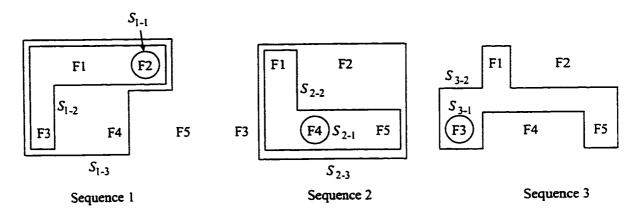

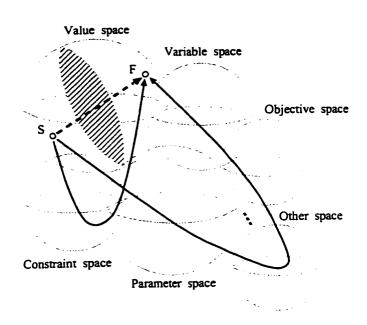

Figure 3.9. The input cone of the next state line G13 in circuit s27.