#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

#### THE UNIVERSITY OF CALGARY

### A Metamorphic Control Architecture for Holonic Systems

by

#### Sivaram Balasubramanian

# A DISSERTATION SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF MECHANICAL ENGINEERING

CALGARY, ALBERTA

SEPTEMBER, 1997

© Sivaram Balasubramanian 1997

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-47923-4

#### **Abstract**

Next generation manufacturing systems are envisioned to be comprised of distributed network of autonomous and cooperative holonic resources. Holonic systems have an information processing part and a physical processing part to process knowledge and material simultaneously. Holonic systems are evolutionary in nature to better accomplish current system objectives. In other words the form and substance of holonic systems undergo constant transformation (metamorphosis) through out their life time. Real time control of such holonic systems requires a radically different approach from that of traditional unit level regulatory control systems.

The control requirements of holonic systems are distributed in nature. The dynamics of distributed control results in complex system behavior and requires an event driven control system. Since holonic systems are evolutionary in nature, they require both static and dynamic reconfigurability of their control systems. Additionally, holonic systems require incorporation of intelligence into their control systems that can enhance autonomy and cooperation. The conventional centralized scan based control systems are inadequate in meeting the said control requirements of holonic systems. This necessitates a new and novel system level distributed control approach, and the control systems based on this approach are termed as metamorphic control systems.

The engineering of such software centric metamorphic control systems for dynamically reconfigurable distributed multi-sensor based holonic systems, is addressed in this dissertation. An integrated and uniform event driven control architecture is specified for various functional levels of metamorphic control system. The architecture utilizes the emerging International Electrotechnical Commission function block standard (IEC 1499) for industrial process measurement and control systems, to specify the requisite behavior of distributed control software components (agents).

A prototype metamorphic control system has been developed using the new architecture. The core metamorphic control mechanisms have been developed in the form

of a distributed real time operating system. The function block specification is used to develop distributed control software agents and applications. A system engineering interface has been developed for remote program development, configuration and maintenance of distributed control system. The implementation and evaluation details of this prototypical system are presented.

## **Acknowledgements**

First and foremost, I would like to thank my supervisor, Dr. Douglas H. Norrie. for his direction and advice through out this research. I especially appreciate the freedom and flexibility, that led me to explore a relatively new area of research. I also appreciate his efforts for making sure that lack of resources never impeded progress.

I would like to thank my supervisory committee members. Dr. Paul Rogers and Dr. Keith Chrystall, for their suggestions, time and energy during the course of this work.

Special thanks are extended to IEC 1499 Function Block Standards Committee project leader, Dr. James Christensen, for giving me 'inside' information. I gained a lot from the discussions with him and am grateful to him for lending an ear.

I thank our technical supervisor, Nick Vogt, for his help in obtaining equipment and other resources for this research.

I am grateful to our technician, David Genge, for his help in developing special hardware used in this research.

I am also thankful to our graduate secretary. Lynn Banach, and division secretary. Karen Undseth, for their help during this research.

I am indebted to my colleagues, Harish Ananda Rao and Francisco Paul Maturana for their help and invigorating discussions.

I am also privileged to have many good friends who have helped me in one way or the other. Thanks to you all.

Words cannot describe my gratitude adequately, to my beloved parents and family members for their encouragement and support, without which this endeavor would not have been possible.

Dedicated to my beloved parents.

# **Table of Contents**

| Approval Page                                 | ii   |

|-----------------------------------------------|------|

| Abstract                                      | ii   |

| Acknowledgements                              |      |

| Dedication                                    | vi   |

| Table of Contents                             | vü   |

| List of Tables                                | xii  |

| List of Figures                               | xiii |

| Acronyms                                      |      |

| Glossary                                      | xvii |

| Chapter 1 - Introduction                      |      |

| 1.1 Overview                                  |      |

| 1.2 Holonic Systems                           | 2    |

| 1.3 Motivation                                | 4    |

| 1.4 Objectives                                | 6    |

| 1.5 Organization of Dissertation              | 6    |

| Chapter 2 - Industrial Automation and Control | 8    |

| 2.1 Introduction                              |      |

| 2.2 Industrial Control Systems                | 8    |

| 2.2.1 Programmable Logic Control Systems      |      |

| 2.2.2 Process/Loop Control Systems            |      |

| 2.2.3 Distributed Control Systems             | 12   |

| 2.2.4 Computer Numerical Control Systems      | 13   |

| 2.2.5 Robot Control Systems                   |      |

| 2.3 Factory Floor Communications              | 14   |

| 2.3.1 Manufacturing Automation Protocol       | 15   |

| 2.3.2 Field Level Networks                    | 17   |

| 2.4 Open Architecture Control                 |      |

|     | 2.4.1 Open Modular Architecture Controller                             | . 20      |

|-----|------------------------------------------------------------------------|-----------|

|     | 2.4.2 Open Systems Architecture for Controls within Automation Systems | . 23      |

|     | 2.4.3 Open System Environment for Controller                           | . 25      |

|     | 2.4.4 Enhanced Machine Controller                                      | . 27      |

|     | 2.4.5 University of Michigan Open Architecture Controller              | . 29      |

|     | 2.4.6 Machine tool Open System Advanced Intelligent Controller         | . 31      |

|     | 2.4.7 Other Open Architecture Control Approaches                       | . 32      |

| 2.  | 5 Summary                                                              | 34        |

| Che | apter 3 - Holonic Systems Control                                      | 35        |

| 3.  | 1 Introduction                                                         | 35        |

| 3.  | 2 Metamorphic Control Requirements                                     | 35        |

|     | 3.2.1 Real Time Control                                                | . 37      |

|     | 3.2.2 Distributed Control                                              | . 39      |

|     | 3.2.3 Event Driven Control                                             | 42        |

|     | 3.2.4 Intelligent Control                                              | 43        |

| 3.  | 3 Control Architectures for Autonomous Systems                         | 44        |

|     | 3.3.1 Subsumption Architecture                                         | 45        |

|     | 3.3.2 Other Reactive Architectures                                     | 48        |

| 3.  | 4 Summary                                                              | 50        |

| Cho | upter 4 - A Review of Real Time Systems                                | <i>51</i> |

| 4.  | 1 Introduction                                                         | 51        |

| 4.  | 2 Real Time Operating Systems                                          | <i>51</i> |

|     | 4.2.1 Scheduling                                                       |           |

|     | 4.2.2 Synchronization4.2.2 Synchronization                             | 56        |

|     | 4.2.3 Communication                                                    | 57        |

|     | 4.2.4 Clock Synchronization                                            | 58        |

|     | 4.2.5 Fault Tolerance                                                  | 59        |

|     | 4.2.6 Distributed Real Time Operating Systems                          | 61        |

| 4.  | 3 Formal Specification Methods                                         | 64        |

|     | 4.3.1 Reference Models                                                 | 65        |

|     | 4.2.2 Pagia Function Blocks                                            | 72        |

| 4.3.3 Composite Function Blocks                                |           |

|----------------------------------------------------------------|-----------|

| 4.3.4 Service Interface Function Blocks                        | 76        |

| 4.4 Summary                                                    | 79        |

| Chapter 5 - Metamorphic Control Architecture                   | 80        |

| 5.1 Introduction                                               | 80        |

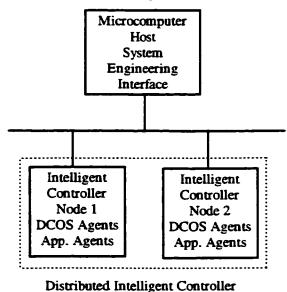

| 5.2 System Architecture                                        | 81        |

| 5.2.1 Distributed Intelligent Controller                       | 83        |

| 5.3 Physical Architecture                                      |           |

| 5.4 Software Architecture                                      | <i>88</i> |

| 5.4.1 Operational Architecture                                 | 88        |

| 5.4.2 Application Architecture                                 | 90        |

| 5.5 Functional Architecture                                    | 91        |

| 5.6 Critical Issues                                            | 93        |

| 5.7 Limitations of Extant Systems                              | <i>97</i> |

| 5.8 Prototype Metamorphic Control System                       | 99        |

| 5.9 Summary                                                    | 100       |

| Chapter 6 - The Distributed Controller Operating System Design |           |

| 6.1 Introduction                                               |           |

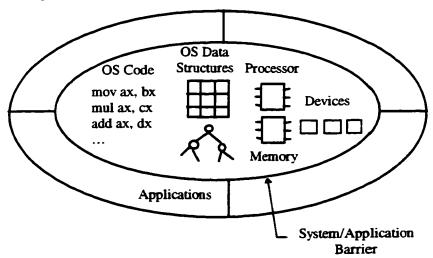

| 6.2 Operating System Concepts                                  | 102       |

| 6.2.1 Types of Operating Systems                               |           |

| 6.3 Operating System Design Techniques                         | 107       |

| 6.3.1 Uninterruptable Monitor Approach                         |           |

| 6.3.2 Kernel Approach                                          | 109       |

| 6.3.3 Layered Approach                                         | 110       |

| 6.3.4 Message Passing Approach                                 | 112       |

| 6.3.5 Object Based Approach                                    | 113       |

| 6.4 DCOS Architecture                                          | 115       |

| 6.5 Summary                                                    | 122       |

| Chapter 7 - The DCOS Implementation                            | 123       |

| 7.1 Introduction                                               | 123       |

| 7.2 Implementation Details                                     | 123       |

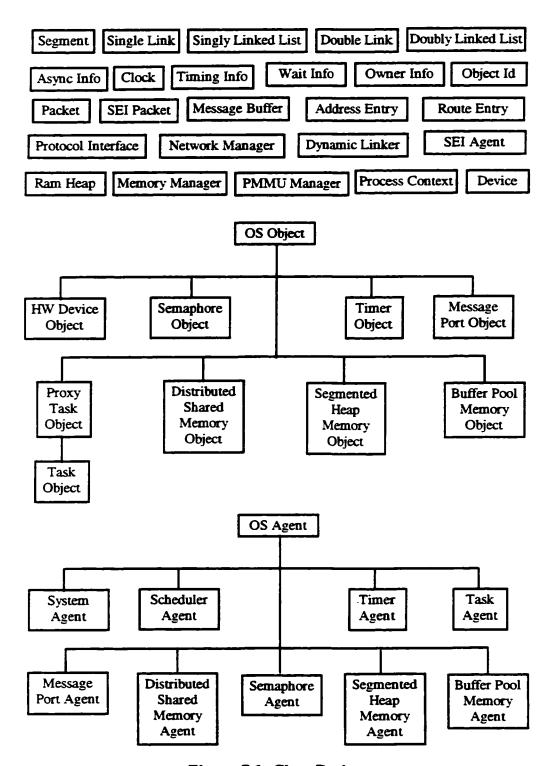

| 7.2.1 Class Design                                    | 125 |

|-------------------------------------------------------|-----|

| 7.2.2 Virtual Memory Management                       | 127 |

| 7.2.3 Hardware Dependencies                           | 128 |

| 7.2.4 Application Interface                           | 129 |

| 7.3 The System Agent                                  | 130 |

| 7.3.1 I/O Devices                                     | 130 |

| 7.3.2 Device Management                               | 133 |

| 7.3.3 Interrupt Management                            | 135 |

| 7.4 The Scheduler Agent                               | 136 |

| 7.4.1 Scheduling Mechanisms                           | 137 |

| 7.4.2 Execution Services                              | 142 |

| 7.5 The Timer Agent                                   |     |

| 7.6 The Task Agent                                    | 145 |

| 7.6.1 Task Services                                   | 147 |

| 7.7 The Buffer Pool Memory Agent                      | 149 |

| 7.8 The Segmented Heap Memory Agent                   |     |

| 7.9 The Message Port Agent                            | 150 |

| 7.10 The Distributed Shared Memory Agent              |     |

| 7.11 The Semaphore Agent                              |     |

| 7.12 The Dynamic Linker                               |     |

| 7.13 The Network Interfaces Manager                   |     |

| 7.14 The System Engineering Interface Agent           |     |

| 7.15 Summary                                          |     |

| Chapter 8 - Application Development and Configuration |     |

| 8.1 Introduction                                      |     |

| 8.2 Software Synthesis                                |     |

| 8.2.1 PID Application                                 |     |

| 8.2.2 Publisher-Subscriber Application                |     |

| 8.2.3 Code Development                                |     |

| 8.3 System Engineering Interface                      |     |

| 8 4 Summary                                           |     |

| Chapter 9 - Implementation and Evaluation              | 172 |

|--------------------------------------------------------|-----|

| 9.1 Introduction                                       | 172 |

| 9.2 System Implementation                              | 172 |

| 9.3 Timing Analysis                                    | 175 |

| 9.3.1 Determinacy                                      | 177 |

| 9.3.2 Interrupt Latency                                | 178 |

| 9.3.3 Context Switch Time                              | 178 |

| 9.3.4 Network Latency                                  | 179 |

| 9.3.5 Service Primitive Times                          | 179 |

| 9.3.6 Methodology                                      | 180 |

| 9.3.7 Performance Data                                 | 181 |

| 9.4 Functionality Tests                                | 185 |

| 9.4.1 Test Case 1                                      | 186 |

| 9.4.2 Test Case 2                                      | 188 |

| 9.4.3 Test Case 3                                      | 189 |

| 9.5 Summary                                            | 192 |

| Chapter 10 - Contributions and Recommended Future Work | 193 |

| 10.1 Summary                                           |     |

| 10.2 Research Contributions                            | 194 |

| 10.3 Future Work                                       |     |

| References                                             | 197 |

# **List of Tables**

| Table 4.1 - Transitions of Event Input State Machine   | 74              |

|--------------------------------------------------------|-----------------|

| Table 4.2 - Transitions of ECC Operation State Machine | 74              |

| Table 9.1 - Qualitative Feature Comparison             | 17 <del>6</del> |

| Table 9.2 - System Agent Primitives                    | 181             |

| Table 9.3 - Scheduler Agent Primitives                 | 182             |

| Table 9.4 - Timer Agent Primitives                     | 182             |

| Table 9.5 - Task Agent Primitives                      | 182             |

| Table 9.6 - Buffer Pool Memory Agent Primitives        | 183             |

| Table 9.7 - Segmented Heap Memory Agent Primitives     | 183             |

| Table 9.8 - Distributed Shared Memory Agent Primitives | 184             |

| Table 9.9 - Message Port Agent Primitives              | 184             |

| Table 9.10 - Semaphore Agent Primitives                | 184             |

| Table 9.11 - Miscellaneous Timing Data                 | 185             |

# **List of Figures**

| Figure 1.1: Holonic Elements and Interfaces                                 | 3  |

|-----------------------------------------------------------------------------|----|

| Figure 1.2: Intelligent Control System                                      | 4  |

| Figure 2.1: Programmable Logic Control System                               | 10 |

| Figure 2.2: Open Modular Architecture Controller                            | 21 |

| Figure 2.3: Elements of OMAC                                                | 22 |

| Figure 2.4: Open System Architecture for Controls within Automation Systems | 24 |

| Figure 2.5: Open System Environment for Controller                          | 26 |

| Figure 2.6: Enhanced Machine Controller Architecture                        | 28 |

| Figure 2.7: University of Michigan Open Architecture Controller             | 30 |

| Figure 2.8: Machine tool Open System Advanced Intelligent Controller        | 31 |

| Figure 3.1: Holonic Distributed Control                                     | 36 |

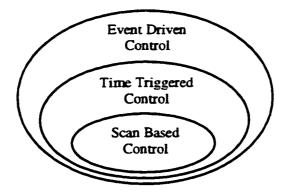

| Figure 3.2: Scan Based and Time Triggered Systems                           | 42 |

| Figure 3.3: Control System Relationships                                    | 43 |

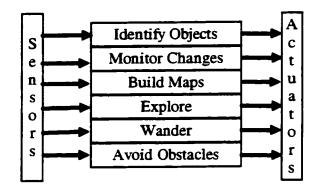

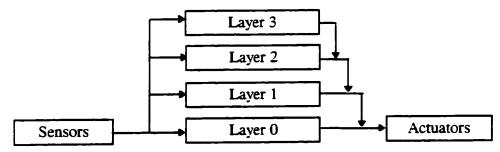

| Figure 3.4: Activity Decomposition                                          | 46 |

| Figure 3.5: Subsumption Layers                                              | 46 |

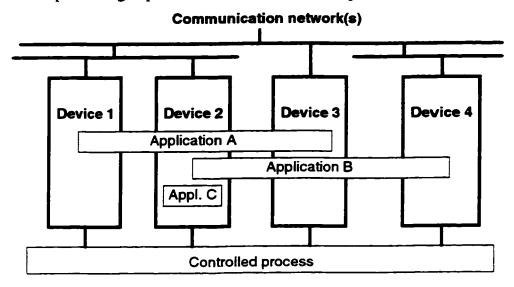

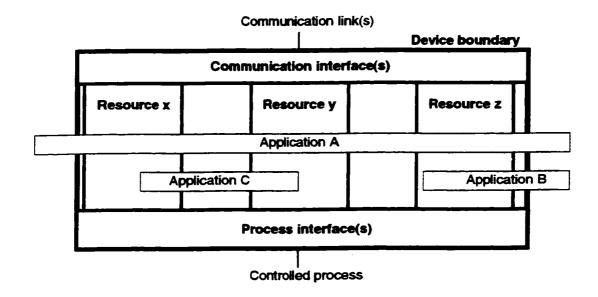

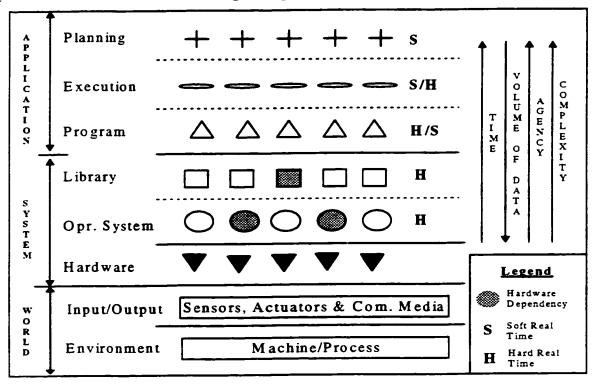

| Figure 4.1: System Model                                                    | 66 |

| Figure 4.2: Device model                                                    | 67 |

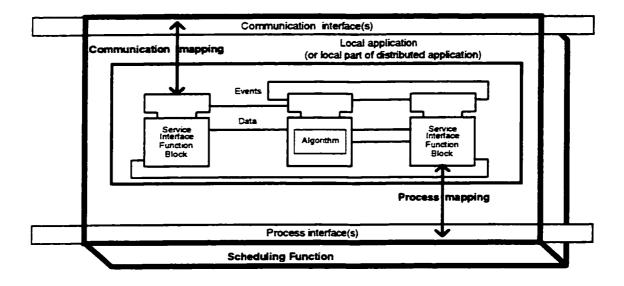

| Figure 4.3: Resource model                                                  | 68 |

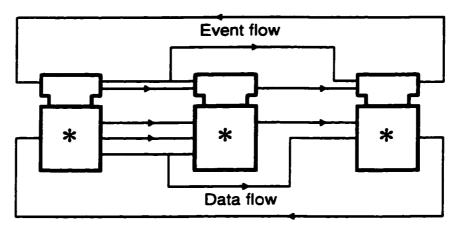

| Figure 4.4: Application model                                               | 69 |

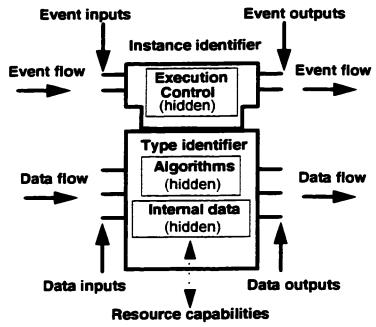

| Figure 4.5: Function Block Model                                            | 70 |

| Figure 4.6: Execution Model and Timing                                      | 70 |

| Figure 4.7: Basic Function Block                                            | 72 |

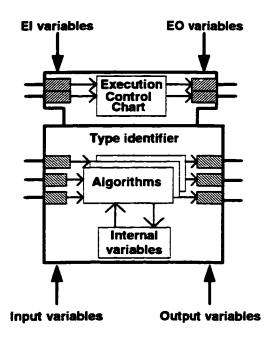

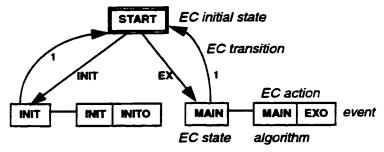

| Figure 4.8: Typical Execution Control Chart                                 | 73 |

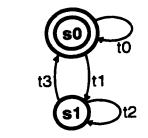

| Figure 4.9: Event Input State Machine                                       |    |

| Figure 4.10: ECC Operation State Machine                                    | 74 |

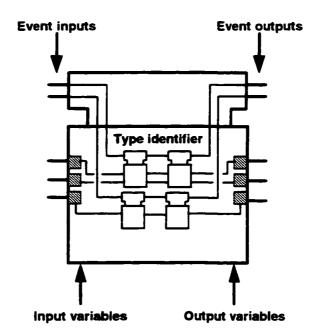

| Figure 4.11: Composite Function Block                                       | 75 |

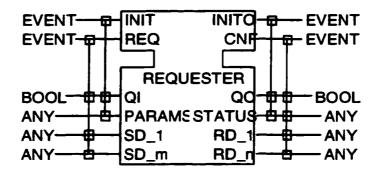

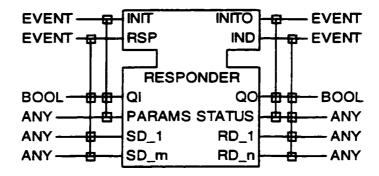

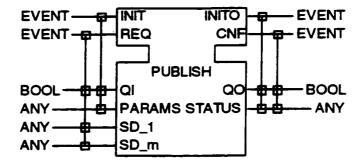

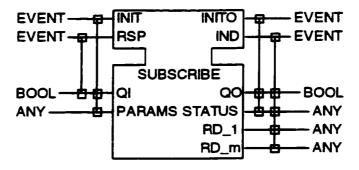

| Figure 4.12: Application Initiated Interaction                              | 77 |

| Figure 4.13: Resource Initiated Interaction      | <i>7</i> 7 |

|--------------------------------------------------|------------|

| Figure 4.14: Unidirectional Requester            | 78         |

| Figure 4.15: Unidirectional Responder            | 78         |

| Figure 4.16: Bidirectional Requester             | 78         |

| Figure 4.17: Bidirectional Responder             | 78         |

| Figure 4.18: Manager Function Block              | 79         |

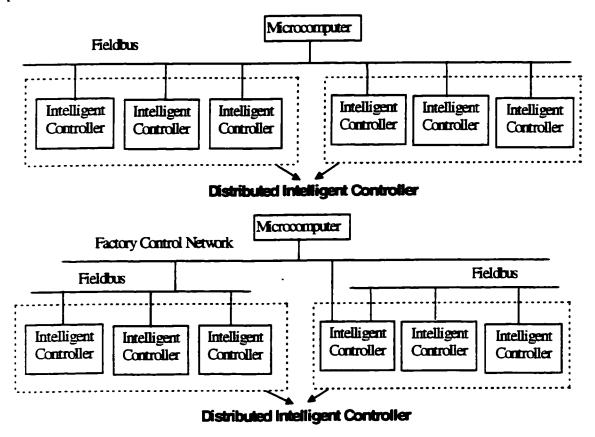

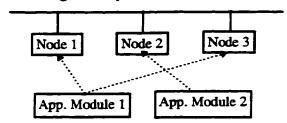

| Figure 5.1: System Architecture                  | 81         |

| Figure 5.2: Feasible System Architectures        | 83         |

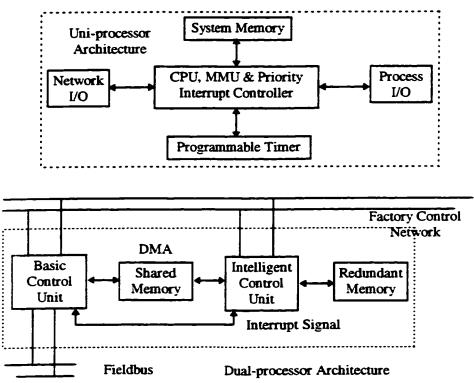

| Figure 5.3: Feasible Physical Architectures      | 86         |

| Figure 5.4: Operational Architecture             | 89         |

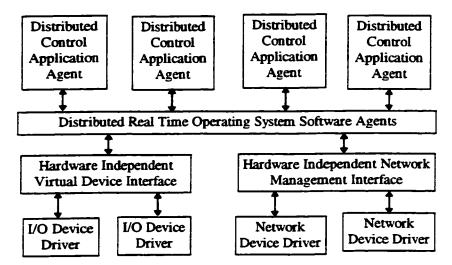

| Figure 5.5: Application Architecture             | 90         |

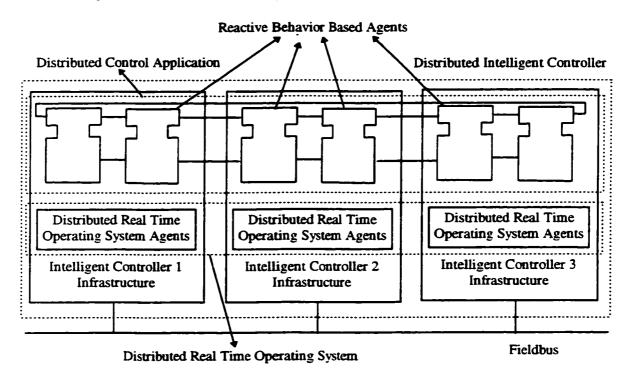

| Figure 5.6: Functional Architecture              | 92         |

| Figure 5.7: Location Transparency                | 94         |

| Figure 5.8: Prototype Metamorphic Control System | 99         |

| Figure 6.1: Conceptual Operating System          | 102        |

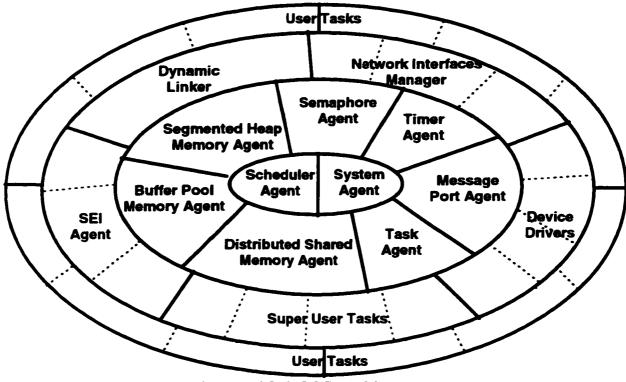

| Figure 6.2: DCOS Architecture                    | 117        |

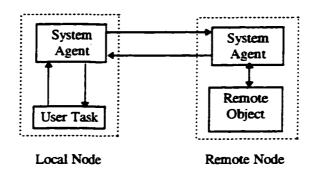

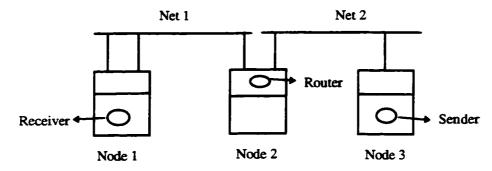

| Figure 6.3: Remote Transaction                   | 120        |

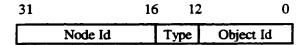

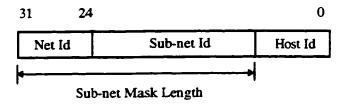

| Figure 6.4: Logical Object Identifier            | 121        |

| Figure 7.1: Class Design                         | 126        |

| Figure 7.2: Virtual Address Space                | 127        |

| Figure 7.3: Virtual Address Translation          | 128        |

| Figure 7.4: Application Interface                | 129        |

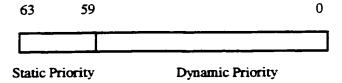

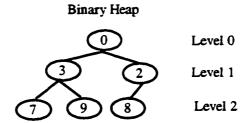

| Figure 7.5: Static Priority Scheduling           | 139        |

| Figure 7.6: Encoded Priority                     | 140        |

| Figure 7.7: Dynamic Priority Scheduling          | 141        |

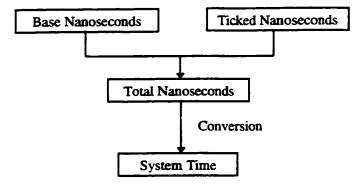

| Figure 7.8: System Clock                         | 143        |

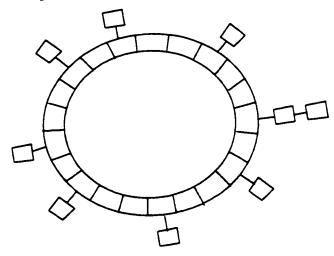

| Figure 7.9: Time Wheel Structure                 | 145        |

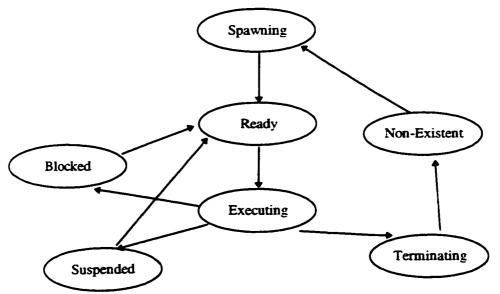

| Figure 7.10: Task State Transitions              | 146        |

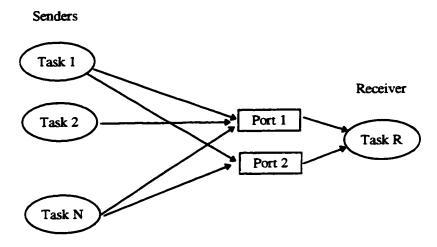

| Figure 7.11: Message Ports                            | 151 |

|-------------------------------------------------------|-----|

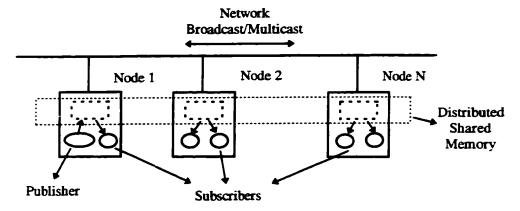

| Figure 7.12: Distributed Shared Memory                | 152 |

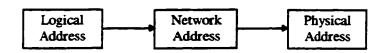

| Figure 7.13: Address Mapping                          | 157 |

| Figure 7.14: Network Address                          | 157 |

| Figure 7.15: Message Routing                          | 158 |

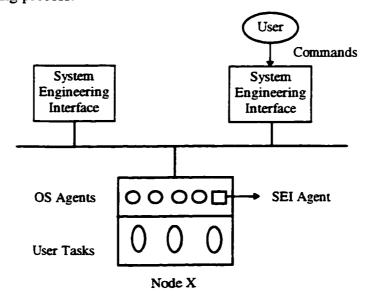

| Figure 7.16: System Engineering Interface Agent       | 159 |

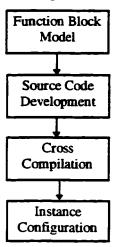

| Figure 8.1: Steps in Application Software Development | 162 |

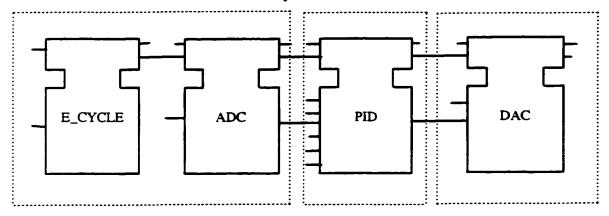

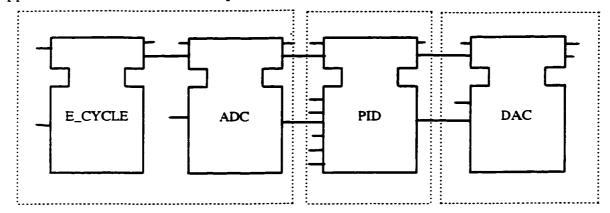

| Figure 8.2: PID Application.                          | 163 |

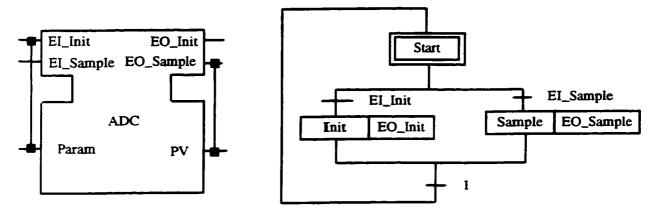

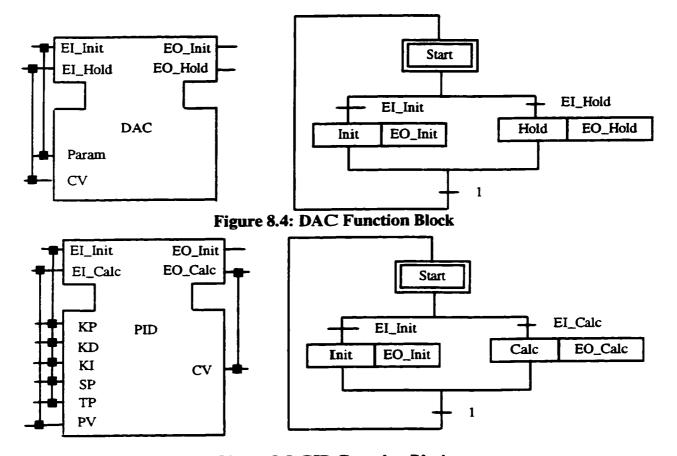

| Figure 8.3: ADC Function Block                        | 164 |

| Figure 8.4: DAC Function Block                        | 164 |

| Figure 8.5: PID Function Block                        | 164 |

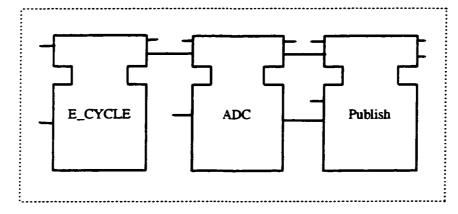

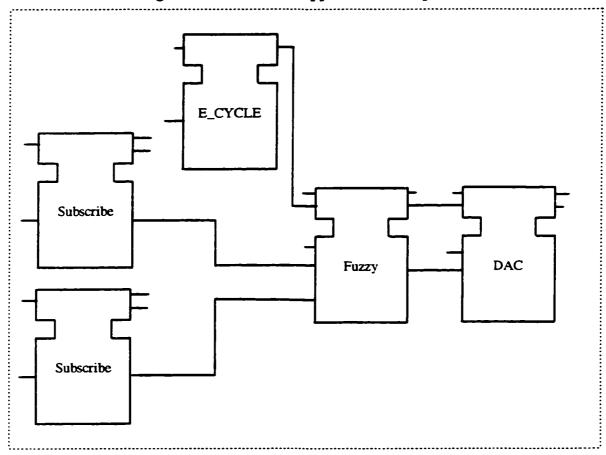

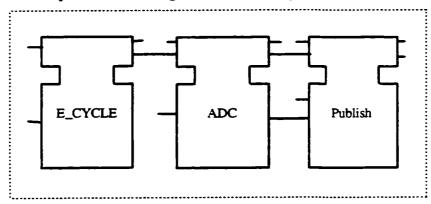

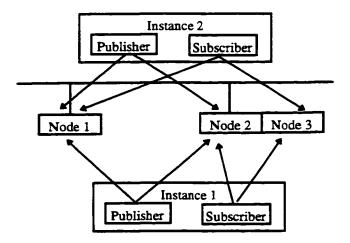

| Figure 8.6: Publisher Application Component           | 166 |

| Figure 8.7: Subscriber Application Component          | 166 |

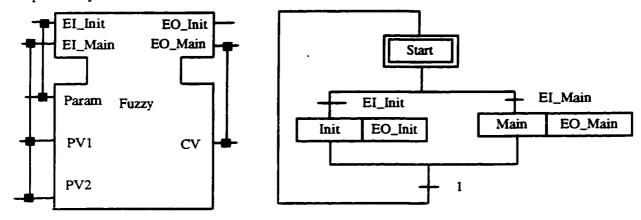

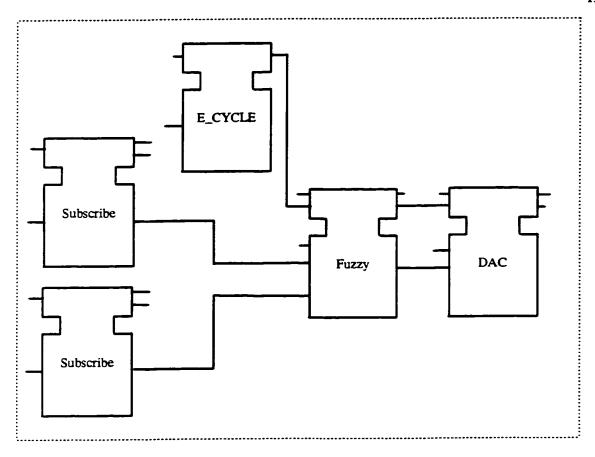

| Figure 8.8: Fuzzy Function Block                      | 167 |

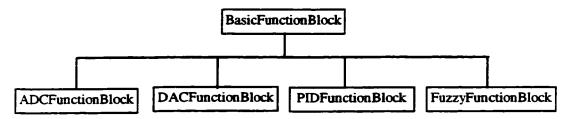

| Figure 8.9: Application Class Design                  | 168 |

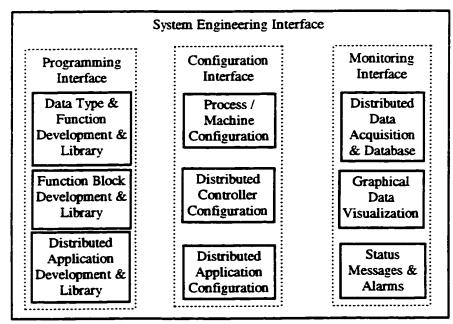

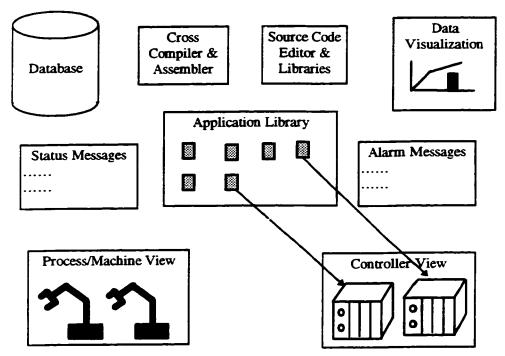

| Figure 8.10: Elements of System Engineering Interface | 169 |

| Figure 8.11: Application Configuration                | 170 |

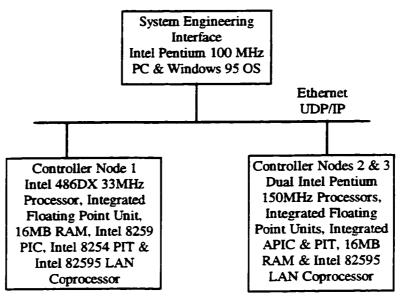

| Figure 9.1: System Implementation                     | 173 |

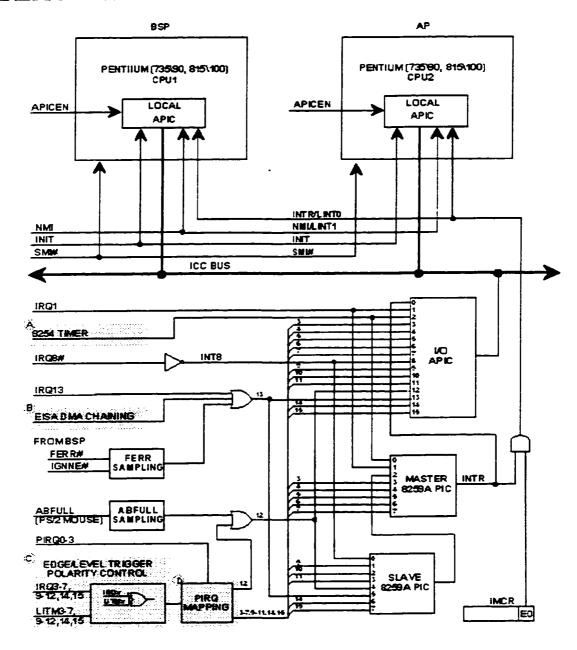

| Figure 9.2: Dual Processor Architecture               | 174 |

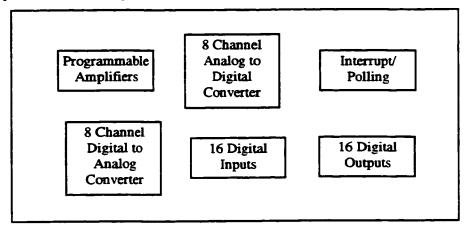

| Figure 9.3: Multi-Function I/O Board                  | 185 |

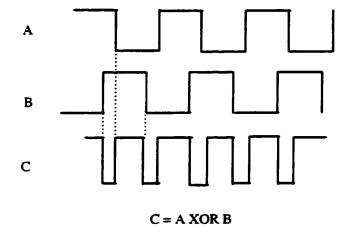

| Figure 9.4: Test Case 1 - Frequency Multiplication    | 187 |

| Figure 9.5: Test Case 1 - Frequency Multiplier        | 187 |

| Figure 9.6: Test Case 2 - PID Application             | 188 |

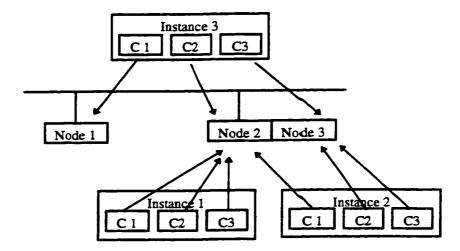

| Figure 9.7: Test Case 2 - Distributed Configuration   | 189 |

| Figure 9.8: Test Case 3 - Publisher Component         | 190 |

| Figure 9.9: Test Case 3 - Subscriber Component        | 191 |

| Figure 9.10: Test Case 3 - Distributed Configuration  | 191 |

## **Acronyms**

API Application Programming Interface

CNC Computer Numerical Control

CPU Central Processing Unit

DCOS Distributed Controller Operating System

DCS Distributed Control System

ECC Execution Control Chart

FIFO/LIFO First In First Out/Last In First Out

I/O Input/Output

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

ISA/EISA Industry Standard Architecture/Extended Industry Standard Architecture

ISO International Standards Organization

LAN Local Area Network

MAP Manufacturing Automation Protocol

MB/GB Mega Byte/Giga Byte

MMS Manufacturing Message Specification

NC Numerical Control

OAC Open Architecture Control

OS Operating System

OSI Open Systems Interconnection

PC Personal Computer

PCI Peripheral Component Interconnect

PLC Programmable Logic Controller

TCP/UDP/IP Transmission Control Protocol/User Datagram Protocol/Internet Protocol

## Glossary

Agent An active control software component/module/object of a holon.

Autonomy The capability of an entity to create and control the execution of its

own plans and/or strategies.

Cooperation A Process whereby a set of entities develop mutually acceptable

plans and execute them.

Function Block A software functional unit comprising an individual, named copy of

a data structure and associated operations.

Holarchy A system of holons which can cooperate to achieve a goal or

objective. The holarchy defines the basic rules for cooperation of

the holons and thereby limits their autonomy.

Holon An autonomous and cooperative building block of a manufacturing

system for transforming, transporting. storing and/or validating

information and physical objects. The holon consists of an

information processing part and often a physical processing part. A

holon can form part of another holon.

Interoperability The ability of an entity to cooperate with other dissimilar entities.

Also the ability of heterogeneous hardware and software

subsystems to function together.

Loosely Coupled A distributed multi-processor system with no shared primary

memory.

Metamorphic A control system that undergoes constant transformation of form

and substance through out its life time.

Tightly Coupled A multi-processor system with shared primary memory.

## Chapter 1

#### Introduction

#### 1.1 Overview

Computer control of manufacturing systems has been the focus of extensive research over the last several decades. Advances in microprocessor, computing, networking and interfacing technologies have improved the capabilities of industrial automation and control systems substantially over this period. However, these control systems are proprietary and still have problems in areas such as interoperability, scalability, upgradability (without complete replacement), and lack of standard interfaces. The development of open architecture control systems addresses some of these problems, in varying degrees. Open architecture control systems shift the focus of automation from being hardware centric to software centric, providing further flexibility. The focus is now shifting to distributed control systems which is the central concern of this dissertation research work.

This dissertation addresses the engineering of software centric control systems for cooperating networks of distributed autonomous sub-systems to provide for enhanced interoperability, scalability, and upgradability. A comprehensive control architecture is presented for dynamically reconfigurable distributed multi-sensor based systems. A prototype control framework has been developed using a system level approach. The core distributed control mechanisms have been developed in the form of a distributed real time operating system. A state machine based sophisticated application specification model is used to develop reusable software modules. A system engineering interface has been developed to address the configuration and maintenance requirements of the distributed control system.

In this chapter, the concepts of holonic manufacturing paradigm and its Intelligent Control System are introduced. Subsequently, the motivation for developing a new control

architecture, and the objectives of this dissertation are presented. Finally, the organizational structure of the remaining chapters in this dissertation is outlined.

## 1.2 Holonic Systems

The change in market requirements towards a larger variety of products in smaller batch sizes, has lead to the concept of next generation intelligent manufacturing systems being an integrated network of distributed resources simultaneously capable of combined knowledge processing and material processing [Norrie94]. The control relationships among these distributed resources need to be reconfigured "on the fly" according to changing requirements [Norrie94]. Earlier research in the area of intelligent manufacturing systems has established that such resources can be realized through the concepts of holonic paradigm [Chris94a].

Arthur Koestler [Koes71] established the basic concepts of holonic systems by postulating a set of underlying principles to explain the self organising tendencies of social and biological systems. He proposed the term *holon* to describe the building blocks of these systems. This is a combination of the Greek word *holos*, meaning "whole", with the suffix -on meaning "part". This term reflects the ability of holons to act as autonomous entities, yet cooperating to form self-organizing hierarchies of subsystems. Koestler used the term *holarchy* to describe these holonic hierarchies. These concepts have been subsequently extended and applied in the context of manufacturing systems by an international consortium of industry and academia on Holonic Manufacturing Systems (HMS) [Chris94a].

In the context of manufacturing systems, a holon is defined as an autonomous and cooperative building block of a manufacturing system for transforming, transporting, storing and/or validating information and physical objects [Chris94b]. A holon has the autonomy to create and control the execution of its own plans, and can cooperate with other holons to develop mutually acceptable plans for achieving system goals. Cooperation among holons is accomplished through an evolutionary self-organizing holarchy. A holon consists of an information processing part and a physical processing

part, and can form a part of another holon.

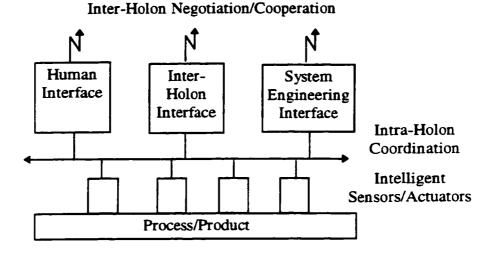

Fig. 1.1 illustrates the major functional elements and critical interfaces of a holon. As may be noted, the functional elements of holon are modular in nature and the architecture is highly distributed. Further, the constitution of holons change and the functional elements evolve over time according to system level requirements. For instance, a turning center holon may be augmented with certain milling operations or a holonic robot may be provided with additional vision system capabilities. Hence the ability to reconfigure on demand is an important requirement for holonic systems. This and other capabilities of holonic systems are largely dependent on their Intelligent Control Systems.

Figure 1.1: Holonic Elements and Interfaces

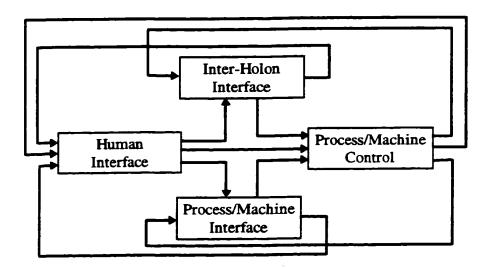

As shown in Fig. 1.2, the Intelligent Control System has been identified [Chris94b] to be comprised of four major components:

- The Process/Machine Control block, responsible for execution of the control plan for the process being controlled.

- The Process/Machine Interface block, representing the physical and logical interface (sensors and actuators) to the process being controlled.

- The Human Interface block, representing the interfaces to the human resources.

- The Inter-Holon Interface block, which provides for the exchange of information, negotiation and cooperation, with other holons in the system.

Figure 1.2: Intelligent Control System

In this dissertation, the architecture and functional elements of these four major components are developed. As mentioned earlier, the form and substance of holonic systems, and the control relationships among them, evolves continuously according to changing requirements. Due to this constant transformation of a holonic system within its lifetime, its control system undergoes metamorphosis. Hence we term this control system as "metamorphic". The issues associated with metamorphic control of holonic systems include predictable real time performance under distributed computation and control, dynamic reconfiguration and fault tolerance, distributed machine intelligence and cooperation, and distributed system engineering interface. The architectural requirements and development of such control systems have not been addressed before, in an integrated manner.

#### 1.3 Motivation

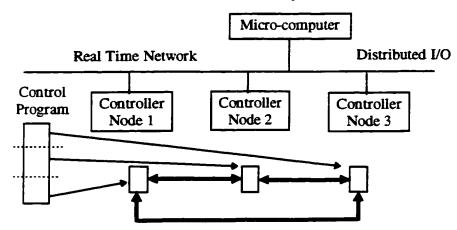

Real world autonomous and cooperative systems such as holonic machines operate under real-time constraints and are inherently distributed and dynamic. Traditional system structures based on static and hierarchical control do not suffice for such situations, and hence a new generation of control systems are needed. Modern and future machinery will therefore, include embedded modular distributed real-time computer control systems. The control system is distributed since computer nodes are spatially distributed in the machine

and control functions are distributed over the nodes. Nodes acquire sensor data, perform processing, exchange information over a real-time network, synchronize, and perform actuation, in order to achieve the system goals. Distributed control systems such as these can provide improved functionality, performance, flexibility, and reduced complexity and costs.

In order to function effectively, the distributed hardware and software systems which monitor and control real world processes must provide adequate means to cope with application requirements such as timeliness, concurrency, and decentralization. A predictable real time communication protocol is the backbone of a distributed control system. In addition, the control system also has to provide high degree of robustness and fault-tolerant behavior through the use of techniques such as component redundancies, dynamic reconfiguration mechanisms, and distributed intelligent sensors and actuators.

Real-time computer control systems arose and have evolved primarily in the context of small, simple, static, centralized, subsystems for unit-level, sampled data monitoring and regulatory control. Holonic systems move from centralized to distributed control, because the problem is distributed, and because of flexibility and cost-effectiveness. However there is a price to pay: system development becomes more complex than in the case of centralized control. There are no comprehensive methods or tools currently available to develop distributed control systems for holonic systems. Today, there are many commercial components that are available "off the shelf" for standalone control systems. Unfortunately, these systems do not scale up beyond the unit level and are unable to meet the needs of future applications in respect to performance, reliability, and extendibility.

For the new distributed control systems, a new design step is introduced in which the control tasks need to be structured and partitioned such that they lend themselves to distributed allocation. There are no tools to support this step and evaluate the effect on control system performance due to different allocations. In a real-time control system, several modes of operation usually need to be implemented as well as mode transitions among them. Data processing and communication in each case pose different requirements

with respect to delays, consistency, and error detection and handling. Existing systems do not provide any support to achieve these requirements nor for a host of others. In short, it becomes the responsibility of system designer/developer to meet any shortcoming at system level through a "piece meal" approach at the application level.

This lack of architecture and means for developing dynamically reconfigurable distributed control systems provides the prime motivation for the work presented in this dissertation. Having outlined the motivation, the following section describes the objectives of this dissertation.

## 1.4 Objectives

The goal of this dissertation is to provide a comprehensive framework for engineering dynamically reconfigurable distributed control of multi-sensor-based systems. It is targeted towards improving the capabilities, reliability and performance of distributed control systems, while at the same time significantly reducing the development time and costs. To achieve this goal, the research has focused on the following objectives:

- To identify the architectural components for generic metamorphic control of holonic systems.

- To develop the core distributed control mechanisms in the form of a distributed real time operating system.

- To develop a consistent programming model and the associated libraries for mapping application level requirements.

- To develop a graphical system engineering interface for configuration and maintenance of the distributed control system.

## 1.5 Organization of Dissertation

Having provided the motivation and objectives, this section outlines the contents of this dissertation. In Chapter 2, the state of the art in industrial automation and control is discussed. This is followed by an overview of emerging open architecture control technology. In Chapter 3, the requirements for metamorphic control of holonic systems

are identified and the need for a new and novel system-level approach is demonstrated. This is followed by a review of agent based intelligent control architectures. In Chapter 4, the relevant literature in the areas of distributed real time operating systems and formal specification methods of distributed real time systems, are reviewed.

In Chapter 5, a novel agent based metamorphic control architecture is presented and the critical components and issues of this architecture are identified. In Chapter 6, the concepts and architecture of a new distributed real time operating system is presented. In Chapter 7, the design and implementation of this distributed operating system are described. In Chapter 8, one feasible method for developing application software and a system engineering interface for developing application software, configuration and maintenance, are presented. In Chapter 9, the details of implementation infrastructure and evaluation of the implemented system are presented. Finally in Chapter 10, the conclusions are summarized, and the anticipated contributions and areas for future research are identified.

## **Chapter 2**

#### **Industrial Automation and Control**

#### 2.1 Introduction

In an automated manufacturing system, the objective is to achieve a complete spectrum of manufacturing control functions ranging from production planning and control at the highest level, to process/machine control at the lowest level. Intelligent manufacturing involves not only the achievement of these control functions, but seamless integration of these as well. Traditionally, these objectives have been achieved by horizontal integration across an hierarchy of control layers. However, for an autonomous holon the control objectives of traditional layers are partitioned vertically. Hence, a holon-based decentralized and distributed manufacturing system uses cooperation as the primary means to achieve system wide integration of control functions. In other words, the control objectives which need to be achieved at the individual holon level need also to be achieved at the system level. Obviously, the ability of a holon to achieve these control functions is directly dependent on its control system.

This chapter begins by presenting an overview of existing industrial control systems technology and is followed by a discussion on factory floor communications standards that are crucial for system integration. The drawbacks of extant control systems technology have led to a number of software centric open architecture control initiatives that are destined to impact the future of the control industry. Therefore, these efforts are reviewed in detail.

## 2.2 Industrial Control Systems

An industrial process/machine control system is the "sense and brain for the muscle" behind any automated manufacturing equipment. Its function is that of periodically comparing sensory process/discrete input variables with setpoints/logic states,

computing the outputs according to a predefined control algorithm/logic and communicating the output signals to the final control element for actuation. The industrial process/machine control systems used in a manufacturing scenario can be classified into following categories: Programmable Logic Control systems. Process/Loop Control systems. Distributed Control Systems, Computer Numerical Control systems and Robot Control systems. The following sub-sections discuss briefly the state of the art in these control systems.

#### 2.2.1 Programmable Logic Control Systems

The first Programmable Logic Control (PLC) [Bryan88] system was introduced in the late sixties as a replacement for massive hard-wired relay panels then used in manufacturing plants. In addition to the key feature of programmability, PLCs provided modularity, expandability, diagnosis indication and reliability under extreme factory floor operating conditions. Although originally designed for on/off applications, such as controlling the starting and stopping of transfer lines, PLCs rapidly spread to more sophisticated applications, such as those in the process industries. The evolution of the PLC over the years, due primarily to advancements in microprocessors, high-speed communication networks and software has gained it a central place in industrial automation.

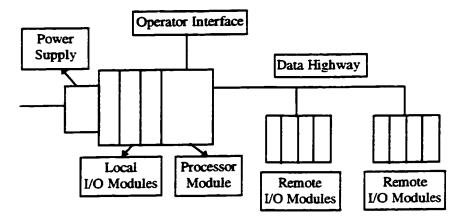

The architecture of a PLC resembles that of a general purpose microcomputer and can be considered representative of other controller systems as well. Basic PLC components are designed as self-contained modularized units that can be inserted and removed from industrial racks or panels. As shown in Fig. 2.1, the hardware platform of a PLC has three main sub-systems: a system power supply module, a processor module and Input/Output (I/O) interface modules. The PLC may also include a peripheral programming device and an interface to a data communications network. The system power supply module provides the necessary voltages for the correct operation of primary PLC components and also usually includes a battery backup to provide power to memory in case of a power failure.

Figure 2.1: Programmable Logic Control System

The processor module houses one or more microprocessors, their supporting circuitry and memory. The processor module also includes diagnostic indicators designed to detect communication failures as well as other failures during system operation. The memory is partitioned into two regions: a system memory region and an application memory region. The system memory includes an area called the executive or operating system, composed of a collection of permanently stored programs that direct all system activities, such as execution of user control programs, communication with peripheral devices etc. The system memory also contains the routines that implement the PLC instruction set, which is composed of specific control functions such as logic, sequencing, timing, counting and arithmetic.

The application memory is divided into the data table area and user program area. The data table stores any data associated with the user control program, such as system input/output status data, constants, variables, preset values etc. The data table is where data is monitored, manipulated and changed for control purposes. The user program area is where the programmed instructions entered by the user are stored as an application control program.

The I/O interface modules connects a PLC to external factory floor sensor/actuator field devices. The main purpose of the I/O interface is to condition the various signals received from or sent to the external input and output devices. Input and output modules are housed in the same master rack or panel that houses the other

components of PLC system. Additional I/O modules can be housed in a remote I/O racks that communicate with the master rack about I/O and diagnostic information. Every I/O module has its own address and these addresses are used in the control program to identify each input and output device.

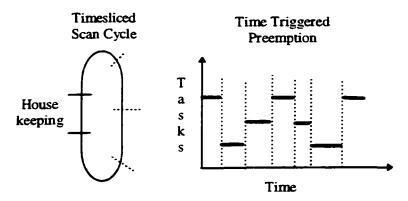

The operation of the PLC includes four phases which are repeated continuously for individual cycles of operation.

- Input Status Scan: During this period the sensor readings are mapped onto a data table

called the input image table. This phase is carried out as a single step uninterrupted by

other operations to provide a clear snap shot of the state of the process at a given

instant.

- Program Execution: In this phase, the user control program is executed. The values in

the input image table are examined, the required calculations and logic are performed

and the results are stored in a data table called output image table.

- Output Status Scan: In this step the stored output values are sent to actuators and other field output devices.

- Housekeeping: In this step, several overhead functions such as diagnostic checks, service of peripheral devices, communications etc. are performed.

The time that a PLC takes to complete these four phases is called the scan time. The program scan time depends on the amount of memory needed by the control program and type of instructions used within it. The scan time can be usually calculated based on the instructions used in the control program. However, other factors such as use of remote I/O, execution monitoring of control program etc., can add additional scan time. PLCs are predominantly programmed using relay ladder logic. However, a variety of other languages such as instruction list, structured text, function blocks, sequential function charts etc. are now also used.

## 2.2.2 Process/Loop Control Systems

The heart of many process control operations is the loop controller [Earl92]. This is the device that does the actual control, keeping the process variable at the setpoint and

maintaining stability. Loop controllers are available as single loop and multi-function loop controllers. The loop controller may be broken down into three major functional areas: operator interface, control data processor and I/O interface. The operator interface typically includes visual display facilities for process variables and a keypad to enter setpoints and other control parameters. The control data processor is microprocessor based and includes system memory. The I/O interface consists of signal conditioning circuitry to convert the input and output to compatible signals for the control data processor and actuator control device, respectively. All loop controllers provide the capabilities for simple proportional-integral-derivative (PID) control without any requirement for programming. Other loop controller features that may be present include but are not limited to, auto-tuning capability, multiple PID algorithms, cascade control, dead time compensation, batch control recipes, diagnostics, internal clock, logic functions, math functions, adaptive control, feed forward control, fuzzy logic, etc.

#### 2.2.3 Distributed Control Systems

The distributed Control System (DCS) [Wayn91] in its infancy, simply provided remote control of valves and other final control elements, based on setpoints from the operator and feedback from the process. Today, various control, interface, and communication functions are distributed among widely separated devices and a data highway carries information between them. Typically, several sophisticated multi-function process controllers form the network of distributed control operations with a centralized operations control room. This modular distributed architecture provides geographical and functional distribution. With geographical distribution, it is no longer necessary to run hundreds or thousands of separate wire pairs to link each point in a system with a central computer or control station. Instead, the system components can be located throughout a plant, all linked for plant wide communications via a data highway. To expand the system, the user simply connects new field devices to the data highway. Functional distribution means that control system tasks are assigned to individual devices. Thus, controllers in remote locations perform control functions independent of other devices in the system.

Similarly, both the centralized and remote operations consoles provide a real-time operator interface to observe process conditions and controller actions and to interact as necessary. DCS process controllers need not be programmed in the same sense as a PLC, since their 'programming' is more like choosing the right control function and configuring it. Their suppliers also provide a proprietary high level control language for programming if needed. Much DCS technology is proprietary in nature and used only in high end continuous process control applications due to the high cost of its implementation.

#### 2.2.4 Computer Numerical Control Systems

Numerical Control technology has evolved from the "brittle" hard-wired analog control systems to flexible, reliable and performance intensive microcomputer based digital Computer Numerical Control (CNC) systems [Sten97]. The microcomputer acts both as a intelligent human interface and as a supervisory coordinating controller for spatially distributed, embedded microprocessor controlled drives. The distributed servomechanism drive controllers have the capability to communicate among themselves as well as with the supervisory microcomputer. CNC systems are programmed using standard part programming languages such as RS-274D. CNC systems provide a set of parameters that can be software configured to dictate the behavior of the system. They also offer a rich set of diagnostic messages and services. Distributed numerical control is a logical extension to CNC systems in that it replaces the earlier unreliable tape reader for part programs, with high speed storage and retrieval of programs through a factory control network. It provides facilities for control of program execution from remote computers. communication with other control systems for task coordination, collection of production statistics, etc.

## 2.2.5 Robot Control Systems

Most industrial robots use some form of PLC equipped with special motion control modules in their control systems [MC95]. The PLCs are augmented with coprocessors and software that lets them execute complex procedures according to simple

instructions in user programs. Such robots typically provide simple point to point or contouring motion. Complex and high performance robots use proprietary control systems technology to provide sophisticated features such as velocity control, force control, fuzzy logic control, vision system and mobility. Robot controllers are predominantly programmed using teach pendant and high level proprietary languages such as VAL and V+, but some provide facilities for using a systems language such as C. Robot controllers also provide capabilities for remote program storage and retrieval, remote program execution, communication and coordination with other controllers, and on-line status information from remote locations.

# 2.3 Factory Floor Communications

Many of the communication schemes for passing data among nodes (devices connected to network) on a factory automation network have been proprietary, and closely held by the companies that developed them. Interoperability between devices from different suppliers often requires gateways and special interfaces that can be inefficient. functionally limited and slow to be developed. Faced by demand for greater interoperability among equipment from various vendors, both at the control and plant information level, the industry focus has shifted to the development and adoption of standard protocols (sets of rules for formatting, encoding and transmitting data). In addition, the proliferation of increasingly smart devices at the field level and the growing functionality of these devices in control schemes have resulted in intense interest in the development of field level communication standard protocols.

All of these standards are based on the Open Systems Interconnection (OSI) reference model [ISO84] defined by the International Standards Organization (ISO). The OSI model defines seven hierarchical layers: physical, data-link, network, transport, session, presentation and application. At the bottom is the physical layer, which defines parameters such as bit rate, the method of encoding bits, electrical or optical characteristics of the communication channel and the manner in which stations are connected to the channel. The data-link layer organizes data into a sequence of bytes

known as a frame and passes it to the physical layer for transmission. The data-link layer also determines which station has a right to transmit on the network, a function called Media Access Control (MAC) that is critical to the performance of the network.

The network layer provides an end-to-end channel which could be made up of many point-to-point connections, or data links. The network layer also reroutes traffic to avoid congestion. The transport layer provides a reliable end-to-end transmission channel, regardless of how many links and subnetworks the data passes through. The session layer provides mechanisms for controlling dialogs between applications. In other words, it ensures that all participants in a dialogue encode their data in a common language. The presentation layer negotiates what is known as abstract syntax (the elements that make up a language vocabulary, such as integers, characters and records) and transfer syntax (the rules for representing these elements in 1s and 0s). At the very top is the application layer. This layer provides high-level services for data access.

A number of communication protocols oriented toward the control or field network level for industrial automation have been based on the OSI model. Notable among these are the Manufacturing Automation Protocol (MAP) and field level communication standards. The following sub-sections discuss these in detail.

## 2.3.1 Manufacturing Automation Protocol

MAP [Val92] was introduced as a means of interconnecting control devices such as process controllers, CNCs, PLCs and robots, and of providing a connection to higher-level plant systems. The MAP standard has been developed and is maintained by the Technical Committee for Industrial Automation, of the ISO. MAP is built upon the Institute of Electrical and Electronic Engineers (IEEE) 802.4 standard for physical and data link layers. This standard specifies coaxial or fiber connection in a bus or tree topology running at 5 or 10 Mbits/s at the physical layer. The data link layer MAP uses an approach called token passing to share access to the bus by multiple devices in a controlled manner. In a token passing architecture, the right to 'speak' on the network (the token) is circulated from device to device in a predetermined manner. As each device

receives the token, it can put traffic on the network for a predetermined maximum length of time before passing the token to the next device in the sequence. This gives every device on the network the chance to transmit with the maximum waiting time between transmissions for a given node being dependent on the number of nodes and amount of traffic on the network layers. Layers 3-6 of MAP make it possible for MAP networks to be interconnected with other networks and different data formats.

The Manufacturing Message Specification (MMS) [ISO90] is an internationally standardized messaging system for exchanging real-time data and supervisory control information between networked devices and/or computer applications. It defines the application layer (layer 7) protocol of MAP. The messaging services provided by MMS are generic enough to be appropriate for a wide variety of devices, applications, and industries. Whether the device is a PLC or a CNC or a robot, the MMS services and messages are identical. The MMS standard consists of six parts. Part 1 is the service specification and contains a definition of

- The Virtual Manufacturing Device.

- The services (or messages) exchanged between nodes on a network, and the attributes.

- Parameters associated with the Virtual Manufacturing Device and services.

Part 2 is the protocol specification and defines the rules of communication which includes

- The sequencing of messages across the network.

- The format (or encoding) of the messages.

- The interaction of the MMS layer with the other layers of the communications network.

The remaining parts explain how MMS can be used for a class of applications such as CNCs, Robot controllers, PLCs or Process Controllers. These companion standards model an application area in terms of objects which are then mapped onto MMS objects. To manipulate the application objects, one has to actually manipulate the corresponding MMS objects with the appropriate services. The key feature of MMS is the Virtual

Manufacturing Device (VMD) model. The VMD model specifies how MMS devices, also called servers, behave as viewed from an external MMS client application point of view. MMS allows any application or device to provide both client and server functions simultaneously.

MAP provides partial integration of plant devices, at the non-time critical layer of plant information gathering through a restrictive client-server model of communications. This and a host of other factors such as cost and complexity of implementation have led to the failure of MAP. However several smaller versions of MAP such as Mini-MAP, MAP/Enhanced Performance Architecture (MAP/EPA) and Factory Automation Instrumentation System (FAIS), have been developed and have received limited acceptance.

#### 2.3.2 Field Level Networks

In the last two decades, much of the network integration work was focused at the plant information level, such as MAP. Recently, much of the network integration effort has shifted to the field level. This is due primarily to advances and cost reductions in microprocessor technology that have made possible smart field devices with digital communication capability. A field level network is a digital communications standard for measurement and control field devices. Field level networks are emerging at two functional levels: sensor bus networks used primarily as high speed communication networks for simple field devices, and low/high speed fieldbuses aimed at both the process control and/or discrete manufacturing industries [John95].

All of these networks have multidrop capability, allowing for the connection of numerous field devices to a single bus, rather than having each device wired directly to the control system. Consequently, the most obvious benefit of field networks is a reduction in the cost of field wiring and wiring maintenance. Additionally, digital communications makes it possible for devices to provide increased diagnostic information remotely and continuously. This in turn, reduces the amount of time and effort expended on field device maintenance. Further, since the smart field devices have some onboard intelligence, some

control functions can be further distributed downward to reside in the field devices themselves.

Sensor bus networks [McMa95] are aimed at replacing the point-to-point individual wiring currently used for photoelectric, proximity, pressure and other low cost sensors and switches commonly used in discrete manufacturing or packaging industry. Sensor bus networks require a four wire connection and are not capable of the same distances as fieldbuses. Two wires are used for communication and two wires provide power to the field device. Sensor bus networks are generally high speed with extremely simple message structures to enable millisecond response. Several sensor bus networks such as the Devicenet network, Smart Distributed Systems network (both based on Controller Area Network), Bitbus network, Highway Addressable Remote Transducer network. Actuator Sensor Interface network and LonWorks network, have been developed and have found varying degrees of acceptance.

There are three major low/high speed fieldbus protocols vying for international recognition [Chat92]. The first is IEC/SP50, which represents the joint efforts of International Electrotechnical Commission (IEC) and Instrument Society of America (ISA). It uses only three layers of OSI model, namely physical, data link and application layer. It provides peer-to-peer communications using twisted pair wire at several transmission speeds. The second is the Factory Instrumentation Protocol (FIP), a French national standard. It also uses only three layers, with the application layer services being a subset of MMS. It provides Master/Slave communications using twisted pair wire at several transmission speeds. The third is the Profibus or process fieldbus, a German national standard. It again uses only three layers with the application layer services being a subset of MMS. It provides master/slave or token passing communications using twisted pair wire at several transmission speeds. In addition, other fieldbus networks such as Controlnet network and Interoperable Systems Project fieldbus network have been developed and have found varying degrees of acceptance.

# 2.4 Open Architecture Control

Currently, most industrial control systems incorporate proprietary control technologies. Even though these proprietary technologies have been proven to be reliable and capable of meeting application needs, there are difficulties associated with using them. Examples of these difficulties include non-common interfaces, inability of equipment from different vendors to interoperate, and inability to extend and enhance the control system without replacing them. Hence, in recent years, industry and academia have shifted their focus towards the development of Open Architecture Control (OAC) systems. IEEE defines openness as [IEEE83]: "An open system provides capabilities that enable properly implemented applications to run on a variety of platforms from multiple vendors, interoperate with other systems, applications, and present a consistent style of interaction with the user".

The concept of OAC provides flexibility in terms of both hardware and software, and shifts the focus from hardware to software. By moving away from a hardware centric control to a software centric one, the OAC concept makes it possible to change the basic configuration of hardware at any time during the controller life cycle. This allows for incorporating advances in hardware without having to change the software interfaces. Further, the limitation of a restricted instruction set from a control equipment vendor, without the possibility for enhancement, is done away with in an OAC. Since the system is software based, the programming capabilities of a OAC is limited only by the Application Programming Interfaces (API) and the software libraries used. With the advent of mature OAC systems, the programming capabilities should approach that of general purpose computing systems.

An open architecture control system provides benefits such as reduced system costs, simplified integration of tasks, easier incorporation of diagnostic functions, better integration of user knowledge, and quick and easier reconfiguration of control systems with changing requirements. With the availability of open, modular control systems, the distinction between the various types of process/machine control systems and their

applications become blurred. The modularity and scalability of the OAC enables easy integration of particular functions for specific applications and hence reduces the need to have dedicated control systems.

As mentioned earlier, several initiatives are underway to develop an OAC. Notable among these are: the Open Modular Architecture Controller (OMAC), the Open Systems Architecture for Controls within Automation systems (OSACA), the Open System Environment for Controller (OSEC), the Enhanced Machine Controller (EMC), the University of Michigan Open Architecture Controller (UMOAC) and the Machine tool Open System Advanced Intelligent Controller (MOSAIC). The following sub-sections discuss these efforts in detail.

## 2.4.1 Open Modular Architecture Controller

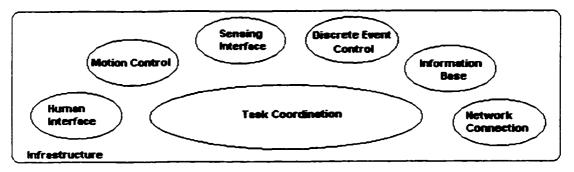

The OMAC [OMAC94] initiative is a joint effort by the 'Big Three' automobile manufacturers in North America: Chrysler, Ford and General Motors, with a pilot project at the GM power train division. OMAC has the distinction of being the largest effort to develop an OAC to date. As an OAC, the openness and modularity of an OMAC are achieved mostly through software modules rather than hardware components. Fig. 2.2 illustrates the concept of modularity in OMAC using cooperating entities to perform the different controller functions. The scalability of the controller is achieved by adding, removing, or replacing control modules to the controller architecture. For example, modules for motion, sensing, and the network interface can be removed from the controller architecture to meet the requirements of a low cost control application. On the other hand, all these modules may be integrated to control a complicated, sensor adaptive controlled machining operation.

The modularity concept allows for interchangeability of controller modules i.e. replacement of a module with another that meets the same interface requirements even if the replacement module may not have identical, detailed internal functions. Instead of requiring replacement of an existing module, the model also allows for incremental functional improvements to each control module with technological advances and

changing requirements. The OMAC groups these modules into two sets: core modules and API modules.

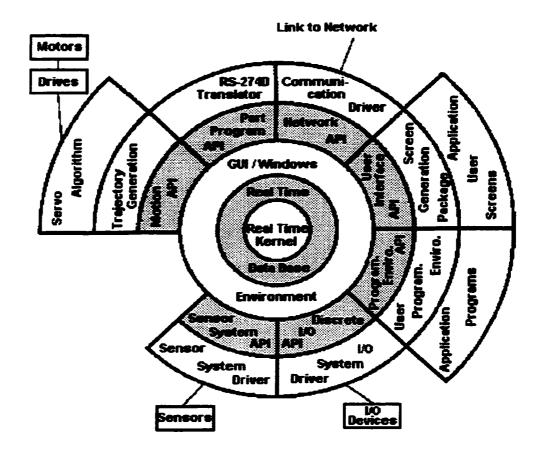

Figure 2.2: Open Modular Architecture Controller

OMAC identifies the real-time kernel, database, and the graphical user interface environment as being the core modules, and the successful resolution of issues in these areas as a prerequisite for its success. OMAC requires flexibility in terms of selecting the most appropriate operating system kernel for a particular application. In other words, a controller designed to satisfy applications with real-time requirements in the range of seconds may require an operating system kernel that is different from the one implemented in a controller that is used primarily in applications with millisecond real-time requirements. However, both controllers will have identical graphical interface environments to the users and this feature is considered critical to achieve scalability.

The API modules layer is considered to be the critical layer to achieve 'plug-and play' functionality and much work needs to be done in standardizing the interfaces. Through well defined and commonly accepted APIs, OMAC aims to integrate modules from various vendors into the controller infrastructure without extensive reprogramming, even though special efforts will still be required to integrate device specific software (e.g. device drivers).

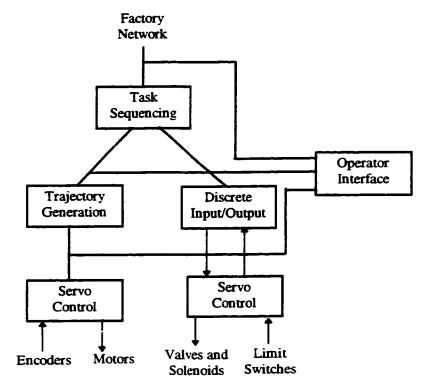

As shown in Fig. 2.3. OMAC groups the functionality of control into eight controller elements. The infrastructure element consists of the hardware platform, real time operating systems, graphical user interface, and the underlying system level software that interacts with all other elements by sending and receiving information such as commands, status, and data. The information base element consists of a real time data base module and is responsible for storing, updating, and sharing system information and data that are needed for the machine or process to operate properly. The task coordination element functions as a coordinator of application tasks being executed by the controller. It ensures proper sequences of machine or process operations are scheduled and executed at the application level, by using the scheduling and coordination services of controller operating system.

Figure 2.3: Elements of OMAC

The human interface element is used to input system parameters, program machine and process operations, operate the machine or process being controlled, monitor machine and process performance, display controller and process status, receive and display diagnostic information, etc. The motion control element provides the key functions for

path planning, trajectory generation, and servo loop trajectory tracking. The motion control functions may be executed by a dedicated motion control board in the controller or can be executed by the main CPU of the controller. However, the API between the infrastructure system software and the motion control element is identical regardless of the motion control hardware configuration.

The discrete event control element interacts with the external environment and implements an all software based PLC. It collects input information, executes the discrete logic, enables output devices, and also supplies I/O information to the real-time database for other controller elements to make proper decisions and take appropriate actions. The sensing interface element provides a means to gather information from complex sensing devices and systems, such as vision systems and force monitoring systems, that generally acquire and process a large amount of data. The network connection element provides facilities to upload and download programs and to transfer information about production statistics to the plant manufacturing information system when they are requested.

# 2.4.2 Open Systems Architecture for Controls within Automation Systems

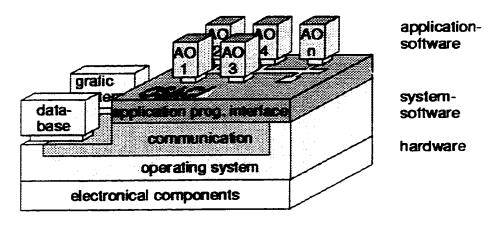

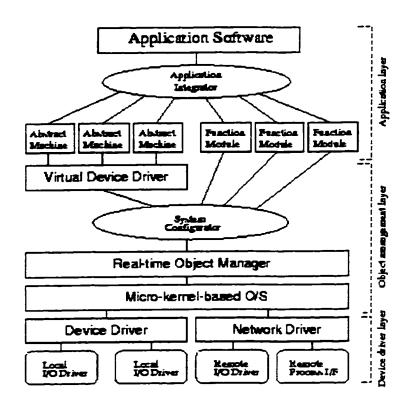

OSACA [OSACA96] is a joint project by a consortium of European control systems and machine tool manufacturers and universities. The main goal of OSACA is to define a hardware independent reference architecture for controller equipment such as robot controllers, numerical controllers, logic controllers and cell controllers. OSACA has elaborated specifications primarily by defining a software reference architecture. This reference architecture enables the interchangeability and extendibility of comparable control specific application Architecture Objects (AO). It defines which AOs can be found in a control system, what tasks they perform and how they interact with each other.

As shown in Fig. 2.4, the architecture consists of two main sub divisions: the System Platform and Architecture Objects. The system platform consists of system hardware and system software. The system software contains core parts such as operating system, communication system, database and graphical user interface. It offers its services through a standardized API and is the only means of access from AO. This hides the

actual implementation of services, thus achieving hardware independence. Interoperability of AOs is achieved through a standardized communication system which not only allows interchange of data but also defines the protocols for interchange. Portability of AOs is guaranteed since the API is standard across various platforms. Scalability is achieved by adding, removing or modifying system hardware, software and/or AOs.

AO: Architecture Object

Figure 2.4: Open System Architecture for Controls within Automation Systems

The AOs are grouped into 5 areas also called subjects, according to their functions in control: Man Machine Control, Motion Control, Axis Control, Process Controls and Logic Controls. The man machine control represents the machine or part of it, to external entities, such as the operator and supervisory control system, and allows these entities to control the operation of the machine. Motion control enables the machine to produce relative motion of a given degree of freedom, by commanding axis controls. Axis control includes all the means necessary for activating the axis to execute movement commands within defined constraints. Process controls represent the auxiliary systems of the machine. Logic controls are responsible for discrete sensors and actuators of the machine.

OSACA has specified a vendor neutral communication system based on the ISO/OSI reference model. In this model, the internal control communication is via a uniform, message oriented communication interface. In order to fulfill the high real time demands on the controller, layers 1 to 4 were combined into the OSACA Message

Transport System and layers 5 to 7 to the OSACA Application Services System. The message transport system provides a hardware independent interface for transport of arbitrary messages between arbitrary objects both for local and distributed control. The application services system is responsible for connection management, encoding and decoding of messages, data format conversions and error correction within the communication system. To simplify the implementation and management of communication objects with the AOs, a Communication Object Manager is used. It provides an optional layer with standard routines and call back functions for creation and deletion of communication objects.

OSACA specifies that the real time controller operating system should be compliant with IEEE POSIX portable operating system standard and its real time extensions. It also specifies the requirements for process scheduling, real time aspects. parallel tasks and task distribution, within the operating system. OSACA specifies the architecture of a Configuration Manager that can be used for both static configuration during boot up and dynamic configuration during run time. Means are also specified for integrating databases.

## 2.4.3 Open System Environment for Controller

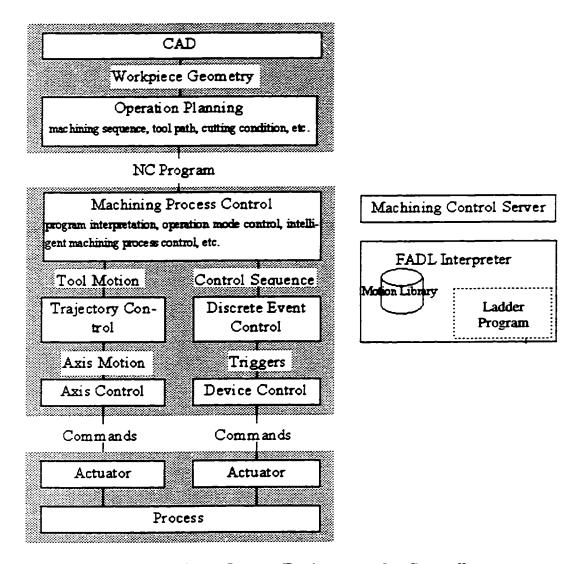

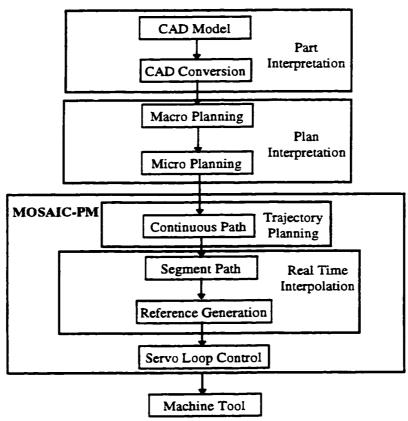

OSEC [OSEC95] is a joint effort by a consortium of Japanese machine tool and control equipment manufacturers to develop an open architecture controller for CNCs. OSEC has a restricted focus compared to OMAC or OSACA in the sense that it is only meant for CNCs. Further, OSEC architecture specifies a personal computer based open architecture Numerical Controller (NC). As shown in Fig. 2.5, the OSEC reference architectural model for CNC systems consists of the following parts: an operation planning part, a machining process control part, trajectory control part, an axis control part, a device control part and actual devices.

Figure 2.5: Open System Environment for Controller

The operation planning part includes a CAD/CAM system to generate geometric design, machining sequence and part program codes. The machining process control part includes program interpretation, supervisory operation control, intelligent machining process control, etc. The trajectory control is responsible for generating coordinated commands to axis control. The axis control is responsible for achieving desired axis motion. The discrete event control part executes logic control functions of the controller. The device control includes control of auxiliary devices that may be present in the machine tool. The actual devices include all forms of sensors and actuators.

The service and the protocol for connecting modules are designed to form autonomous agent systems that exchange messages in distributed network environments. To achieve a high degree of autonomy, OSEC defines a new data communication language called the Factory Automation equipment Description Language (FADL). FADL provides a rich set of services to interact with the real time controller and to command control sequence in a hardware independent manner.

OSEC also provides NC machining libraries to dynamically alter the control system performance. NC machining libraries are classified into 3 levels: machining description level, machining level and servo drive control level. These library functions are defined externally and linked dynamically during run time to command different types of system behavior and servo drives. The OSEC also specifies a service and message protocol for remote control of NC nodes based on the MMS standard. Service functions include management of the communication environment, uploading/downloading of program/data. reading and writing of control parameters, monitoring and signaling of alarms etc.

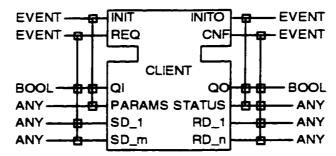

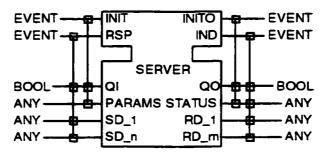

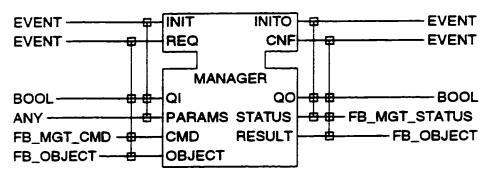

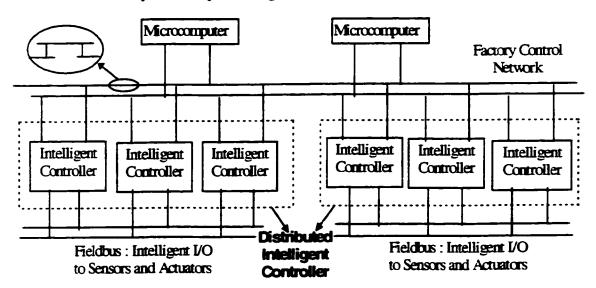

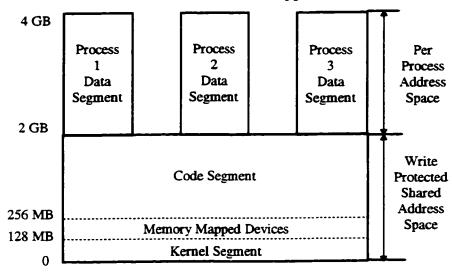

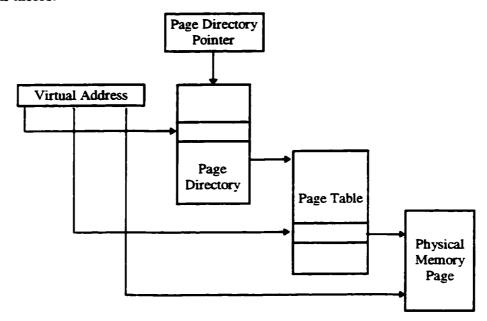

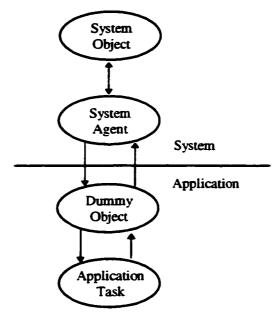

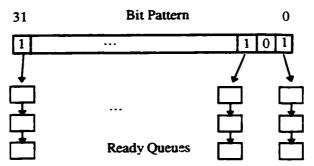

#### 2.4.4 Enhanced Machine Controller