The Vault

Open Theses and Dissertations

2014-12-03

# A Broadband Variable-Gain Amplifier and a Broadband Self-Calibrated High-Sensitivity Power Detector for the Square Kilometre Array

Wu, Ge

Wu, G. (2014). A Broadband Variable-Gain Amplifier and a Broadband Self-Calibrated High-Sensitivity Power Detector for the Square Kilometre Array (Doctoral thesis, University of Calgary, Canada). Retrieved from https://prism.ucalgary.ca. doi:10.11575/PRISM/24637 http://hdl.handle.net/11023/1948

Downloaded from PRISM Repository, University of Calgary

### UNIVERSITY OF CALGARY

A Broadband Variable-Gain Amplifier and a Broadband Self-Calibrated High-Sensitivity

Power Detector for the Square Kilometre Array

by

Ge Wu

### A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

GRADUATE PROGRAM IN ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

NOVEMBER, 2014

© Ge Wu 2014

### **Abstract**

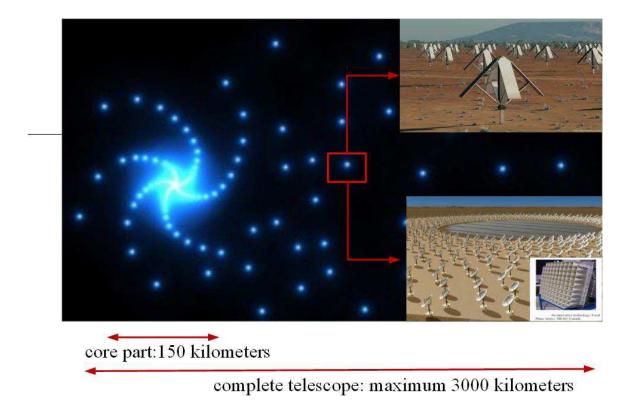

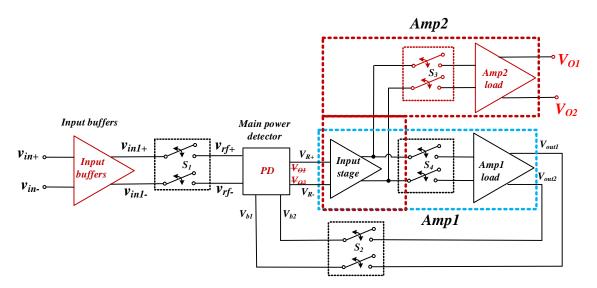

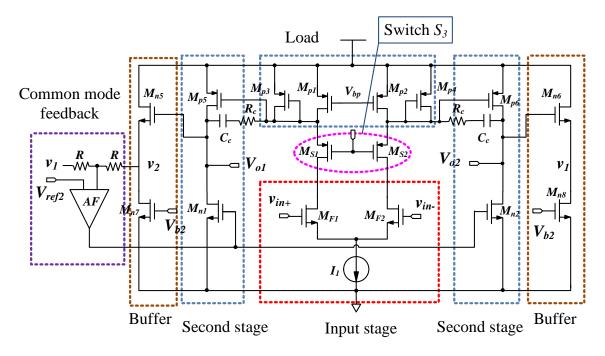

The Square Kilometre Array (SKA) is an international project to design and construct the next generation ultra-sensitive radio telescope. Depending on the final configuration, the SKA will require millions of receivers ideally fabricated in a low cost semiconductor process. This thesis presents a study of using CMOS technologies, which are the most common and less expensive semiconductor option, to implement a variable gain amplifier (VGA) with a linear-in-dB performance and an RMS power detector (PD) for a mid-frequency SKA receiver.

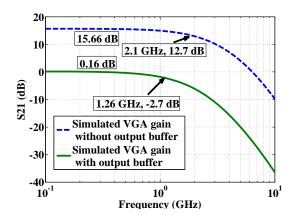

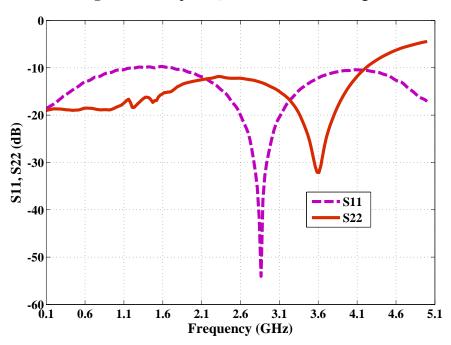

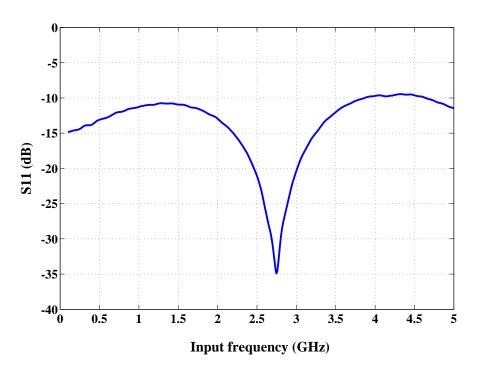

Two linear-in-dB VGAs were designed and experimentally verified in this work. The first VGA meets most of the SKA specifications except bandwidth and linear-in-dB range. The second VGA uses a bandwidth extension technique and a low threshold voltage transistor to achieve a maximum tunable gain range of 34 dB and the linear-in-dB range of 28.5 dB within  $\pm 1$  dB error, an upper 3 dB cutoff frequency of 2.1 GHz and a power consumption of 1.1mW. Both S11 and S22 are less than -10 dB from 100 MHz up to 4.2 GHz. This VGA achieved the lowest power consumption among comparable VGAs published to date.

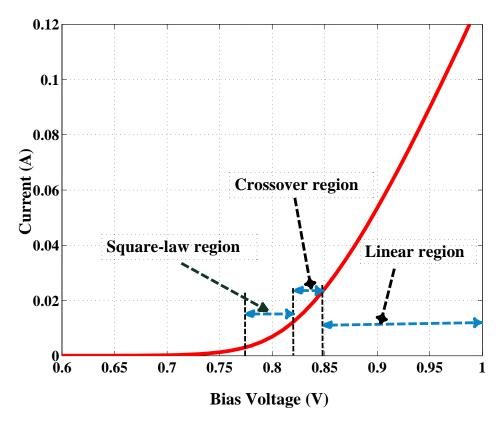

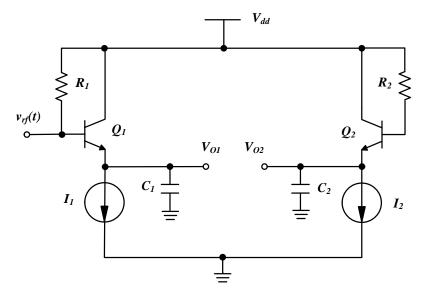

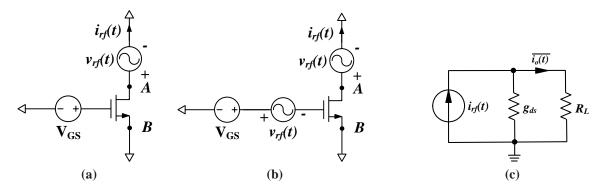

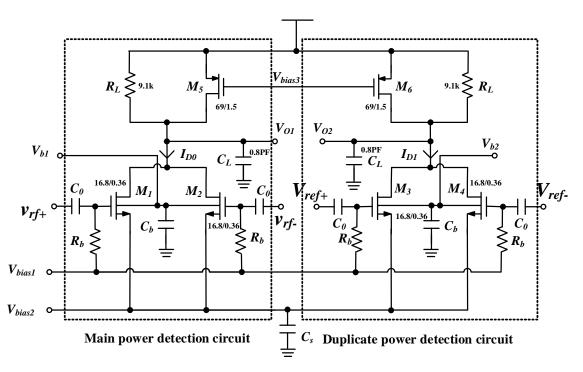

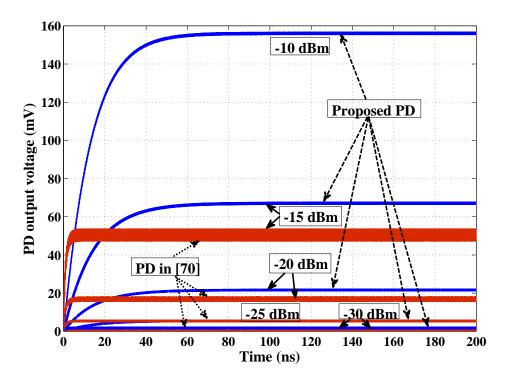

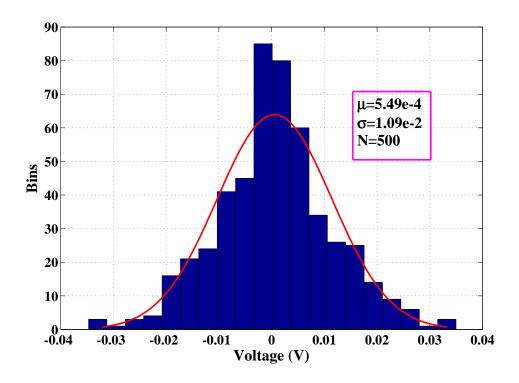

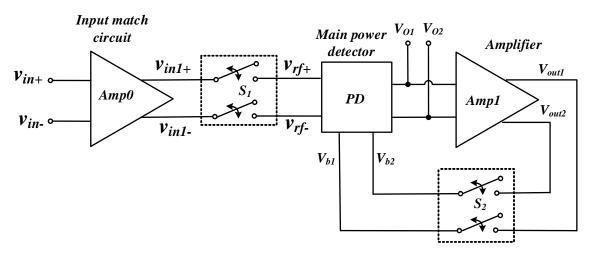

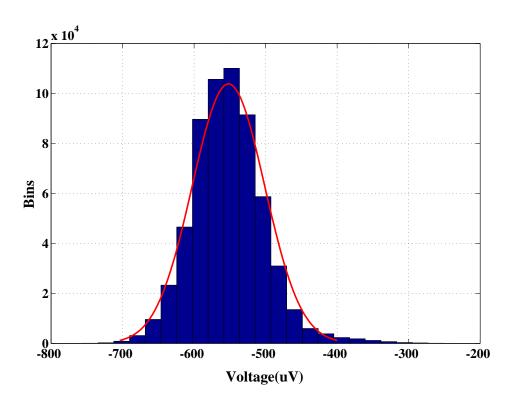

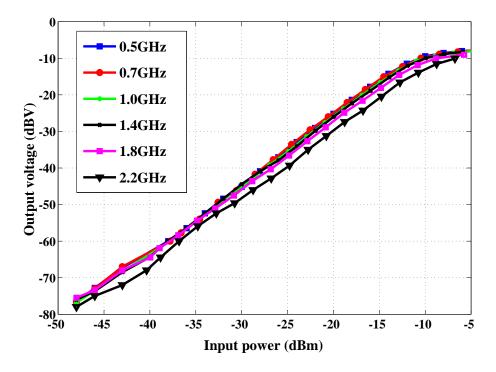

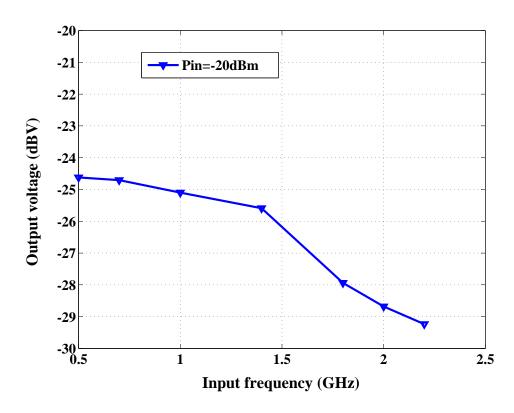

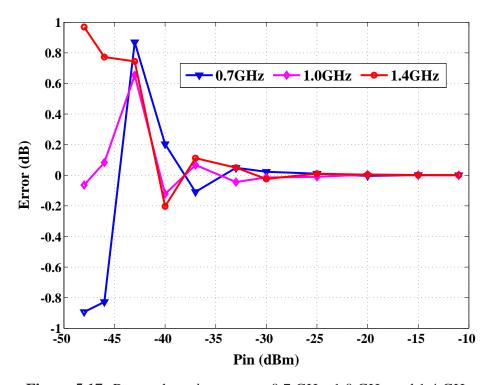

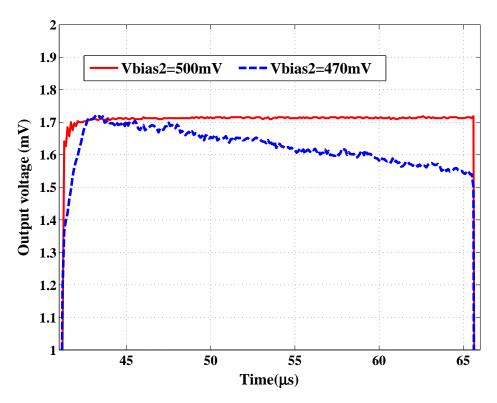

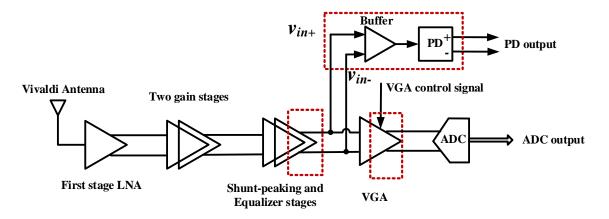

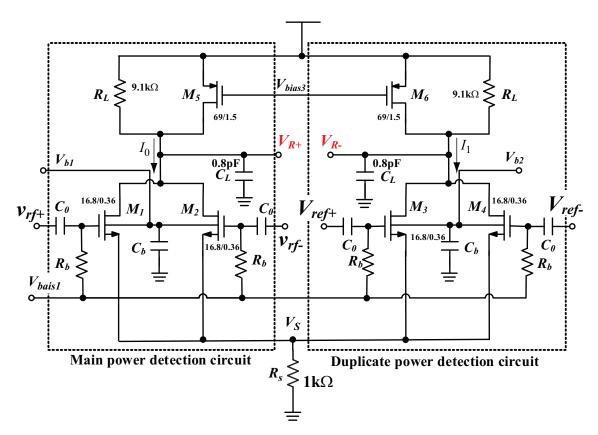

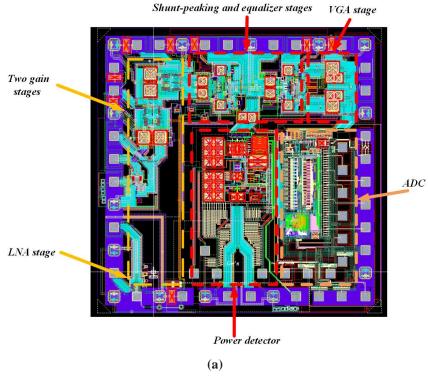

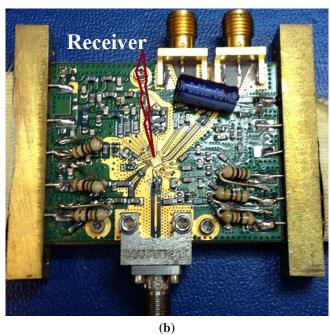

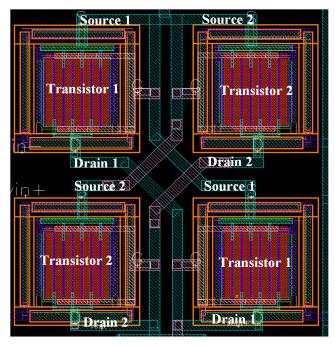

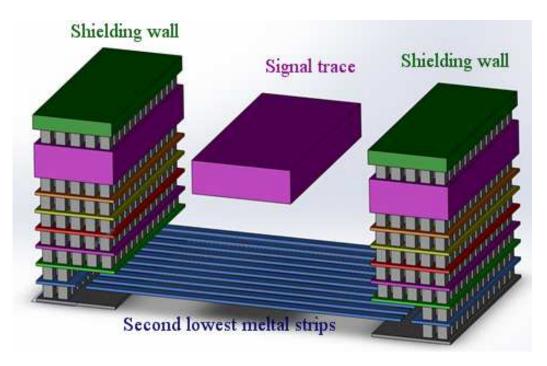

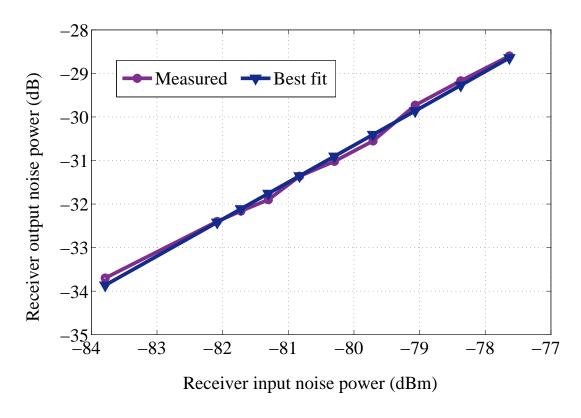

A differential broadband self-calibrated RMS PD using the MOSFET square-law characteristics was proposed and experimentally verified in this work. After automatically compensating mismatches between all circuit components by adjusting input transistor bulk voltage, the proposed PD circuit showed the highest sensitivity and lowest power consumption of all PDs published prior to this work. The PD operates over an input power range from -48 dBm to -11 dBm with output voltage offset less than 0.95 dB for the SKA midfrequency range with an input-referred  $P_{1dB}$  of -11 dBm, 3 dB bandwidth of 1.8 GHz and power consumption of only 1.2 mW. This PD meets all requirements of the mid-frequency SKA receiver. This power detector was embedded within the receiver and fabricated in a TSMC 65nm CMOS process. Measurement results showed an input power range from -40 dBm to -20 dBm with power consumption of 1.5 mW.

### Acknowledgements

I would really like to thank my supervisor Dr. Leonid Belostotski for his guidance, patience, and interest throughout my Ph.D research work. I appreciate his broad knowledge and experience in the RFIC design. He is always helpful and spent as much time as I needed to discuss the problems of my Ph.D research work. I would also like to thank him for his patience and spending days and days helping me write and edit my papers for conferences and journals. This provided me with many opportunities to attend very good conferences.

Second, I would really like to thank my co-supervisor Dr. J.W. Haslett for his guidance, enthusiasm and support in the Ph.D research work. I admire his talent and dedication in the RFIC design and am deeply moved by his preciseness in doing research work. I really appreciate him spending hours and hours discussing my research work and using days and days correcting and editing my papers and supporting me to go to many good conferences. I also want to thank him for his very kind understanding whenever I need some personal time for family.

Third, I would like to thank CMC Microsystems for subsidizing the cost of fabricating all ICs used in this thesis.

Fourth, I would like to thank Zhixing Zhao, Yongsheng Xu and Aaron Beaulieu for teaching me to use the wirebond machine and measurement instruments.

Fifth, I would like to thank all the people in the RFIC lab for their help.

Last, I would like to thank my parents, without their support I could not finish this work.

For Jie, my lovely boys Yibo and Kinsey, and my parents

### **Table of Contents**

| Al | bstrac  | et      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ii   |

|----|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A  | cknov   | vledgmo | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iii  |

| De | edicat  | tion    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iv   |

| Ta | ble of  | f Conte | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vii  |

| Li | st of ' | Tables  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | viii |

| Li | st of l | Figures |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xiii |

| Gl | lossar  | ·y      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xiv  |

| 1  | Intr    | oductio | on and the same of | 1    |

|    | 1.1     | Square  | e Kilometre Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2    |

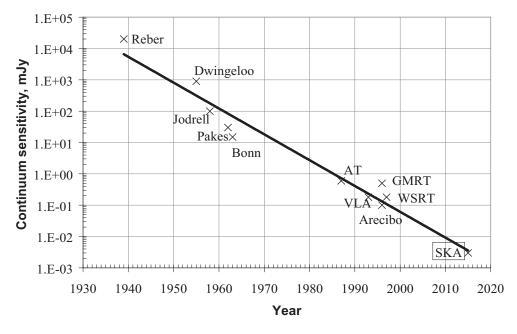

|    |         | 1.1.1   | Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3    |

|    |         | 1.1.2   | Survey speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4    |

|    |         | 1.1.3   | System noise temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5    |

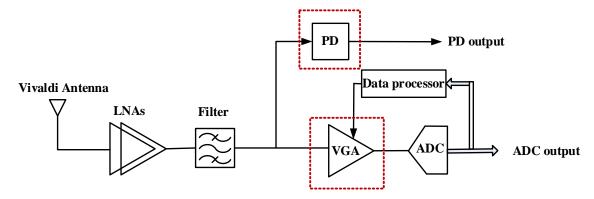

|    | 1.2     | SKA 1   | receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5    |

|    |         | 1.2.1   | LNA and gain stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7    |

|    |         | 1.2.2   | Variable-gain amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8    |

|    |         | 1.2.3   | Power detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8    |

|    |         | 1.2.4   | Analog-to-digital converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9    |

|    | 1.3     | Thesis  | s layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9    |

|    | 1.4     | Contri  | ibutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10   |

| 2  | Bros    | adband  | Linear-in-dB VGA techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12   |

|    | 2.1     | Variab  | ble gain amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12   |

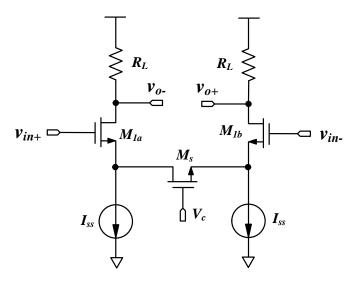

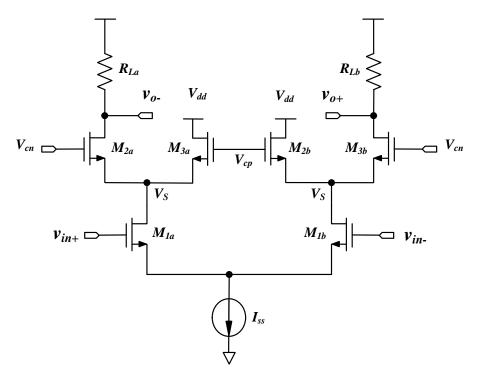

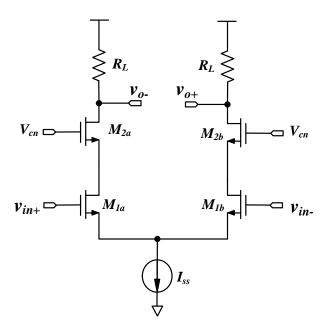

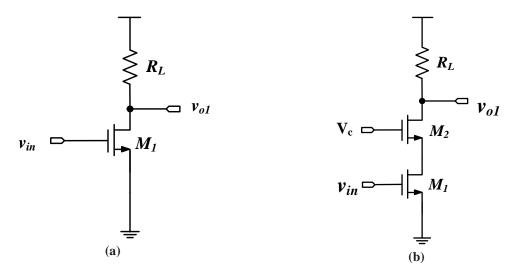

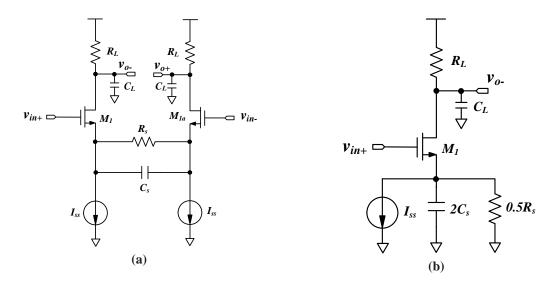

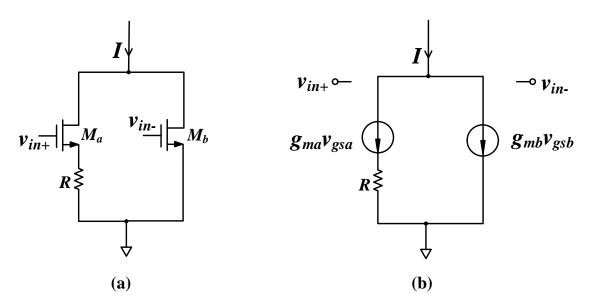

|    |         | 2.1.1   | Tranconductance-tunable VGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13   |

|    |         | 2.1.2   | Load-tunable VGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15   |

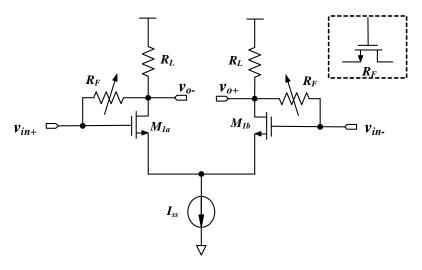

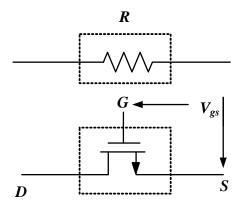

|    |         | 2.1.3   | Feedback-tunable VGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17   |

|    |         | 2.1.4   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18   |

|    | 2.2     | Expon   | nential function approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19   |

|    |         | 2.2.1   | Exponential function using transistor intrinsic performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19   |

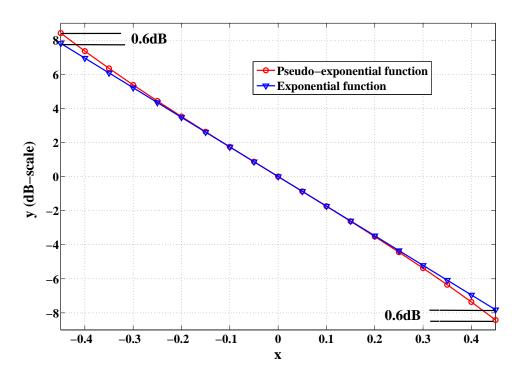

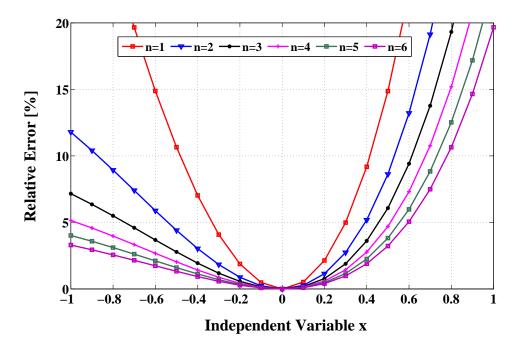

|    |         | 2.2.2   | Pseudo-exponential function based on Taylor expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20   |

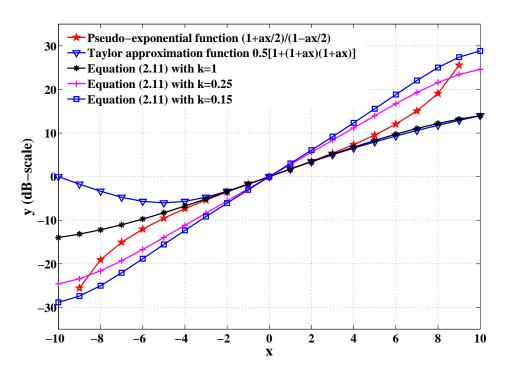

|   |                                 | 2.2.3                                                                                      | Exponential-function realization based on a linear function                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                                        |

|---|---------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|   | 2.3                             | Broad                                                                                      | oand VGA techniques                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                        |

|   |                                 | 2.3.1                                                                                      | Cascode topology                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                        |

|   |                                 | 2.3.2                                                                                      | Capacitive degeneration                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                        |

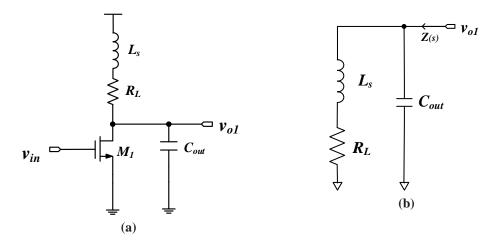

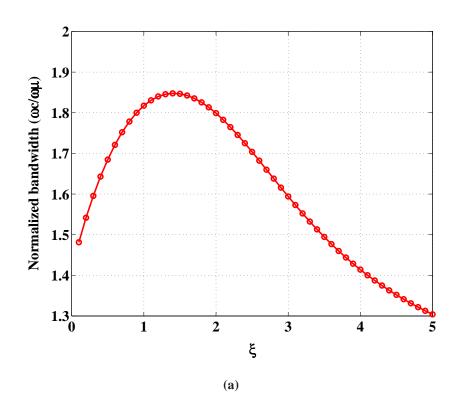

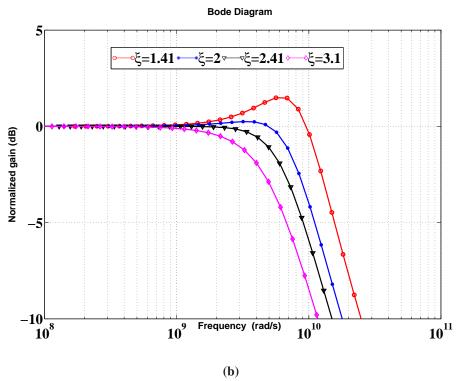

|   |                                 | 2.3.3                                                                                      | Shunt peaking                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                        |

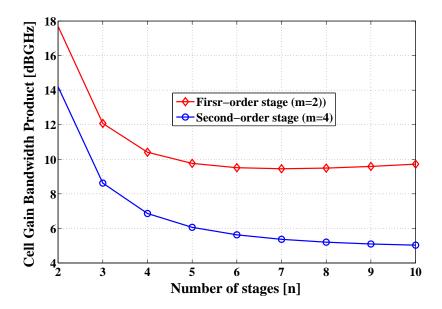

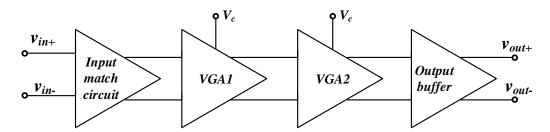

|   | 2.4                             | Bandw                                                                                      | vidth of a cascaded VGA chain                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30                                                                        |

|   | 2.5                             | Conclu                                                                                     | asions                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31                                                                        |

| 3 | Bro                             | adband                                                                                     | VGAs for an SKA receiver                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                        |

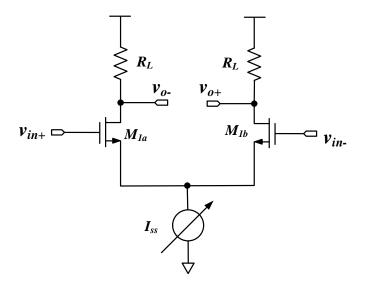

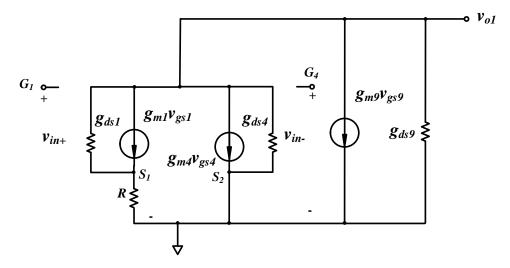

|   | 3.1                             | Propos                                                                                     | sed VGA circuit unit cell                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                                        |

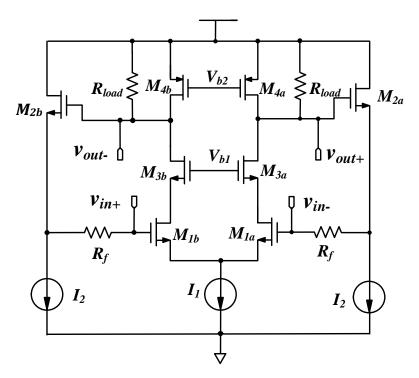

|   | 3.2                             | Propos                                                                                     | sed VGA circuit I                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                        |

|   |                                 | 3.2.1                                                                                      | VGA schematic design                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                        |

|   |                                 | 3.2.2                                                                                      | Two-stage cascaded VGA chain                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39                                                                        |

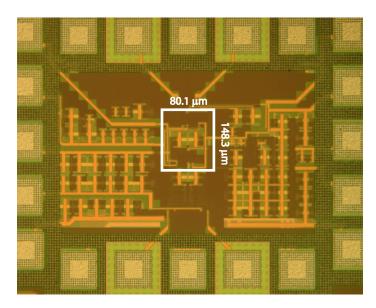

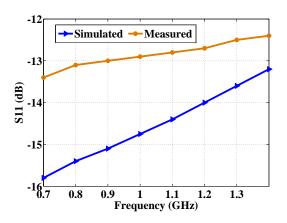

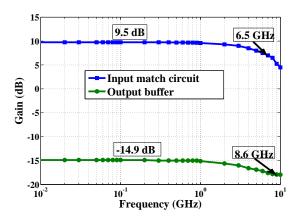

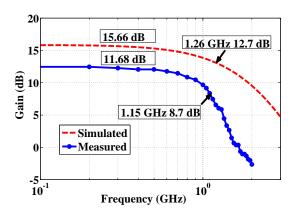

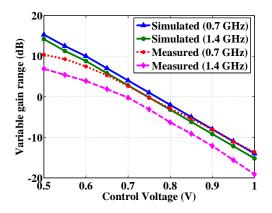

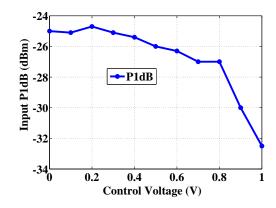

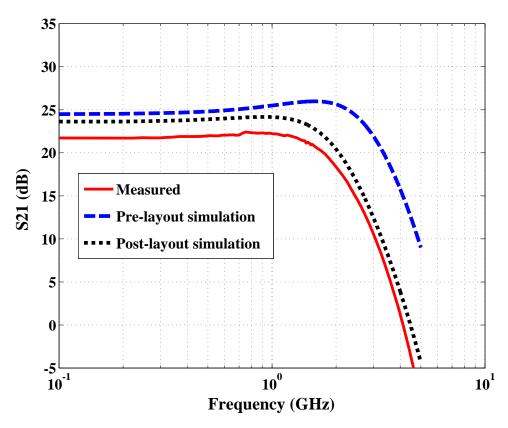

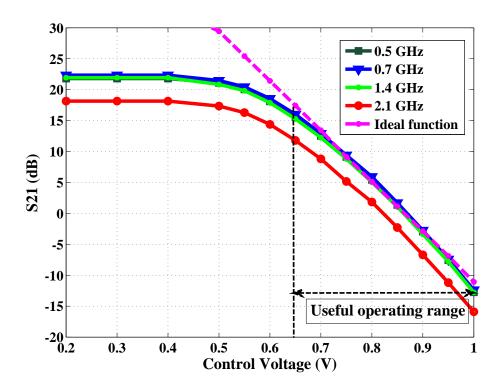

|   |                                 | 3.2.3                                                                                      | Simulation and measurements results                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                        |

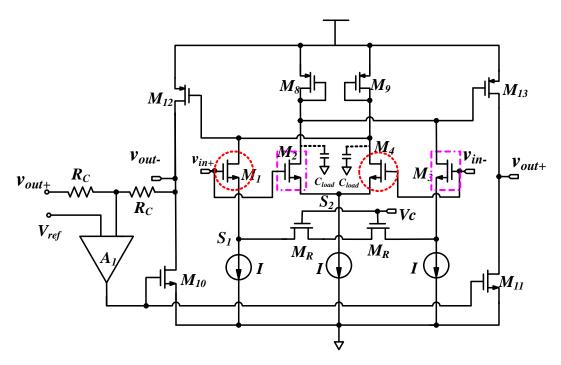

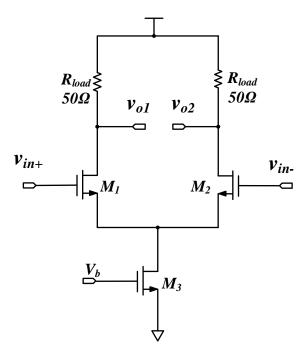

|   | 3.3                             | Propos                                                                                     | sed VGA circuit II                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                                        |

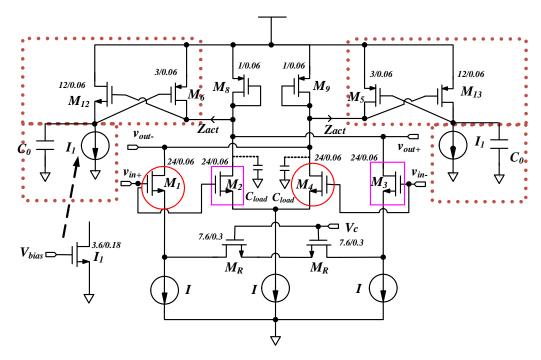

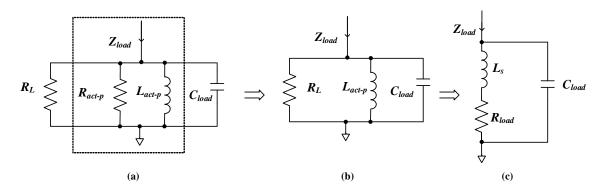

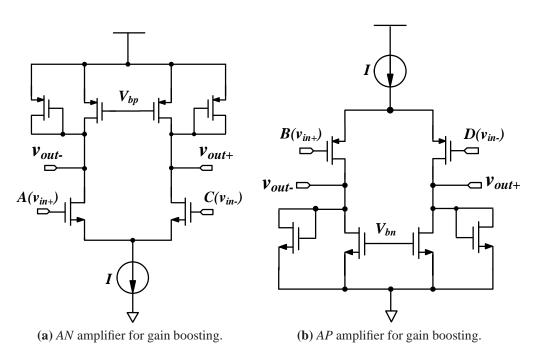

|   |                                 | 3.3.1                                                                                      | Active inductor-load VGA                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                        |

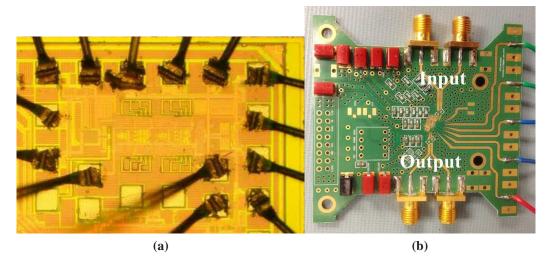

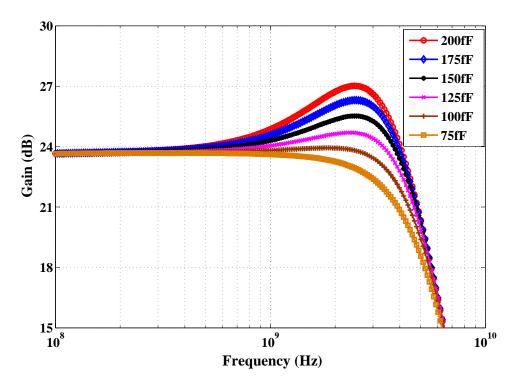

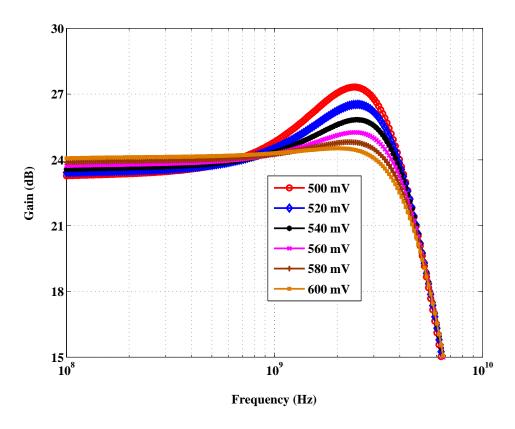

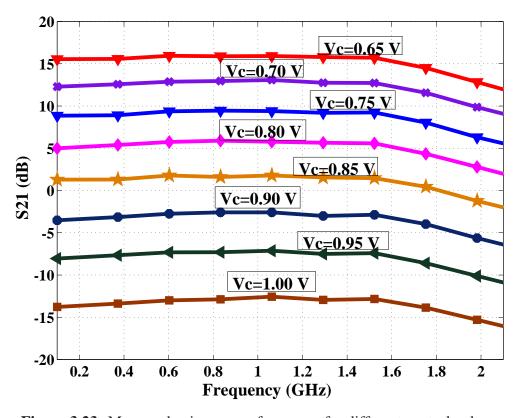

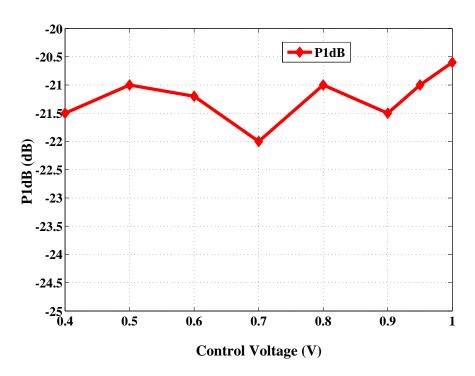

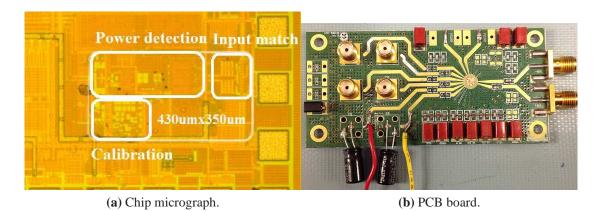

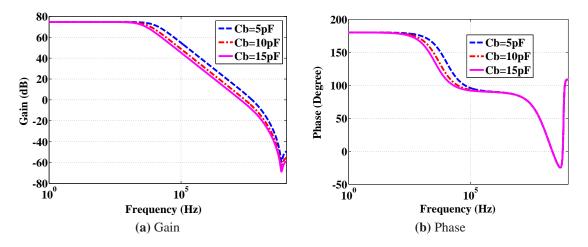

|   |                                 | 3.3.2                                                                                      | Simulation and measurement results                                                                                                                                                                                                                                                                                                                                                                                                                               | 48                                                                        |

|   | 3.4                             | Conclu                                                                                     | isions                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53                                                                        |

|   |                                 |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

| 4 | Pov                             | ver dete                                                                                   | ction techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                        |

| 4 | <b>Pov</b> 4.1                  |                                                                                            | ction techniques mental power detection methods                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

| 4 |                                 |                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                        |

| 4 |                                 | Funda                                                                                      | mental power detection methods                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56<br>56                                                                  |

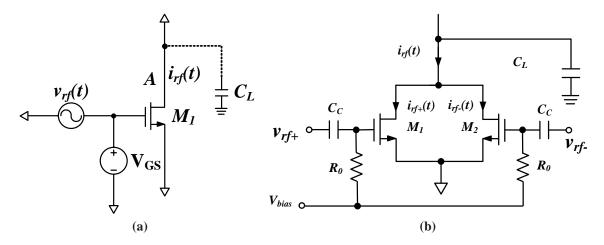

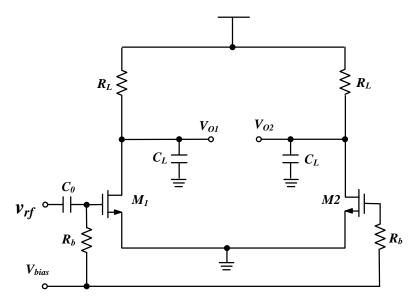

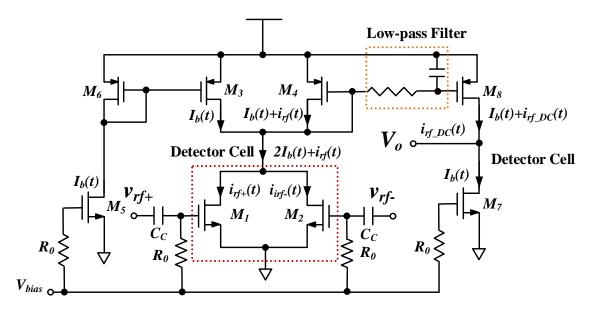

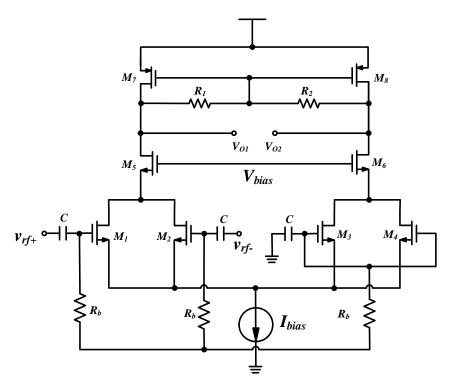

| 4 |                                 | Funda: 4.1.1                                                                               | mental power detection methods                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56<br>56<br>57                                                            |

| 4 |                                 | Funda: 4.1.1 4.1.2                                                                         | mental power detection methods                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56<br>56<br>57<br>58                                                      |