## UNIVERSITY OF CALGARY

# Optimization of Voltage Steps in Cascaded H-Bridge Inverters

by

.

Arif Al-Judi

# A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE

#### DEGREE OF MASTER OF SCIENCE

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# CALGARY, ALBERTA

## SEPTEMBER, 2008

© Arif Al-Judi 2008

# UNIVERSITY OF CALGARY FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled "Optimization of Voltage Steps in Cascaded H-Bridge Inverters" submitted by Arif Al-Judi in partial fulfilment of the requirements for the degree of Master of Science.

Supervisor, Dr. Ed Nowicki Dept. of Electrical and Computer Engineering

Norm Bartley Dept. of Electrical and Computer Engineering

Dr. John Nielsen Dept. of Electrical and Computer Engineering

Dr. Peter Goldsmith Dept. of Mechanical and Manufacturing Engineering

2008 Date

#### Abstract

In this thesis the design of multilevel cascaded H-bridge inverter topologies that can reduce harmonic distortion in the output waveform is investigated. The harmonic reduction methods investigated may be applicable to the integration of renewable energy sources in an electric utility power system. In multilevel inverters, a reduction in total harmonic distortion can be achieved by increasing the number of levels in the inverter output staircase waveform. The two approaches investigated avoid the use of an increased number of dc voltage sources or active semiconductor components. Both techniques are analyzed and harmonic equations are derived. Also presented is a gradient based optimization to determine the switching instances of transistor gating functions in order to minimize total harmonic distortion of the inverter output voltage waveform.

# Acknowledgements

,

I would like to express my sincere thanks to my supervisor Dr Ed Nowicki for his kind guidance and supervision throughout the work done in this thesis.

My thanks are also due to my fellow students Nacer Benaifa and Hussien Bierk at the University of Calgary for their help and assistance during the preparation of this work. Dedication

To my beloved family

.

| Approval Page                                                            | ii                   |

|--------------------------------------------------------------------------|----------------------|

| Abstract                                                                 | iii                  |

| Acknowledgements                                                         | iv                   |

| Dedication                                                               |                      |

| Table of Contents                                                        |                      |

| List of Tables                                                           |                      |

| List of Figures and Illustrations                                        |                      |

| List of Symbols                                                          |                      |

|                                                                          | 11                   |

| CHAPTER ONE: INTRODUCTION                                                | 1                    |

| 1.1 Developments in Power Electronics and Renewable Energy Sources       |                      |

| 1.2 Harmonics in Power Systems                                           |                      |

| 1.3 Thesis Outline                                                       |                      |

|                                                                          |                      |

| CHAPTER TWO: LITERATURE REVIEW                                           | 7                    |

| 2.1 Introduction                                                         |                      |

| 2.2 Two-Level and Multilevel Inverters                                   |                      |

| 2.3 Topologies and Structures of Multilevel Inverters                    |                      |

| 2.4 Modulation Techniques                                                |                      |

| 2.5 Harmonics in a Multilevel Inverter Output                            |                      |

| 2.6 Advantages of Multilevel Inverters                                   |                      |

| 2.7 The Work Presented in This Thesis                                    | 20<br>つつ             |

|                                                                          | , <i>La La</i>       |

| CHAPTER THREE: THE INVESTIGATED TECHNIQUES                               | 24                   |

| 3.1 Introduction                                                         |                      |

| 3.2 The Cascaded H-bridge Voltage Source Multilevel Inverter Structure   |                      |

| 3.3 The Technique of Single Polarity Voltage Addition in Each Half Cycle |                      |

| 3.4 Harmonic Analysis of the First Technique                             |                      |

| 3.5 The Technique of Dual Polarity Voltage Addition in Each Half Cycle   |                      |

| 3.6 Harmonic Analysis of the Second Technique                            |                      |

| 3.7 Analyzing the Effect of Waveform Parameters on THD                   | <del>1</del> 0<br>17 |

|                                                                          |                      |

| 3.8 Searching for the Minimum THD Using a Search Algorithm               |                      |

| CHAPTER FOUR: PRACTICAL IMPLEMENTATION OF THE SYSTEM                     | 61                   |

| 4.1 Introduction                                                         |                      |

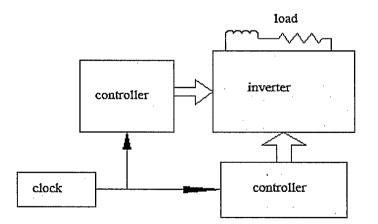

| 4.2 Block diagram and General Description                                | 01<br>60             |

| -                                                                        |                      |

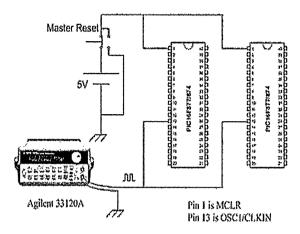

| 4.3 Instruments Used in the Experimental Set-Up                          | 03                   |

| 4.4 The Microcontroller PIC 16F877                                       |                      |

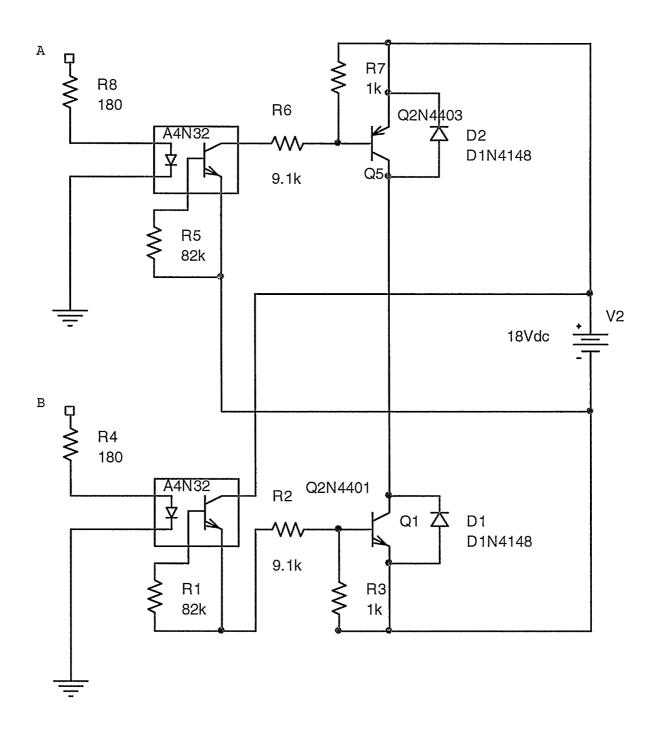

| 4.5 Practical H-Bridge Implementation                                    |                      |

| 4.6 Practical Results                                                    |                      |

| 4.7 Discussion                                                           | 72                   |

| CHAPTER FIVE: CONCLUSIONS AND FUTURE WORK                                | 70                   |

| 5.1 Conclusions                                                          |                      |

| 5.2 Suggestions for Future Work                                          |                      |

|                                                                          |                      |

# **Table of Contents**

| REFERENCES                                     | 82  |

|------------------------------------------------|-----|

| APPENDIX A: PIC16F877 ASSEMBLY LISTING         | 90  |

| APPENDIX B: MATLAB LISTING                     | 93  |

| APPENDIX C: VERIFICATION OF HARMONIC EQUATIONS | 101 |

.

.

# List of Tables

.

| Table (3.1) H-bridge switching states                                        | 27 |

|------------------------------------------------------------------------------|----|

| Table (3.2) Pattern of step values in the first technique                    | 36 |

| Table (3.3) Pattern of Step Voltage Values in the Second Technique           | 43 |

| Table (4.1) Pattern of the States for the Switching Components of the System | 70 |

`

# List of Figures and Illustrations

| Fig. 2.1: PWM technique to generate a sinusoidal signal. (a) output generating process (b) output voltage waveform |

|--------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2: Typical waveform of a multilevel inverter output (Voltage is normalized) 11                              |

| Fig. 3.1 Cascaded H-bridge multilevel inverter                                                                     |

| Fig. 3.2 The H-bridge switching circuit                                                                            |

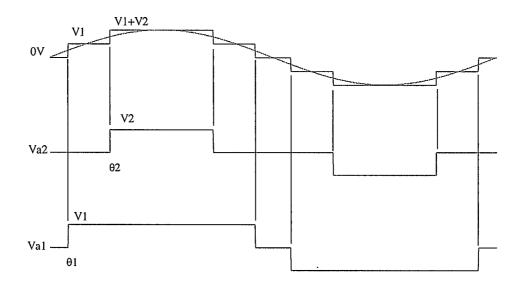

| Fig. 3.3 Output waveform and switching pattern of Va1 and Va2 in the conventional approach                         |

| Fig. 3.4 Output waveform and switching pattern of Va1 and Va2 using the first technique                            |

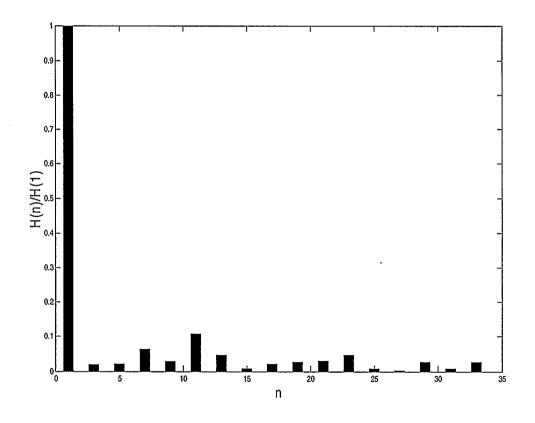

| Fig. 3.5 Spectrum of the conventional staircase waveform for two voltage sources 33                                |

| Fig. 3.6 Spectrum of the staircase waveform for two voltage sources generated by the first technique               |

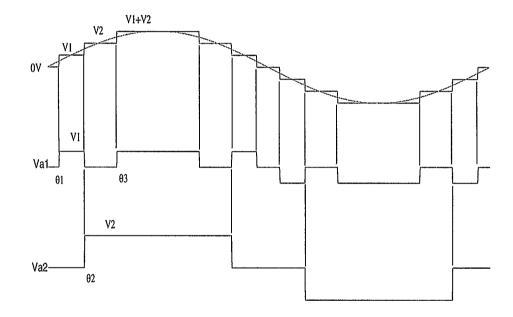

| Fig. 3.7 Output voltage waveform and switching pattern for the second technique 42                                 |

| Fig. 3.8 spectrum of the output waveform generated by the 2 <sup>nd</sup> technique for two voltage sources        |

| Fig. 3.9 A three level waveform having single transition angle $\theta$                                            |

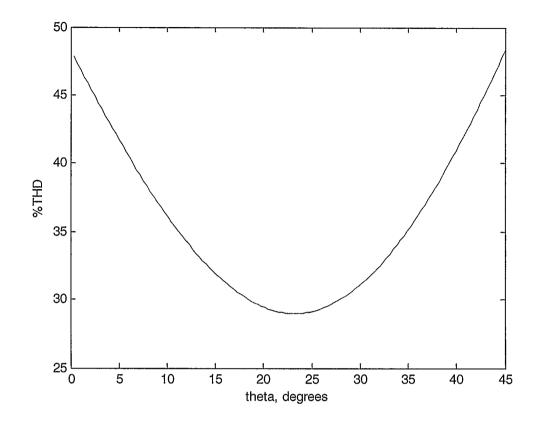

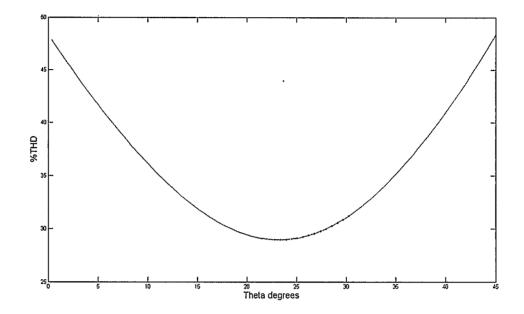

| Fig. 3.10 THD of a three level voltage waveform versus the angle $\theta$                                          |

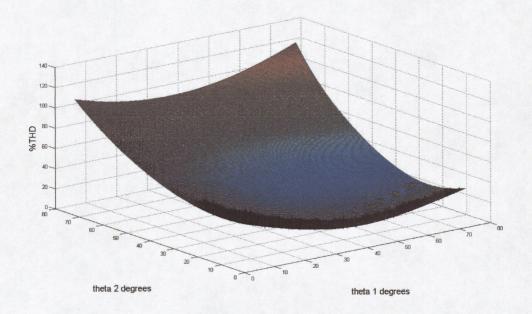

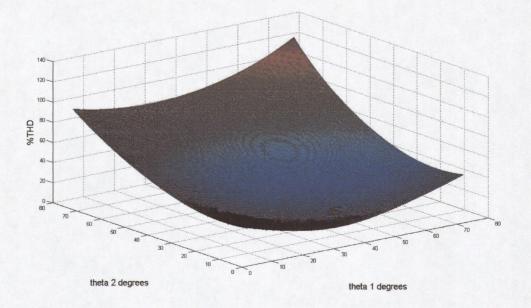

| Fig 3.11 THD versus the two angles in a five level waveform                                                        |

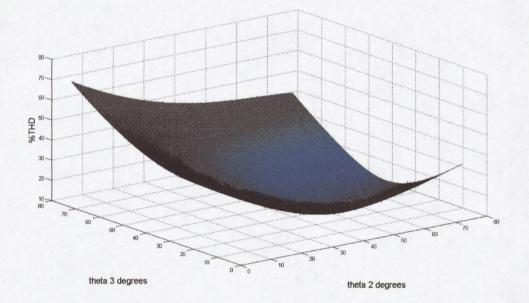

| Fig. 3.12 THD with $\theta$ 3 fixed at 72.00 ° for a seven level waveform                                          |

| Fig. 3.13 THD for a seven level waveform with $\theta$ 1 fixed at 9.00 °                                           |

| Fig. 3.14 Search path for minimum THD in a three level waveform                                                    |

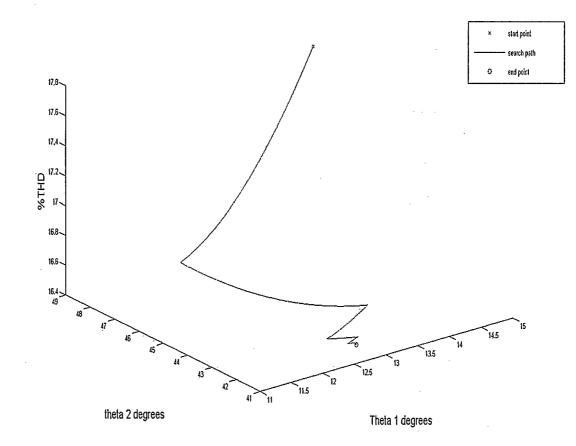

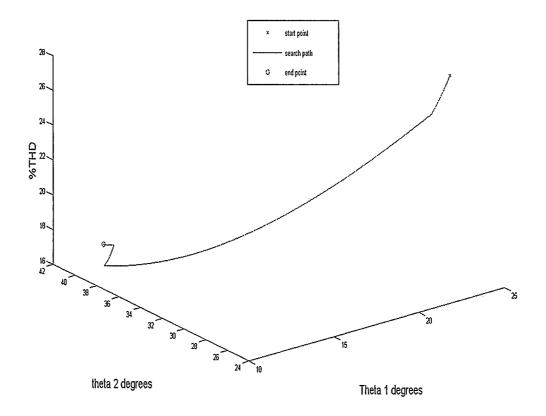

| Fig. 3.15 Search path for a five-level waveform with $\mu$ =0.0001 rad                                             |

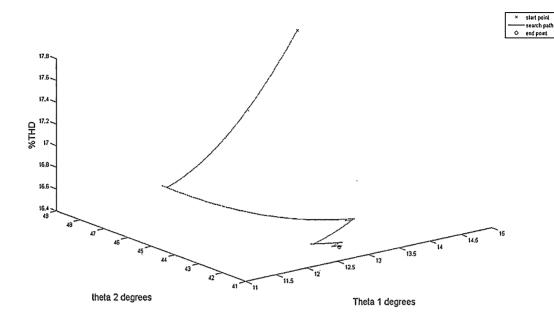

| Fig. 3.16 Search path for a five-level waveform with $\mu$ =0.001 rad                                              |

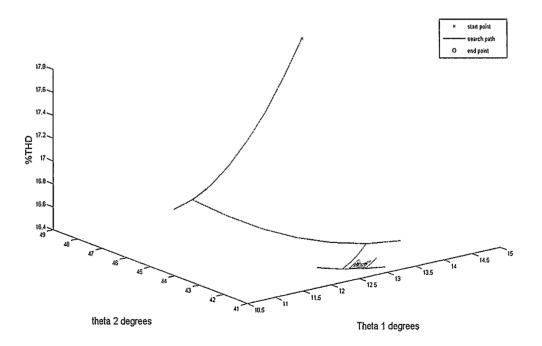

| Fig. 3.17 Search path for a five-level waveform with $\mu$ =0.01 rad                                               |

| Fig. 3.18 Search path for a five-level waveform with a different starting point 60                                 |

| Fig. 4.1 Block diagram of the practical setup                                                                      |

| Fig. 4.2 One leg of the H-bridge used in the practical implementation of the system   | 66 |

|---------------------------------------------------------------------------------------|----|

| Fig. 4.3 Synchronizing the operation of the two microcontrollers                      | 68 |

| Fig. 4.4 Switching times for the practical set up (simulated waveform)                | 68 |

| Fig. 4.5 DC voltage sources and switches of the H-bridges of the system               | 69 |

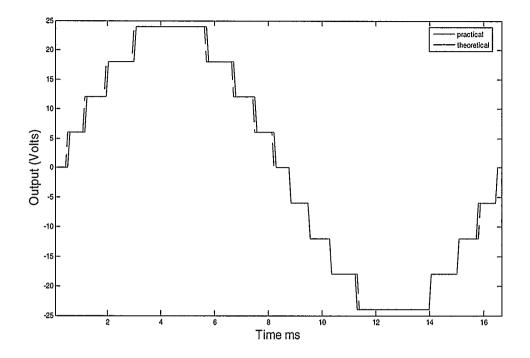

| Fig. 4.6 Experimental output staircase waveform of the implemented inverter           | 72 |

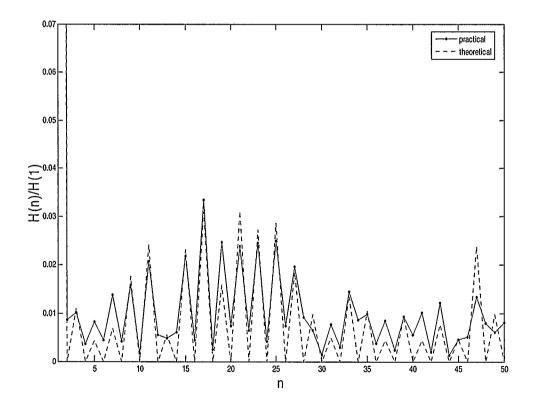

| Fig. 4.7 Spectrum of the output waveform of the experimental set up                   | 73 |

| Fig. 4.8 One cycle of the practical and theoretical outputs                           | 74 |

| Fig. 4.9 Comparison of the spectrum of the practical and theoretical outputs          | 74 |

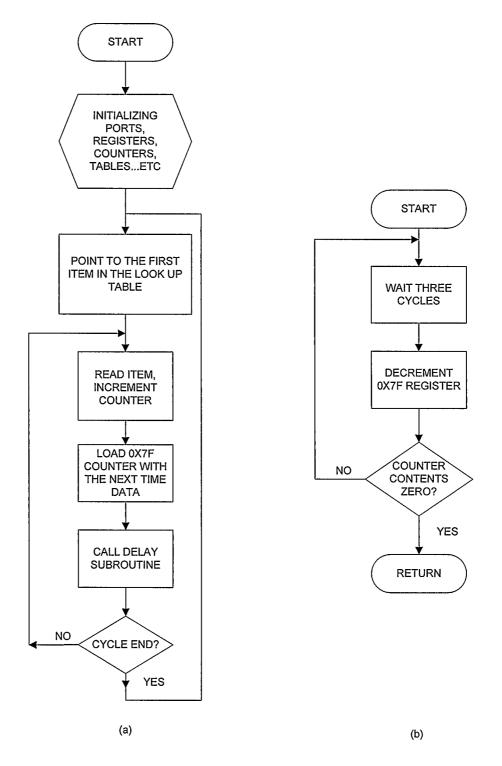

| Fig. A.1 Flow chart of (a) the main PIC 16F877 program; (b) the time delay subroutine | 92 |

.

# List of Symbols

| Symbol      | Definition                                                           |

|-------------|----------------------------------------------------------------------|

| AC          | Alternating current waveform                                         |

| DC          | Direct current waveform                                              |

| PWM         | Pulse width modulation                                               |

| Vdc         | Value of dc voltage source                                           |

| THD         | Total harmonic distortion                                            |

| Vi          |                                                                      |

|             | Value of the ith voltage source<br>Peak value of the fundamental     |

| H(1)<br>RMS |                                                                      |

|             | Root mean square value of an ac waveform                             |

| θi          | The ith switching angle in the first quarter of a staircase waveform |

| IGBT        | Insulated gate bipolar transistor                                    |

| IGCT        | Integrated gate commutated thyristor                                 |

| GTO         | Gate turn-off thyristor                                              |

| AI          | Artificial intelligence                                              |

| NN          | Neural network                                                       |

| SPWM        | Sinusoidal pulse width modulation                                    |

| IPD         | In-phase disposition modulation                                      |

| POD         | Phase opposite disposition modulation                                |

| APOD        | Alternative phase opposite disposition                               |

|             | modulation                                                           |

| THPWM       | Third harmonic pulse width modulation                                |

| DSP         | Digital signal processor                                             |

| EMI         | Electromagnetic interference                                         |

| ASD         | Adjustable speed drive                                               |

| dv/dt       | Rate of change of the voltage with time                              |

| VAr         | Reactive power regulation                                            |

| Vai         | The output voltage of the ith H-bridge circuit                       |

| v(t)        | Output voltage of the multilevel inverter                            |

| Si          | The ith switch in a multilevel inverter                              |

| M           | The total number of dc voltage sources in the                        |

| 141         | multilevel inverter                                                  |

| H(n)        | Amplitude of the nth harmonic of the                                 |

| 11(11)      | waveform                                                             |

| ω           | Angular frequency of a sinusoidal waveform                           |

| CPU         | Central processing unit                                              |

| PIC         | The microcontroller used in the practical set                        |

| ~~~         | up of the system                                                     |

| RISC        | Reduced instruction set computer                                     |

| EEPROM      | Electrically erasable programmable read only                         |

|             |                                                                      |

| CMOS        | memory<br>Complementary metal oxide semiconductor                    |

| 0.1100      | complementary metal oxide semiconductor                              |

| RAM   | Random access memory                    |

|-------|-----------------------------------------|

| di/dt | Rate of change of the current with time |

| C     | Capacitor                               |

| L     | Inductor                                |

| R     | Resistor                                |

| .m    | Extension for executable MATLAB files   |

•

#### **Chapter One: Introduction**

## 1.1 Developments in Power Electronics and Renewable Energy Sources

Power electronics is concerned with the system engineering of power converters that contain semiconductor switching components. A power converter transforms voltage and/or current waveforms from one form (e.g. low or high ripple dc, low or high frequency ac, square or sinusoidal ac, etc.) to another form [1]. Over the past fifty years there has been rapid growth in power electronics research, as new high power, light weight; high efficiency power semiconductor components have replaced many of the older rotary machine power converters and heavy bulky transformers and inductors. The growth of the power electronics industry is likely to grow more rapidly in the foreseeable future [2]. Research work in the power electronics discipline, and industry applications of high power converters, are gaining more attention and support from community, industry and government institutions, especially as related to renewable energy sources such as biomass electric power generation, photo-voltaic (solar) cells, and wind electric power systems that employ novel rotary generators [3].

The field of high power semiconductor technology and related applications plays a great role in industry and our everyday life. Processes, appliances and vehicles that were once primarily mechanical in nature are now moving toward hybrid electro-mechanical designs, or in some cases, all-electrical designs. Not long ago, active solar cells were quite costly and considered useful for limited applications such as satellites orbiting the earth. However, achievements in semiconductor solar cells have made it possible to introduce higher efficiency and lower cost components. A typical commercial solar panel today has an efficiency of about 20% at a retail cost of approximately \$5000 per kW. Recently, a 40% efficiency solar panel was introduced which could lead to photovoltaic systems that can produce energy at a cost of around 10 cents per kilowatt-hour<sup>1</sup>. Wind electric power generation is becoming accepted as the most economic and environmentally sensitive form of alternative energy (though environmental issues require a balanced multi-faceted solution). One important role of power electronics in renewable energy systems is the conversion of dc voltage or current into near-sinusoidal ac power. In some cases, such as wind electric power, a semiconductor based rectifier is employed as a front-end power converter to create a dc-link. In particular, power electronics is finding applications in the conversion of electrical power from active solar panels or wind generators for the purpose of integrating that power into an electric utility grid. Such an application, sometimes referred to as distributed generation, is gaining popularity around the world, in Canada and in Alberta.

Projects exploiting natural energy resources are receiving both national and international attention in recent years. Right now, Great Britain is planning to use the tidal sea waters as an alternative source of energy<sup>2</sup>. Project planners hope this will be the basis for more projects perhaps with a goal of obtaining 20% of the country's need of electrical power

<sup>&</sup>lt;sup>1</sup> "Solar Cell Breaks the 40% efficiency Barrier" Renewable Energy World.Com online, Dec. 7 2006 http://www.renewableenergyworld.com/rea/news/story?id=46765&src=rss

<sup>2</sup>The Rise of British Sea Power, *The Independent*, UK, 23 March 2008,

http://www.independent.co.uk/environment/green-living/the-rise-of-british-sea-power-799630.html

from a marine source. Here in Calgary, ENMAX is working on some projects, including wind powered electrical generation, which can increase "the propagation of green technology", as stated by the president of the company<sup>3</sup>.

As more "green" electric power sources are being developed, one of the key technical issues is the research and development of high-performance, efficient, reliable, and cost effective means to convert power from a dc voltage (as is available from some alternative energy sources) into an ac power form, capable of being connected to the ac power grid, or driving off-line loads such as ac motors or appliances. This thesis addresses the need for high performance dc to ac power converters.

# 1.2 Harmonics in Power Systems

The system that converts power from a dc form into an ac form is the power inverter [1]. Much research work has been performed to improve the basic inverter structure or enhance the quality of the output waveform of these inverters. Among the many inverter structures available in the inverter family is the multilevel inverter. The work in this thesis is devoted to the improvement of the techniques used in multilevel inverter design to reduce the harmonic content of the output waveform of these inverters. Ideally, the output of an inverter should be purely sinusoidal, but in practice the power waveform contains unwanted frequency components.

Motors, electronic equipment and appliances are affected differently by harmonics; depending on their internal circuitry and method of operation. For example, incandescent lights and most types of household heaters and stoves are not affected at all<sup>4</sup>. On the other hand, induction motors windings can be overheated by harmonics, causing degradation of insulation and loss of life. Harmonics in an electrical grid system may overload electrical power distribution equipment; like transformers, and resonate with power correction capacitors and are responsible for other undesirable effects [4].

The IEEE 519 Standard gives specifications for accepted levels of harmonics in power systems. For example, according to this standard [4], a maximum of 5% Total Harmonic Distortion in a given voltage supply is regarded acceptable in the petrochemical industry, with no single harmonic exceeding 3% of fundamental. The IEEE 519 Standard and emerging standards provide industry and academia with motivation to improve the quality of ac power inverters.

With recent advances in the field of multilevel inverters [1,3] it is possible for multilevel inverters to meet the IEEE 519 Standard with fewer dc sources. In this thesis we investigate these recent advances and provide harmonic analyses and suggest a gradient based technique to optimize the gating function of the transistors in a multilevel inverter with the objective of minimizing total harmonic distortion (THD).

<sup>&</sup>lt;sup>4</sup> "Harmonic Distortion in the Electric Supply System" University of Wollongong, Integral Energy Technical Note 3, March 2000. http://www.elec.uow.edu.au/iepgrc/files/technote3.pdf

#### **1.3** Thesis Outline

Following Chapter One, the thesis is divided into four more chapters. Chapter Two presents a literature survey of the main research trends in the field of the multilevel inverter design. The various improvements and advances in design, topologies, modulation techniques and harmonic reduction procedures are reviewed. The three main topologies are introduced in brief. Modulation techniques are reviewed in general. Advantages and applications of the multilevel inverter are introduced. No mathematical treatment of the subject is given in this chapter.

In Chapter Three, circuit details and mathematical analysis of two techniques [1,3] are presented (independently derived by the author, but also known in the literature). The main harmonic analysis equations and mathematical details to minimize harmonic distortion are described. Derivation of the harmonic equations for the presented techniques and simulation results done using MATLAB are given. The search for the values of angles that give minimum THD is presented using a gradient search technique.

Chapter Four provides details of the practical implementation of the proposed system. The implementation is done using bipolar transistors as switches and a microcontroller to activate and deactivate semiconductor switching operations. Experimental results are shown and compared to theoretical expectations. Chapter Five presents the conclusions of the thesis along with suggestions for possible future work.

, ·

.

#### **Chapter Two: Literature Review**

#### 2.1 Introduction

Multilevel inverters were introduced to industry in the early 1980s, although the concept of these converters was developed earlier in the 1970s [1]. The general concept is based on using a high number of active components to achieve power conversion in small voltage steps [2]. Since their first introduction, many design structures, topologies and modulation techniques have been devised as advancements to improve the performance of these power converters. What follows in this chapter is a look at the research work done by others on this kind of converter as improvements to their basic operation. More details on some of the topologies and techniques used are given in the next chapter. It is worthwhile to begin with some notes about the terminology used in the literature. The term inverter is used to define a circuit that converts a fixed dc voltage to an ac voltage (single or three-phase) with variable magnitude and frequency as used in motor drives, or with relatively constant magnitude and fixed frequency as might be used in grid-tie applications [3]. On the other hand, the term converter is sometimes used (especially in Europe) to refer to a circuit that could operate in an inverter or rectifier mode [1]. Below are definitions of two-level and multilevel inverters.

### 2.2 **Two-Level and Multilevel Inverters**

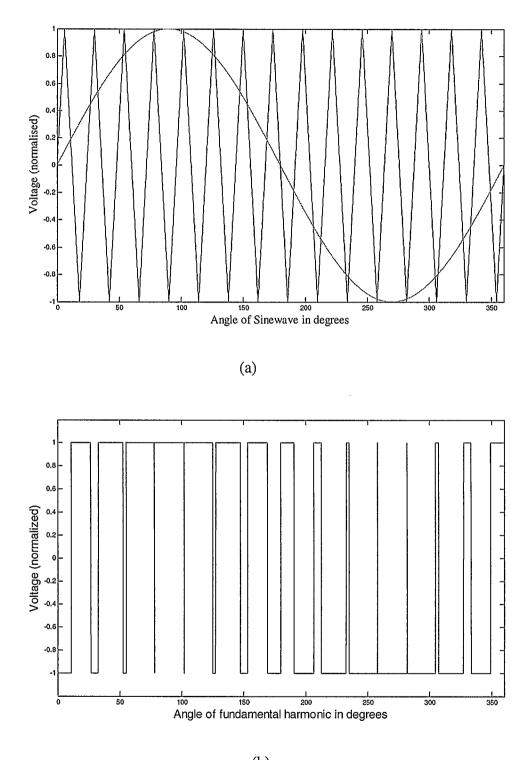

The term multilevel inverter is used in contrast with the two-level inverter. Fig. 2.1-a shows the signal waveforms related to the generation of the output waveform of a

conventional two-level inverter [4]. The technique used here, as is commonly used in industry, is pulse width modulation (PWM). The sinusoidal (reference or modulating) waveform is compared with a triangular (carrier) waveform. When the sinusoidal signal is greater than the triangular waveform, the output of the inverter is set (switched) to be equal to a constant dc voltage (Vdc), usually taken from a battery or a capacitor. When the magnitude of the sinusoidal signal is smaller than that of the triangular signal, the output of the inverter is set to be equal to the negative value of the same constant dc voltage (-Vdc). This process will yield the waveform shown in Fig. 2.1-b. The fundamental frequency component of this output waveform is the same as the sinusoidal modulating waveform. Actually, a harmonic-free sinusoidal component at the output of the inverter is the ultimate goal of the power conversion process. However, this sinusoidal component is usually distorted by harmonics due to the switching process. These harmonics will be "pushed up" to the higher end of the output spectrum by the carrier frequency, which is usually kept large enough for the harmonics to be filtered out by the appropriate filtering components. It is seen from the figure that the instantaneous value of the output waveform of the inverter alternates between the two dc values throughout one sinusoidal cycle of the fundamental sinusoidal reference waveform.

The total harmonic distortion (THD) is one of the criteria used as an indicator of the harmonic contents of a waveform. If H(1) is the peak value of the fundamental, and H(i) designates the peak value of the *i*th harmonic; then THD can be obtained using the following formula [4]:

(b)

Fig. 2.1: PWM technique to generate a sinusoidal signal. (a) output generating process (b) output voltage waveform.

$$THD = \sqrt{\frac{\sum_{i=2}^{\infty} \{H(i)\}^2}{\{H(1)\}^2}} \quad (2.1)$$

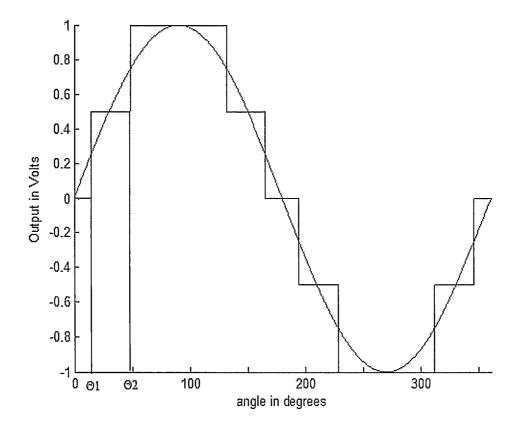

As the name implies, the output waveform of a multilevel inverter can have three voltage levels or more. A three level inverter has an output waveform that has one of the following voltage levels: Vdc, 0 or -Vdc. A quasi-square wave, or modified square wave as it is called in industry (common in sub-kilowatt inverters), is an example of a possible output of such an inverter [5]. A more advanced multilevel inverter output waveform is shown in Fig. 2.2. This is an example of a five level waveform. In the positive half cycle the output waveform is switched to a value, say V1 at an angle  $\theta$ 1, then at angle of  $\theta$ 2 the output is switched to V1+V2, where both values of V1 and V2 can be taken from two dc voltage sources or two capacitors. The values of V1 and V2 can be equal in magnitude, or they can have different values. The method with which this kind of signal is generated depends on the topology and structure of the inverter circuit. Many variations of switching angle values, number of voltage levels and specific values of the dc voltage sources contribute to the different design approaches and techniques used in the literature. Among the many research ideas and design techniques pursued so far, the work that is of interest to the research done in this thesis can be categorized into the following groups: the work done to introduce new topologies and structures, the research achievements to reduce harmonic contents of the output waveform; which is done either by reduction of the overall harmonic contents or by selective harmonic elimination approaches (which intend to eliminate a specific number of harmonic frequencies rather

**Fig. 2.2: Typical waveform of a multilevel inverter output (Voltage is normalized)** than reducing all the harmonic as a whole), modulation techniques, and the advantages of multilevel inverters. These subjects are addressed in the following sections.

# 2.3 Topologies and Structures of Multilevel Inverters

The early research work done by Nabae, Takahashi and Akagi [6] is a turning point in the improvement of multilevel inverters for practical applications [7 - 9]. The authors describe a three level converter that consists of two capacitor voltages in series and use the center tap as the neutral point. What they describe as neutral-point-clamped PWM

inverter is the basis for the diode-clamped topology of the multilevel inverter design. The diode-clamped topology can be used for a higher number of levels in the output waveform [7]. For a few years after 1980 no interest was shown in the literature in multilevel structures, but in the late eighties there was more research work done on these power converter systems [9].

Meynard and Foch described what they call "A novel versatile multilevel commutation cell" in 1992 [10]. The structure was introduced as being safer, simpler in control requirements and delivering purer output waveforms. The authors show how the new technique can be used in inverters and generalize its use to any number of switches. What was introduced in their work as a multilevel commutation cell was the basic structure for the flying capacitor multilevel inverter topology [1].

The third major improvement to the structure of the multilevel inverter is the cascadedinverter with separate dc voltage sources developed by Marchesoni, Mazzucchelli and Tenconni [11-13]. It was reported also by Tenconi, Carpita and Bacigalupo [9], referring to their structure as the "modular converter", differentiating it from the other multilevel converter structures. This inverter was introduced as a topology that can avoid extra clamping diodes or voltage balancing capacitors. Each dc source is associated with a fullbridge inverter consisting of four switching devices. The ac terminal voltages of different level inverters are connected in series to constitute the ac output of the multilevel inverter. This topology requires the least number of components among all multilevel converters to achieve the same number of voltage levels. In addition to these three basic topologies, other structures have been proposed. Many of the other topologies are not more than a minor modification to the original ones or they may use a combination of two or more of the basic topologies, which can be categorized as "hybrid" converter circuits [1]. One such structure consists of an H-bridge unit whose legs are made from diode clamped circuits [2], which is a combination of the cascaded Hbridge and diode clamped topologies. The "hybrid" term is sometimes used in conjunction with the use of different types of semiconductor switches in the same inverter topology. An example of that is the use of insulated gate bipolar transistors (IGBT) in the same inverter together with the integrated gate commutated thyristor (IGCT) for high-power applications [14]. This kind of design is tailored to multilevel inverters operating in a PWM mode, where some of the switching devices of the higher voltage cells have to operate at high frequency during some time intervals. The achievement is that the higher power cells operate at low frequency and only the lowest power cell operates with high frequency PWM. Another hybrid topology uses IGBTs, exploiting their voltage blocking capability, together with Gate turn-off (GTO) thyristors utilizing their switching speed and high voltage capabilities [15]. An attempt was made to give a unified definition to hybrid multilevel inverters as "those systems composed of several series-connected cells that present different dc voltage levels, modulation strategies, topologies, and/or semiconductor technologies operating in synergism" [16]. This definition was exemplified by a hybrid system that contains all three basic topologies in one inverter design. Another hybrid multilevel inverter for driving electric vehicles uses a single dc source at one level and capacitors for the rest of the levels [17].

This is done to overcome the difficulty of needing many dc sources for all the levels. Another topology was introduced concerning power requirements of the main circuit for a five level inverter that utilizes a special type of switch as an auxiliary component in the main power circuit [18]. The switch is inserted between the voltage source and the rest of the switching components in the circuit. The main goal of this configuration is to reduce the number of high power components in the inverter circuit.

Generally speaking, the hybrid techniques which use combinations of multilevel power converters give flexibility and versatility to the design structure of the system to fit the specific application it is intended to be used in. Finally, the symmetry property of these converters is worth mentioning. These converters can be classified according to the values of dc sources involved; if they are equal, the converter is called symmetric. If the dc sources used have different values, the term asymmetrical is used [19].

Other than the hybrid technology in multilevel inverters, specific kinds of techniques were sometimes developed to overcome certain drawbacks of the conventional approaches used in multilevel power converters. One approach uses a special kind of circuit that can charge a bank of capacitors in parallel and discharge them in series [20]. The main purpose of this topology is to overcome the requirements of separate dc voltage sources or a complicated capacitor-voltage balancing circuit for active power transfer. In another approach a fault diagnostic system based on artificial intelligence (AI) techniques is proposed [21]. The system uses neural network (NN) classification as a modeling tool and measures the output waveforms to identify the type and location of occurring faults

[22]. These efforts do not imply a real change in the basic topology design of these inverters; however they represent the progress in research work to improve the general design of these systems.

## 2.4 Modulation Techniques

Topologies and modulation techniques are sometimes very much related in multilevel inverter design to the extent that makes it difficult in some instances to differentiate between each other. However, two main modulation techniques can be found in most kinds of power converters: the non PWM techniques and the PWM techniques. The simplest and most obvious modulation scheme in a multilevel inverter system is the staircase (or step) modulation [3]. This is the one previously introduced and shown in Fig. 2.2; it is also known as the fundamental switching frequency modulation technique. Calculations can be done to find the specific values of the switching angles so as to minimize the harmonic contents of the resultant waveform. This is to be explained in more details later.

The method of PWM introduced earlier for the two-level inverter in Fig. 2.1-b can be extended to the multilevel concept. Carrara [23] developed the analysis of such a technique which is called sinusoidal pulse width modulation SPWM. To generate N odd levels of SPWM output, one modulating sinusoidal signal is needed, together with N-1 triangular carrier signals having the same frequency and amplitude and are aligned so that the bands they occupy are contiguous. The same number of carriers will be present above

and below the zero level. These carriers are compared instantaneously one by one with the sinusoidal signal in a fashion similar to bi-level PWM; the results of all the comparisons are added together to give the output multilevel PWM waveform. These carrier phases can be the same (in-phase disposition IPD), or they can be in phase for those above the zero value reference but in opposition with those below (phase opposite disposition POD), or they can be in opposition to each other alternatively (alternative phase opposite disposition APOD). For each of these three cases there is a different shape of output waveform. This description is actually for the kind of carrier based PWM technique categorized as the level shifted multicarrier SPWM technique. The other type of the SPWM technique is the phase shifted multicarrier modulation. In this kind of modulation all the carriers have the same frequency and amplitude, but there is a phase shift between any two adjacent carrier waves divided equally among the carriers to make a complete  $2\pi$  cycle for all the phase shift angles. The modulating sinusoidal signal is compared with carrier waves to generate the output waveform as usual.

In addition to the popular SPWM technique, another modulation strategy also emerged. The third harmonic PWM (THPWM) technique injects a third harmonic into the reference sinusoidal signal equal to 25% of the fundamental [1]. This process makes the reference voltage somewhat flattened in the middle and is done to make it possible to increase the fundamental output voltage without having the reference signal exceed the level of the carrier signals (the condition is called over-modulation). This additional third harmonic will be present at the output phase voltage with the same phase and magnitude, and it will be cancelled at the line to line voltage in a three phase system, which makes it applicable only in three phase systems [24]. Many other variations of the PWM technique have been reported in the literature [25-27]; they are mostly extensions of two-level and multilevel PWM techniques.

Most of the modulation techniques described so far can be used in different topologies of multilevel inverter design. However, a few exceptions have been reported [3].

## 2.5 Harmonics in a Multilevel Inverter Output

The output of a multilevel inverter, regardless of the modulation technique or topology used, is required to be a near-sinusoidal waveform free of harmonic distortion in the ideal condition, but this has never been the case. The desired sinusoidal output is distorted by higher order harmonics that are inherent in the output waveform due to the nature of the output generation process. Harmonic reduction is one of the main goals in the developments of any inverter design.

Two main trends can be observed in the literature regarding the harmonics problem in multilevel inverters. Harmonics can be minimized as a whole without emphasizing on specific frequency component, or a near-complete elimination of specific frequency components can be carried out [28, 29]. In the step modulation scheme, the switching angles of the staircase output waveform can be adjusted so as to minimize the harmonic content of the waveform. This can be done by running an exhaustive search method to

find the required angles, or by calculating the angles that will keep the area between the output staircase waveform and the sinusoidal desired output at a minimum [29]. Using this approach, it has been shown that for equal voltage steps of the staircase waveform, the optimal angles are found at the mean value of any two voltage steps. While for equal angle intervals and different voltage step values, the optimum angles are found to be at the mean value of any two corresponding angles. The criterion of equal area between the sinusoidal curve and the staircase waveform above and below the intersection point between the two has also been adopted [30]. Referring back to Fig. 2.2, an example of these two areas is the one below the sine wave trace and above the staircase after  $\theta 1$  until they intersect at 0.5 V level before  $\theta 2$ . It has been shown that by using this equal area criterion, the fundamental of the staircase waveform can reasonably resemble the sinusoidal modulation waveform. However, by minimizing the total harmonic distortion (THD) of the waveform, no elimination of specific harmonics can be realized.

Elimination of selected harmonic frequencies from the output waveform is carried out by sacrificing the minimization of THD. It is done usually to remove lower order harmonics which are closer to the fundamental, and use filtering circuits to attenuate the higher order harmonics in the output stage of the inverter. This approach is strengthened by the fact that the triplen harmonics (i.e. the odd multiples of the third harmonic) are already not present on the line-to-line voltage in a three phase system [28]. One of the pioneering works in harmonic elimination was carried out by Patel and Hoft [31]; they introduced research on harmonic elimination in two and three level inverters with thyristor firing

circuits. They developed a technique to eliminate some of the harmonics in a two-level PWM inverter by chopping the basic square wave output a number of times, and a fixed relationship was derived between the number of chops and possible number of harmonics that can be eliminated. The problem is that there will be a number of equations that have to be solved to eliminate the harmonics. These equations are nonlinear and transcendental in nature and not easy to solve. They can be solved by a trial and error process, or by numerical techniques. For a three level PWM output, the method adopted was the generating (instead of chopping) of identical but opposite polarity pulse train in each half-cycle.

In the staircase modulation of the multilevel inverter, harmonic elimination can be achieved by solving a set of nonlinear transcendental equations resulting from the Fourier analysis of the output waveform. The number of these equations is equal to the number of switching angles in the first quarter of the staircase output waveform (the uprising positive part before  $\pi/2$ ). The number of harmonics that can be eliminated is equal to the number of these equations minus one [32, 33]. For example, the number of equations for the waveform of Fig. 2.2 is just two, so only one harmonic can be eliminated in such a waveform. The solution of these transcendental equations is usually done by iterative methods. Many procedures to provide solutions to these nonlinear equations have been reported [34-37]. The problem with the numerical methods to solve the harmonic equations is that good initial guesses are required, moreover, solutions are not guaranteed. Usually the calculations of the values of the switching angles in stepped modulation is done off-line and stored in look up tables to be used in the control circuitry

of the inverter. Real time calculations are also possible and have been reported using a digital signal processor (DSP) to minimize the total harmonic distortion (THD) [38].

#### 2.6 Advantages of Multilevel Inverters

As stated before, the multilevel inverter design enables converting of power in small voltage steps rather than operating the electronic switches between the two extreme voltage levels in the bi-level PWM approach. The switches of the subsequent levels of the circuit are connected in series across the peak output voltage and the voltage drop is shared among the switches in the different levels. This technique enables the inverter to be used in applications that need high power (larger than 1 MW) and medium voltage (2.3 kV to 6.9 kV, i.e. several kVs), where an ac drive in the megawatt range is usually connected to the medium voltage network [8]. However, this is achieved at the expense of a higher number of switching circuits realized by active components required to cover the range of the output voltage waveform. The usual structure of these inverter circuits consists of layers or multiples of switches for each level added to the output voltage. The multiple switches in the multilevel inverter in fact permit an extra degree of switching freedom. Each switch still has the same limited switching frequency, but the overall switching frequency of the multilevel inverter becomes a multiple of that of the individual switches [39]. In addition to that, the fundamental switching scheme of these inverters (when every switch is activated once in a cycle) enables the use of these inverters in applications where low electromagnetic interference (EMI) is required [40].

The cascaded topology of these converters can fit many of the needs of all-electric vehicles using onboard batteries or fuel cells to generate the sinusoidal waveform to drive the main traction motor [41]. Multilevel converters have been utilized also in the design of hybrid electric vehicles where a high voltage battery pack is used as an alternative power source and energy storage device to provide drive power during acceleration and reserve energy during vehicle braking [42]. The high volt-ampere ratings of the multilevel inverters make them uniquely suited to meet the high power requirements of heavy duty trucks and military combat vehicles (>250 KW). Development of electric drive trains for these large vehicles will result in increased fuel efficiency, lower emissions, and better performance [43].

Multilevel inverters can be used in adjustable speed drives (ASD) to overcome some of the problems related to this application. Conventional ASDs use the two-level PWM technique to generate a voltage with variable frequency and amplitude in motor speed control applications. Many problems can arise from the high dv/dt caused by this kind of PWM operation, such as motor bearing failure and motor winding insulation breakdown, in addition to other problems [43]. Multilevel inverters overcome these problems because their individual devices have a much lower dv/dt per switching.

The use of these inverters in active control of reactive power (VAr) has been also reported [44]. Static VAr generators using multilevel inverters have been widely used as reactive power controllers of power systems to replace the conventional VAr compensators that use transformers. Transformers are the most expensive part in the system, need large area, encounter high losses, and are prone to failure. For these reasons, it is better to use multilevel inverters as a controlled reactive admittance and avoid the use of transformer based compensators. Recently, a cascaded multilevel-converter has been used to mitigate flicker; caused by feeder voltage fluctuation, in 40MVA electrical arc furnace and was successful in preventing problems in transmission and distribution systems [45].

One of the advantages of the cascaded multilevel inverter is its suitability for renewable energy sources. The cascaded multilevel inverter with its separate dc sources make it a good choice in applications that make use of renewable energy sources like wind turbines and photovoltaic cells [46]. These inverters are ideal for connecting to an ac grid with distributed energy sources composed of these renewable energy sources. This is a very important advantage in a time the world is seeking new sources of energy to save the environment and to compensate for the shortage in oil supplies and its increasing cost.

## 2.7 The Work Presented in This Thesis

It has been shown in this review chapter that one of the limitations of the multilevel inverter is the need for more components to increase the number of levels of the output waveform. Harmonic minimization in the output requires an increased number of output levels in the staircase waveform. A near-zero harmonic output can be achieved by having a very large number of levels in the staircase output; this requires a large number of isolated dc sources and an equivalent large number of active switching components. In the next chapter we review two approaches to tackle this problem [1,3]. The first one increases the possible number of levels in the output waveform without the need to increase the number of active components or dc sources. This is achieved by introducing a specific switching sequence of the active components; some constraints on the magnitudes of the dc voltage sources are imposed though. Simulation results are shown and compared to the conventional approach [47]. The second proposed method introduces a switching scheme that increases further the number of levels of the output waveform keeping the same number of voltage sources and active switching components; more constraints on the dc voltage source values are imposed to make this possible. Simulation results are shown together with practical implementation results [48]. The next chapter deals with the theory related to the design requirements and harmonic analysis of the investigated techniques.

#### **Chapter Three: The Investigated Techniques**

#### 3.1 Introduction

In this chapter, two techniques [1,3] are investigated that can minimize total harmonic distortion (THD) of the output waveform of the multilevel inverter. Both techniques (derived independently by the author) have been identified in the literature [1,3]. The topology adopted for these techniques is the cascaded H-bridge multilevel inverter structure. Both techniques increase the number of the staircase waveform levels of the inverter output without the need to increase the number of dc voltage sources or system components. To achieve that, the controller produces a specific switching sequence in each case. In doing this, some constraints on the values of the contributing dc sources are imposed. The details of these constraints depend on the specific requirement of each one of these two techniques. The first technique is included in the second one implicitly, i.e. the second one contains all the necessary requirements and procedures of the first one; in addition, it imposes more constraints on the values of the dc voltage sources and on their functioning nature to achieve the higher number of staircase levels in the output. A review of the conventional H-bridge multilevel inverter is given first; then details of both techniques are described with harmonic analysis and comparisons with the conventional approach.

### 3.2 The Cascaded H-bridge Voltage Source Multilevel Inverter Structure

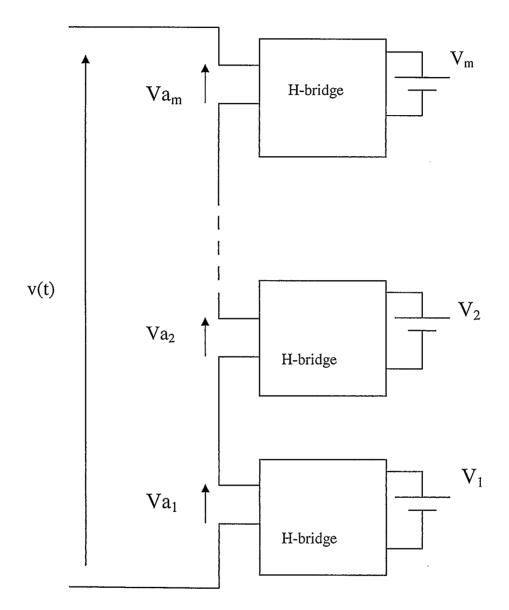

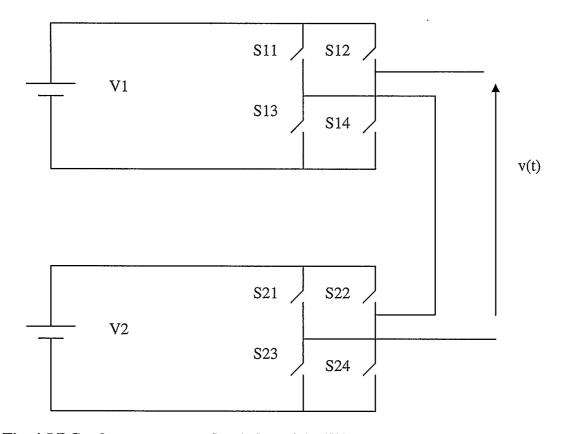

These inverters use more than one dc voltage source and a combination of several semiconductor switches to generate an ac staircase voltage waveform. To obtain a higher number of steps for the output waveform, more voltage sources and semiconductor components are required for the system. Fig. 3.1 depicts the block diagram for such a system [1]. The power of the system can be driven from a number of separate dc sources such as batteries, or capacitors fed from dc sources, or separate renewable energy voltage sources [8]. An H-bridge switching circuit is associated with each dc voltage source. For the i-th H-bridge, the dc source voltage Vi is the input of the i-th H-bridge which has an output voltage of Vai. The total number of these bridges is m which is usually equal to the number of dc sources. The output voltage of the i-th H-bridge, Vai, can take one of three voltage values: +Vi, -Vi, or zero volts. The output voltages of the m H-bridge circuits are connected in series to be added together to generate the output waveform of the inverter circuit represented simply as v(t).

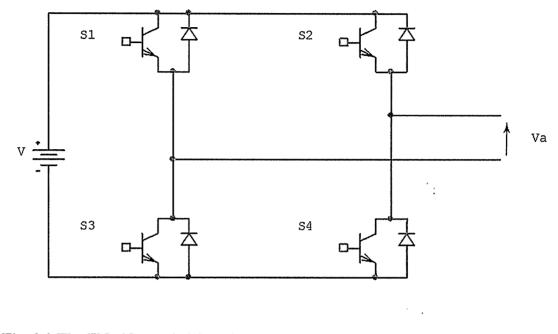

Each H-bridge circuit contains four semiconductor switches, as shown in Fig. 3.2. The output voltage of the bridge, Va, can be made equal to +V by turning on S2 and S3 while keeping S1 and S4 off. To make the output equal to -V; S1 and S4 have to be on while S2 and S3 have to be off. For a 0 volt output, S1 and S2 have to be off, while S3 and S4 on (or vice versa). Table 3.1 gives the switching conditions and the output of the bridge for each of these conditions [2], where a 1 means on (connected), and a 0 means off (disconnected). It can be noted that the switching condition of S1 is complementary to S3, and S2 and S4 are also operated in complementary fashion.

Fig. 3.1 Cascaded H-bridge multilevel inverter

The subsequent additions of the H-bridge circuit outputs generate the staircase waveform at the output of the inverter as shown in the waveform of Fig. (2.2), where this waveform can be generated by a two dc voltage source inverter. By properly selecting the switching angles of the steps in the output waveform; (e.g.  $\theta 1$  and  $\theta 2$  in the waveform of Fig. 2.2), control of the harmonic contents of the output waveform can be achieved [1].

Fig. 3.2 The H-bridge switching circuit

|    | -  | •  |    |    |

|----|----|----|----|----|

| Va | S1 | S2 | S3 | S4 |

| +V | 0  | 1  | 1  | 0  |

| -V | 1  | 0  | 0  | 1  |

| 0  | 0  | 0  | 1  | 1  |

| 0  | 1  | 1  | 0  | 0  |

|    |    |    |    |    |

Table (3.1) H-bridge switching states

The number of levels possible with the conventional approach in generating the output staircase waveform is 2m+1; where m is the total number of dc sources. This number

stems from the fact that each new level is generated by adding a new voltage source to the resultant waveform in every stage. Even with unequal voltage sources, there are still 2m+1 staircase levels in the output waveform. With the conventional control of the cascaded H-bridge the only way to increase the number of levels in the inverter output waveform is to increase the number of dc sources and their associated H-bridge circuits.

## 3.3 The Technique of Single Polarity Voltage Addition in Each Half Cycle

The first method investigated here has the capability of increasing the number of levels without the need to increase the number of dc sources or the semiconductor switching components; it is done by following a specific switching pattern for the outputs of the H-bridge circuits. The basic concept is to add to the conventional levels all the possible arrangements of voltage additions with the same polarity in each half cycle. An example of how to do this can be given by studying the case of the two voltage sources illustrated in Fig. 2.2. The conventional values of the levels in the positive half cycle are VIfollowed by V1+V2. Whether V1 is equal to V2 or not would not change anything in the total number of levels of the waveform. An additional level in the positive half cycle of the waveform can be added to have a total of seven levels in the whole cycle of the output waveform. This can be done by adding the level of voltage that is equal to V2 alone. The resultant waveform in the first quarter will consist of the levels V1, V2 and V1+V2, and the same voltage values having negative polarities will be present in the second half cycle, in addition to the zero voltage level. This operation can be carried out for any number of dc voltage sources in the system; however, some conditions may be imposed on the values of the dc voltage sources. These conditions can be deduced by inspecting the example of the two voltage sources given above and the cases of three or more sources. In order to increase the number of staircase levels, the value of V2 in the two source example is constrained by V2>VI. However, for equal step values, V2 has to be equal to 2VI, so that the step voltage will be equal to VI for the three steps in the positive half cycle, where the step value here is used to designate the difference between two consecutive levels. The technique can be applied for non equal step values as well, but equal step values will well approximate the desired sinusoidal output. To formulate the constraints on the values of the dc voltage sources, it is assumed that there are m dc sources with a set of voltage values {Vi}, i = 1, 2, ..., m. Each of these sources has a distinct voltage value, i.e.:

$$Vi \neq Vj$$

, for all i and j (3.1)

The dc source with the lowest voltage value will be given the notation V1, the next higher voltage source is V2, and so on. The highest value of the dc voltage sources in the system is Vm. This means

$$Vi < V(i+1), for all i$$

(3.2)

The other assumption imposed on the values of the dc voltage sources is:

$$V1 + V2 + \dots + Vi \neq V(i+1), for all i (3.3 - a)$$

This assumption is essential when the number of dc sources is higher than two. The importance of this assumption can be understood by studying the case of three dc sources, i.e. by having V3 in addition to V1 and V2. After the three step levels of V1, V2

and VI+V2, the next level of the output voltage waveform will be V3 alone; this value has to be different than the previous level, which is ensured by this equation. The same argument can be made when there are more than three voltage sources in the system. For more convenience, equation (3.3-a) can be put in a more appropriate form as follows:

$V1 + V2 + \dots + Vi < V(i+1)$ , for all i (3.3 - b)

This form is for convenience more than for necessity. It is needed to make the level of V3 higher than the level of V1+V2 in the three source example; not lower than it. The same applies to examples with a higher number of voltage sources. However, the form (3.3-a) of this equation is sufficient for the technique to work.

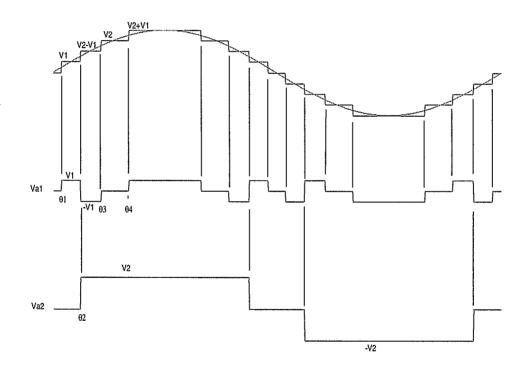

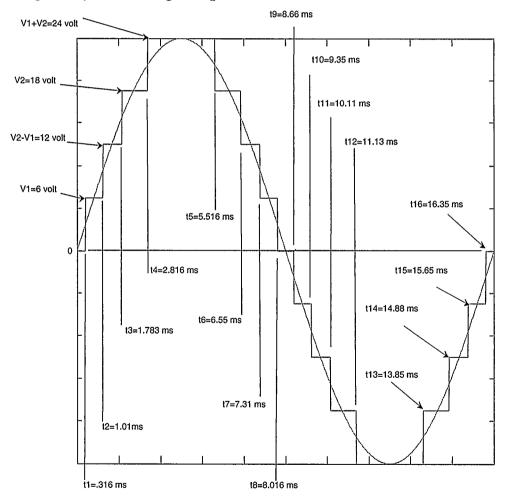

Fig. 3.3 Output waveform and switching pattern of Va1 and Va2 in the conventional approach

To illustrate how the technique works, the case of two voltage sources is presented here for the conventional and the current approach. Fig. 3.3 shows the output staircase waveform in the case of the conventional technique together with the switching pattern of the H-bridge circuits (the square wave components are discussed in the next section). The two levels in the positive half cycle are VI and VI+V2, where V2 is chosen here to be equal to VI for the equal step condition. Similar argument applies for the negative half cycle. The total number of levels is five. Fig. 3.4 depicts the output waveform and the variations of voltage outputs of the two H-bridge circuits Val and Va2 in the current technique. The additional two levels in this waveform is the +V2 and -V2 in the positive and negative half cycles, respectively. Here V2 is chosen to be 2V1 for equal step values. It is possible to add these two more levels of V2 alone since V2 is higher than V1; according to equation (3.2). It is clear that the total number of levels for the whole cycle is seven and not five, as was the case in the traditional approach. For a total number of mdc voltage sources, the total number of levels obtained for the whole voltage cycle will be  $(2^{m+1}-1)$  using the current technique; a considerable increase in the number of steps of the output waveform that will result in a great reduction in the harmonic distortion of the waveform, as illustrated below.

### 3.4 Harmonic Analysis of the First Technique

To study the harmonic contents of the output waveform, it is useful to find the equation of harmonics in the multilevel inverter first for the conventional approach to serve as a reference. In the waveforms of Fig. 3.3, the output staircase waveform is actually a resultant of the linear addition of two square waves as illustrated in Fig. 3.3; the number of square waves equal to the number of the stages (H-bridges) of the converter. The harmonic content of this waveform is obtained by adding the harmonic contents of these two square waveforms. For a fundamental frequency of  $\omega$ , and transition angles of  $\theta I$  and  $\theta 2$  for the two square waveforms, the equation for Fourier series expansion of the original staircase waveform can be given as follows [1]:

$$v(t) = \frac{\sin(n\omega t)}{n} \frac{4}{\pi} \sum_{n \text{ odd}} (V1\cos(n\theta 1) + V2\cos(n\theta 2)), \ n = 1,3,5 \dots (3.4)$$

Fig. 3.4 Output waveform and switching pattern of Va1 and Va2 using the first technique

It is noted that the even harmonics are zero due to the quarter wave symmetry property of the waveform. If the number of steps is defined as the number of transitions (or angles) in the output waveform prior to  $\theta = \pi/2$ , then for *m* number of dc sources there will be *m* steps. The Fourier coefficients, H(n), of the output waveform in this case can be given as [1]:

$$H(n) = \frac{4}{n\pi} [V1\cos(n\theta 1) + V2\cos(n\theta 2) + ... + Vm(\cos(n\theta m))] n = 1, 3, 5... (3.5)$$

For equal dc voltage source values of V, equation (3.5) becomes:

$$H(n) = \frac{4V}{n\pi} (\cos(n\theta 1) + \cos(n\theta 2) \pm ... \pm \cos(n\theta m)), \quad n = 1, 3, 5 \dots (3.6)$$

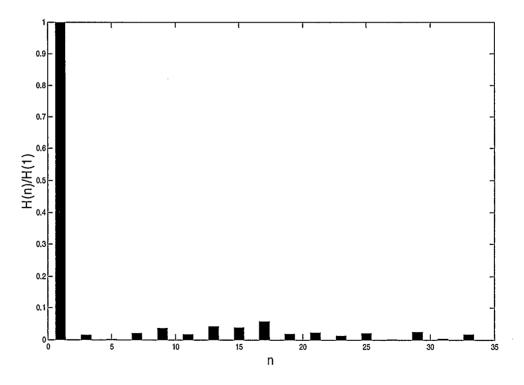

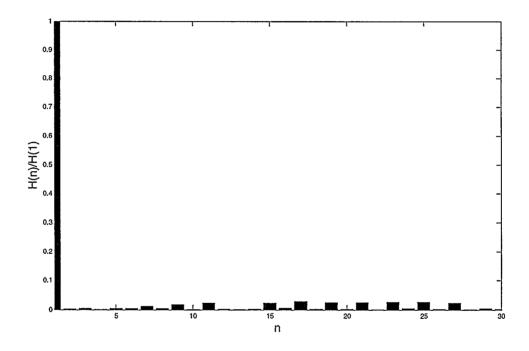

Fig. 3.5 gives the spectrum of the five level waveform of Fig. 3.3 normalized to the first harmonic. The highest magnitude after the fundamental appears at the eleventh harmonic and equals 10.7% of the fundamental. The THD value is found to be 17.56 %.

Fig. 3.5 Spectrum of the conventional staircase waveform for two voltage sources Equation (3.5) provides a basis to find the harmonic equation for the first technique. Every value of the step voltage is multiplied by a cosine function whose argument is n

multiplied by the angle that the transition is taking place at. The step voltage here is defined as the difference between the value of the current level voltage and the one before it. This is a very important result that is necessary to derive the harmonic equations for both of the techniques that are discussed here. For the current (first) technique, a careful inspection of the waveforms in Fig. 3.4 can be made. The important point to note here is the value of the step voltage between any two levels. This is the value that will be effective in formulating the harmonic equation for this condition. The three step values in this case are: VI at  $\theta I$ , (V2-VI) at  $\theta 2$ , and VI again at  $\theta 3$ . As stated before, the value of V2 in the diagram is chosen to be 2VI for the purpose of achieving equal voltage steps, however, the derivation will be done for the more general case of voltage values that comply with the equations (3.1)-(3.3) given above. According to the above discussion; the equation for Fourier coefficients of the output waveform in the case of two voltage sources and using the first technique can be given as:

$$H(n) = \frac{4}{n\pi} [V1 \{ \cos(n\theta 1) - \cos(n\theta 2) + \cos(n\theta 3) \} + V2 \cos(n\theta 2)],$$

$$n = 1, 3, 5 \dots (3.7)$$

By inspecting equation (3.7) and the transitions in Val and Va2 given in Fig. 3.4, it can be noted that the positive signs preceding  $cos(n\theta l)$  and  $cos(n\theta 3)$  in the first term of the equation that contains Vl correspond to the rising edges of Val at  $\theta l$  and  $\theta 3$ , respectively, while the negative sign preceding  $cos(n\theta 2)$  in the same term corresponds to the falling edge of Val at  $\theta 2$ . The second term in the equation that contains V2, has only a positive sign preceding  $cos(n\theta 2)$ ; since there is no falling edge for Va2 in the first quarter of the waveform. This same argument will hold true for the case of more than two dc voltage sources. For instance, in the case of three voltage sources, the equation of the Fourier coefficients will have the first term containing VI multiplied by seven cosine terms associated with the seven transitions of VaI in the first quarter of the waveform; each of these terms will have a positive or a negative sign reflecting its condition of transition; positive for a rising edge, and negative for a falling one, i.e. we will have the following equation:

$$H(n) = \frac{4}{n\pi} [V1 \{cos(n\theta 1) - cos(n\theta 2) + cos(n\theta 3) - cos(n\theta 4) + cos(n\theta 5) - cos(n\theta 6) + cos(n\theta 7)\} + V2 \{cos(n\theta 2) - cos(n\theta 4) + cos(n\theta 6)\} + V3 cos(n\theta 4)],$$

$$n = 1, 3, 5 \dots (3.8)$$

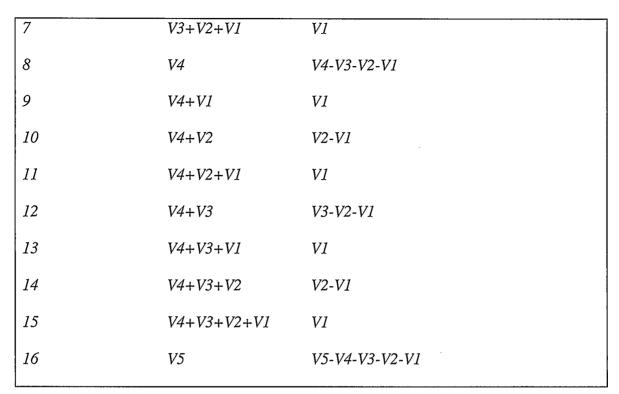

This pattern can be noted more clearly in the list of step voltage values given in Table (3.2). In this table, the values of the staircase output voltage waveform v(t) are listed up to 15 steps, i.e. for m=4, together with the corresponding step values. The step values are the difference between a given voltage level and the previous one. The pattern of the step voltages follows a binary sequence. For more declaration of the final compact form of the equation, the case of four voltage sources is given in the following equation:

$$\begin{split} H(n) &= \frac{4}{n\pi} [V1\{cos(n\theta 1) - cos(n\theta 2) \\ &+ cos(n\theta 3) - cos(n\theta 4) + cos(n\theta 5) - cos(n\theta 6) + cos(n\theta 7) \\ &- cos(n\theta 8) + cos(n\theta 9) \\ &- cos(n\theta 10) + cos(n\theta 11) - cos(n\theta 12) + cos(n\theta 13) - cos(n\theta 14) \\ &+ cos(n\theta 15)\} \\ &+ V2\{cos(n\theta 2) - cos(n\theta 4) \\ &+ cos(n\theta 6) - cos(n\theta 8) \\ &+ cos(n\theta 10) - cos(n\theta 12) + cos(n\theta 14)\} + V3\{cos(n\theta 4) \\ &- cos(n\theta 8) + cos(n\theta 12)\} + V4\{cos(n\theta 8)\}], \quad n = 1,3,5 \dots (3.9) \end{split}$$

Hence, for the general case of m dc voltage sources, the equation for Fourier coefficients H(n) for the first technique can be given in a compact form as follows:

$$H(n) = \frac{4}{n\pi} \sum_{j=1}^{m} V_j \sum_{i=1}^{2^{m-j+1}-1} (-1)^{i+1} \cos\left(n\theta_{2^{j-1}(i)}\right), \qquad n = 1, 3, 5...(3.10)$$

| angle number(i) | voltage level | step value |

|-----------------|---------------|------------|

| 1 .             | VI            | VI .       |

| 2               | V2            | V2-V1      |

| 3               | V2+V1         | VI         |

| 4               | V3            | V3-V2-V1   |

| 5               | V3+V1         | VI         |

| 6               | V3+V2         | V2-V1      |

| 6               | V3+V2         | V2-V1      |

Table (3.2) Pattern of step values in the first technique

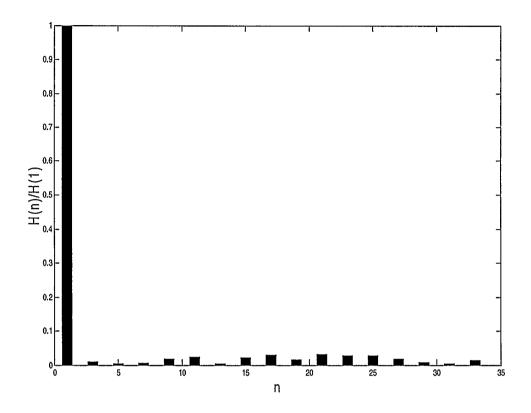

Fig. 3.6 Spectrum of the staircase waveform for two voltage sources generated by the first technique

Equation (3.10) represents the Fourier coefficient values for the staircase waveform generated by the first technique. Verification of this equation is given in Appendix C. Fig. 3.6 gives the spectrum of the output waveform generated using this method. The maximum harmonic magnitude occurs at the 17<sup>th</sup> harmonic and equals to 5.7% of the fundamental. The THD is 12.21%; a reduction of approximately 30% from the case of the conventionally generated waveform. The reduction in THD will be higher in the case of more than two voltage sources.

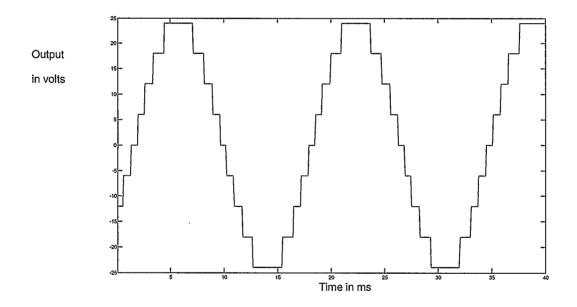

### 3.5 The Technique of Dual Polarity Voltage Addition in Each Half Cycle

In the technique investigated in the previous section, it was possible to reach a number of levels equal to  $(2^{m+1}-I)$ . This higher number of levels was achieved by inserting all the possible combinations of voltage additions in the output waveform with the same polarity of the half wave output waveform. The second technique exploits this idea, with some modification, to obtain a larger number of voltage levels in the inverter output. In this technique, all the possibilities of positive and negative polarity voltage values are used in each half cycle of the output waveform to achieve the maximum number of levels in the inverter output. Going back to the same example of the two voltage level that is equal to V2-VI. The sequence of steps is VI at  $\theta I$ , V2-VI (a new value) at  $\theta 2$ , V2 at  $\theta 3$ , and V2+VI at  $\theta 4$ , and the symmetrical voltages with negative polarity in the negative half cycle. Four switching angles are present in the first quarter of the waveform in this case

with only two dc voltage sources. As stated before, there are more constraints with this technique; the most obvious one is that V2-V1 should not be equal to any of the other three voltage level values. This can be formulated as follows:

V2-V1>V1

Also, for the case of three voltage sources, one should have:

*V3-V2-V1>V2+V1*

In general, for any number of voltage sources, this constraint may be expressed as:

$V_{j}-(V_{1}+V_{2}+...+V_{j}-1)>V_{1}+V_{2}+...+V_{j}-1$  (3.11)

Equations (3.1)-(3.3), in addition to equation (3.11) represent the requirements imposed on the values of the dc voltage sources for the second technique. For equal step voltage values, the special case of  $V_i = 3V_{i-1}$ , for all *i*, can be used; this is to be proved later on in this chapter. The other requirement needed for this approach is related to the nature of these dc sources. All of the voltage sources, except for one with the highest voltage value, must accept current flowing in the opposite direction (i.e. sending power to the source) for some parts of the output waveform cycle. This requirement stems from the nature of the dual polarity voltage addition procedure adopted in this technique. With this technique, the number of levels of the inverter output can be as much as  $3^{m}$ . For a three voltage source, for example, an output waveform of 27 levels can be generated; compared with 7 levels in the conventional case. Harmonic distortion can be reduced greatly with such an increase in the number of levels.

## 3.6 Harmonic Analysis of the Second Technique

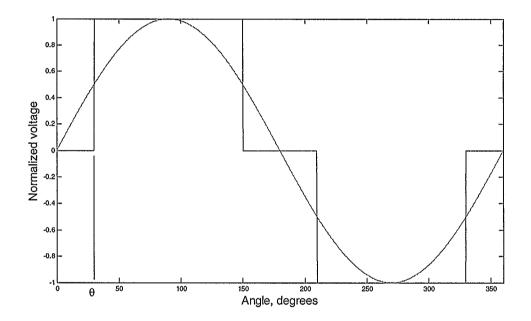

Once again, the case of two voltage sources is first presented, and the general formula for any number of voltage sources can be deduced after that. Fig. 3.7 depicts the output waveform and the switching states of the H-bridge output voltages, choosing V2=3V1. It can bee seen from this figure that the waveform of Va2 is a normal square wave activated at  $\theta 2$ , while Va1 is activated at three of the four angles of the output waveform with positive and negative polarities. Once again, the method used previously to find the Fourier coefficients in the first technique is used here. The cosine term is multiplied by the value of the step voltage in the output waveform, and the argument of the cosine function is *n* multiplied by the angle at which this step takes place. Table (3.3) shows the values of step voltages for this technique for up to four voltage sources, i.e. providing 81 levels in the output voltage waveform. According to this table and the discussion above, the Fourier coefficients of the staircase waveform shown in Fig. 3.7 can be given as:

$$H(n) = \frac{4}{n\pi} [\{V1\} \cos(n\theta 1) + \{V2 - V1 - (V1)\} \cos(n\theta 2) + \{V2 - (V2 - V1)\} \cos(n\theta 3) + \{(V1 + V2) - V2\} \cos(n\theta 4)],$$

$$n = 1, 3, 5 \dots (3.12)$$

In this equation, the expressions that were put between curly braces {.} represent the values of the step voltages at the specified activation angles. Simplifying equation (3.12) allows us to express the harmonic coefficients in the following form:

$$H(n) = \frac{4}{n\pi} [V1 \{ \cos(n\theta 1) - 2\cos(n\theta 2) + \cos(n\theta 3) + \cos(n\theta 4) \} + V2\cos(n\theta 2)],$$

$$n = 1, 3, 5 \dots (3.13)$$

In the case of three voltage sources, there will be angles up to  $\theta$ 13; as can be seen from table 3.3, where the output staircase waveform will have 27 levels. The equation for harmonic coefficients in this case can be written as:

•

$$\begin{split} H(n) &= \frac{4}{n\pi} \left[ V1\{\cos(n\theta 1) + \cos(n\theta 2) + \cos(n\theta 3) + ... + \cos(n\theta 13) - 3\cos(n\theta 2) - 3\cos(n\theta 5) - 3\cos(n\theta 8) - 3\cos(n\theta 11) \right] + V2\{\cos(n\theta 2) + \cos(n\theta 5) + \cos(n\theta 8) + \cos(n\theta 11) \right] \\ &-3\cos(n\theta 5) + V3\cos(n\theta 5) \right], n = 1, 3, 5, ... (3.14) \end{split}$$

In the case of 4 voltage sources, there will be angles up to  $\theta$ 40, the output will have 81 levels, and the equation can be written as:

$$H(n) = \frac{4}{n\pi} [V1\{\cos(n\theta 1) + \cos(n\theta 2) + \cos(n\theta 3) + ... + \cos(n\theta 40) - 3\cos(n\theta 2) - 3\cos(n\theta 5) - 3\cos(n\theta 8) - 3\cos(n\theta 11) - 3\cos(n\theta 14) - 3\cos(n\theta 17) - 3\cos(n\theta 20) - ... - 3\cos(n\theta 38)\} + V2\{\cos(n\theta 2) + \cos(n\theta 5) + \cos(n\theta 8) + \cos(n\theta 11) + \cos(n\theta 14) + \cos(n\theta 17) + ... + \cos(n\theta 38) - 3\cos(n\theta 5) - 3\cos(n\theta 14) - 3\cos(n\theta 23) - 3\cos(n\theta 32)\} + V3\{\cos(n\theta 5) + \cos(n\theta 14) + \cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 23) - 3\cos(n\theta 32)\} + V3\{\cos(n\theta 5) + \cos(n\theta 14) + \cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) + \cos(n\theta 14) + \cos(n\theta 14) + \cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) + \cos(n\theta 14) + \cos(n\theta 14) + \cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) + \cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) - 3\cos(n\theta 14) + \cos(n\theta 14) + \sin(n\theta 14)$$

To proceed further with the derivation of the final compact form of the Fourier coefficients equation for the second technique; it is very helpful to understand the pattern

$+\cos(n\theta_{23}) + \cos(n\theta_{32}) - 3\cos(n\theta_{14}) + V4[\cos(n\theta_{14})], n = 1, 3, 5, (3.15)$

of the step voltage values shown in Table (3.3). From this pattern it is seen that the step values follow a ternary repetition mode. Also, it can be noted that the term multiplied by (-2) in equation (3.13) is repeated several times in equations (3.14) and (3.15). For the sake of simplicity of formulation, this term is put in the form of (1-3), i.e. instead of writing for example [-2Vcos(n $\theta$ )], it is written as [Vcos(n $\theta$ )-3Vcos(n $\theta$ )]. Following these rules, the equation of the Fourier coefficients for the second technique can be compactly expressed by the following form:

Fig. 3.7 Output voltage waveform and switching pattern for the second technique

$$H(n) = \frac{4}{n\pi} \{ \sum_{j=1}^{m-1} V_j \left[ \sum_{i=0}^{\frac{3^{m+1-j}-3}{2}} \cos\left(n\theta_{3^{j-1}i+\frac{1}{2}(3^{j-1}+1)}\right) - 3 \sum_{k=0}^{\frac{3^{m-j}-3}{2}} \cos\left(n\theta_{3^{j}k+\frac{3^{j}+1}{2}}\right) \right] + V_m \cos(n\theta_{\frac{3^{m-1}+1}{2}}), \qquad n = 1, 3, 5 \dots (3.16)$$

| Table (3.3) Pattern of Step | Voltage | Values in the Second Technique |

|-----------------------------|---------|--------------------------------|

|-----------------------------|---------|--------------------------------|

| angle number(i) | voltage level | step value     |

|-----------------|---------------|----------------|

| 1               | V1            | V1             |

| 2               | V2-V1         | V2-2V1         |

| 3               | V2            | V1             |

| 4               | V2+V1         | V1             |

| 5               | V3-V2-V1      | V3-2V2-2V1     |

| 6               | V3-V2         | V1             |

| 7               | V3-V2+V1      | V1             |

| 8               | V3-V1         | V2-2V1         |

| 9               | V3            | V1             |

| 10              | V3+V1         | V1             |

| 11              | V3+V2-V1      | V2-2V1         |

| 12              | V3+V2         | V1             |

| 13              | V3+V2+V1      | <b>V</b> 1     |

| 14              | V4-V3-V2-V1   | V4-2V3-2V2-2V1 |

| 15              | V4-V3-V2      | V1             |

| 16              | V4-V3-V2+V1   | V1             |

| 17 | V4-V3-V1    | V2-2V1     |

|----|-------------|------------|

| 18 | V4-V3       | V1         |

| 19 | V4-V3+V1    | V1         |

| 20 | V4-V3+V2-V1 | V2-2V1     |

| 21 | V4-V3+V2    | V1         |

| 22 | V4-V3+V2+V1 | V1         |

| 23 | V4-V2-V1 .  | V3-2V2-2V1 |

| 24 | V4-V2       | V1         |

| 25 | V4-V2+V1    | V1         |

| 26 | V4-V1       | V2-2V1     |

| 27 | V4          | V1         |

| 28 | V4+V1       | V1 .       |

| 29 | V4+V2-V1    | V2-2V1     |

| 30 | V4+V2       | V1         |

| 31 | V4+V2+V1    | V1         |

| 32 | V4+V3-V2-V1 | V3-2V2-2V1 |

| 33 | V4+V3-V2    | V1         |

| 34 | V4+V3-V2+V1 | V1         |

| 35 | V4+V3-V1    | V2-2V1     |

| 36 | V4+V3       | V1         |

| 37 | V4+V3+V1    | V1         |

| 38 | V4+V3+V2-V1 | V2-2V1     |

| 39 | V4+V3+V2       | V1                   |  |

|----|----------------|----------------------|--|

| 40 | V4+V3+V2+V1    | V1                   |  |

| 41 | V5-V4-V3-V2-V1 | V5-2V4-2V3-2V2-2V1 . |  |

| 41 | V5-V4-V3-V2-V1 | V5-2V4-2V3-2V2-2V1 . |  |