#### THE UNIVERSITY OF CALGARY

A Clausal Approach to Digital Logic Circuit Design

by

Ronan O'Byrne

#### A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

#### DEPARTMENT OF COMPUTER SCIENCE

CALGARY, ALBERTA JUNE, 1987

© Ronan O'Byrne, 1987

# The University of Calgary Faculty of Graduate Studies

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled, "A Clausal Approach to Circuit Design" submitted by Ronan O'Byrne in partial fulfillment of the requirements for the degree of Master of Science.

John Kendall, Computer Science

G. Birtwistle, Computer Science

G.S. Hope, Electrical Engineering

1987-06-01

#### Abstract

• • • • •

.....

This thesis explores the use of logic programming as a technique to aid in the design of complex logic systems. The design of digital systems requires many purely clerical tasks which must be performed accurately and within the confines of many interacting rules. The design result which is sought is usually the result of a search over a solution space rather than a unique, procedurally generated answer. In the development of newer CAD tools the emphasis is on automatic logic generation from functional specifications and an ability to deal effectively with design complexity. Logic programming is proposed as a useful technique necessary to develop these flexible yet automatic design tools. Some research findings are presented, and a simple logic synthesis and design system based on Prolog is illustrated.

iii

#### Acknowledgement

I thank my advisor John Kendall for sparking my interest in logic circuit design and for supplying direction and advice, even while giving me free rein to explore on my own. He has been a pleasure to work with, generous with time and research support, and a most constructive critic and remaining flaws are, of course, entirely of my own devising.

I thank the faculty and students of the Department of Computer Science, and other members of the JADE project for their support and interest. I thank the Natural Sciences and Engineering Research Council of Canada (NSERC). Most of all I thank my wife Ann, for her patience, understanding and encouragement.

# **Table of Contents**

.

| 1. | . Logical Design of Digital Systems                     | 1  |

|----|---------------------------------------------------------|----|

|    | 1.1 The Design Process                                  | 1  |

|    | 1.2 The Challenge to CAD                                | 5  |

|    | 1.3 Logic Design & Computer Aided Engineering           | 8  |

|    | 1.3.1 DA4 - International Computers Ltd.                | 9  |

|    | 1.3.2 IEDS - Intergraph Corporation                     | 12 |

|    | 1.4 VLSI Design                                         | 14 |

|    | 1.4.1 Design Styles for VLSI                            | 16 |

|    | 1.4.2 TANCELL - Tangent Systems Corp                    | 18 |

|    | 1.4.3 Electric                                          | 19 |

| 2. | Synthesis of Combinational Logic                        | 20 |

|    | 2.1 What is Logic Synthesis                             | 20 |

|    | 2.2 Why Logic Synthesis                                 | 22 |

|    | 2.3 Automatic Logic Synthesis & Optimization            | 24 |

|    | 2.3.1 ALERT                                             | 24 |

|    | 2.3.2 LSS (Logic Synthesis System)                      | 25 |

|    | 2.3.3 DDL/SX (Digital Design Language/Synthesis eXpert) | 29 |

|    | 2.3.4 MACDAS Circuit Design System                      | 31 |

|    | 2.3.5 Socrates                                          | 32 |

1

ł

.

.

|    | 2.3.6 Logic Design using Tokio & C-Prolog               | 35 |

|----|---------------------------------------------------------|----|

|    | 2.3.7 DAA (Design Automation Assistant)                 | 38 |

| 3  | . Logic Programming                                     | 39 |

|    | 3.1 Logic Programming                                   | 39 |

|    | 3.1.1 Prolog Logic Programming                          | 40 |

|    | 3.2 Prolog as an Expert System Shell                    | 43 |

|    | 3.3 The Case for a Clausal based Expert System Approach | 45 |

| 4  | . Circuit Representation in Prolog                      | 48 |

|    | 4.1 Circuit Representation in Prolog                    | 48 |

|    | 4.2 Prolog Horn Clause Circuit Representation           | 48 |

|    | 4.3 Prolog Structure Circuit Representation             | 52 |

|    | 4.3.1 Pre-defined Circuits                              | 54 |

|    | 4.3.2 Circuit Input Signals                             | 55 |

|    | 4.3.3 Handling Errors                                   | 56 |

| 5. | . Logic Minimization & Conversion                       | 57 |

|    | 5.1 Boolean Logic                                       | 57 |

|    | 5.2 Logic Minimization                                  | 59 |

|    | 5.2.1 Absolute Logic Minimization                       | 60 |

|    | 5.2.2 Heuristic Logic Minimization Techniques           | 61 |

|    | 5.2.3 Prolog Logic Rewrite Rules                        | 62 |

|    | 5.2.4 Meta-level inferencing                            | 63 |

. . . .

;

•

ţ

# vi

| 5.2.4.1 Logic Minimization Example 1              | . 65 |

|---------------------------------------------------|------|

| 5.2.5 Rewrite rules and true minimzation          | 65   |

| 5.3 Logic Circuit Conversion                      | 66   |

| 5.3.1 NAND/NOR Conversion                         | 67   |

| 6. Counting Circuits                              | 70   |

| 6.1 Counting Circuits                             | 70   |

| 6.2 Designing Counter Circuits                    | 72   |

| 7. Prolog Counter Design                          | 78   |

| 7.1 User Interface                                | 78   |

| 7.2 Limitations of a Prolog Interface             | 80   |

| 7.3 Selecting a Counter Type                      | 81   |

| 7.4 Circuit Synthesis                             | 85   |

| 7.4.1 Example 1 - Synchronous Ring Counter        | 85   |

| 7.4.2 Example 2 - Synchronous Count-by 23 Counter | 87   |

| 7.5 Logic Minimization                            | 91   |

| 7.6 NAND Logic Adoptation                         | 93   |

| 7.7 Functional Simulation                         | 93   |

| 7.7.1 Functional Simulation Example               | 94   |

| 7.8 PCD Session                                   | 96   |

| 8. Summary and Conclusions                        | 102  |

| 8.1 Summary                                       | 102  |

:

.

| 8.2 Conclusions                      | 103 |

|--------------------------------------|-----|

| 8.3 Future Research                  | 104 |

| Bibliography                         | 106 |

| Index                                | 116 |

| Reference Index                      | 118 |

| Appendix A - PCD Listing             | 119 |

| Appendix B - Prolog Simulation Trace | 144 |

. . . . . . .

# List of Tables

| 2-1 Logic Synthesis Systems                        | 24 |

|----------------------------------------------------|----|

| 4-1 Known Circuits                                 | 54 |

| 5-1 Rewrite Rules                                  | 64 |

| 5-2 Conversion Rules for NAND logic representation | 69 |

| 6-1 Counter Code Sequences                         | 72 |

| 6-1 Flow table                                     | 75 |

| 7-1 PCD Commands                                   | 82 |

.

# List of Figures

.

| 1-1 The Design Process              | 4  |

|-------------------------------------|----|

| 1-2 DA4 System Diagram              | 11 |

| 2-1 Levels of Description in LSS    | 26 |

| 2-2 Socrates System Diagram         | 33 |

| 4-1 Example circuit                 | 52 |

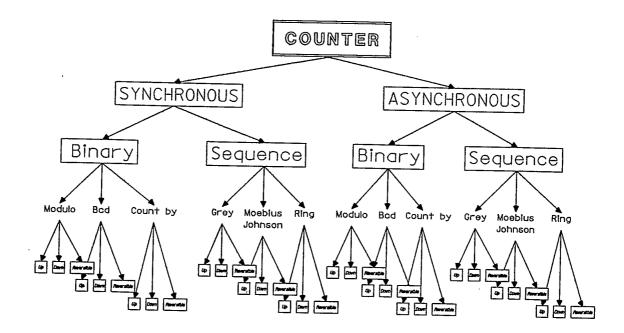

| 6-1 Counter Tree Structure          | 71 |

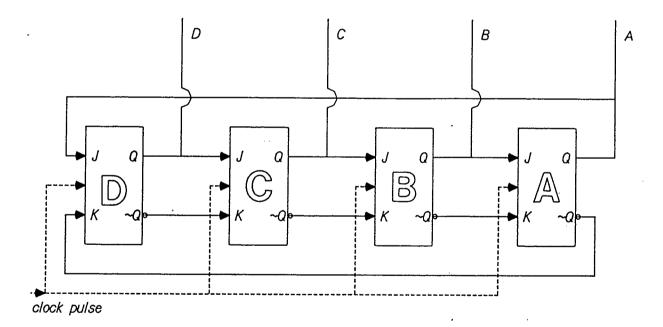

| 6-2 Synchronous Ring Counter        | 73 |

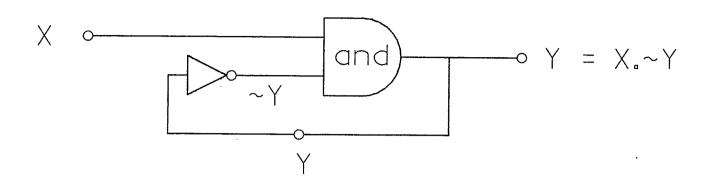

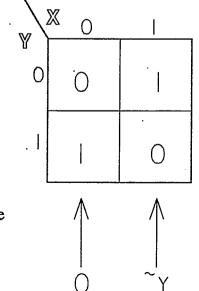

| 6-3 Instability in a simple network | 75 |

#### **CHAPTER 1**

#### Logical Design of Digital Systems

This chapter presents an overview of the evolution and use of CAD for logic design. It is an overview of a field which involves the works of many manufacturers, universities, and research foundations, and as such, the example systems are selected as representative of a particular type. Since this thesis is concerned with improved design automation techniques, this chapter answers the important question, "Why is there a need for better design automation?"

Increasing design complexity of integrated systems is forcing a modification in the traditional approach to design. To illustrate current approaches to the problem of logic design several logic design and production systems are introduced. These systems are discussed with respect to their flexibility to adapt to changing fabrication technology, and their ability to adapt to increasing complexity.

#### **1.1 The Design Process**

Historically, the design task was carried out completely manually. One of the first design automation systems was presented at the 1956 Western Joint Computer Conference by Cray & Kisch [Cray 56]. They described a system which provided automatic checking of logic equations for logical, clerical, and timing errors, logic simulation and net-listing abilities. One interesting observation which also might indicate the pioneering nature of this article is that it cited no references. Several systems flourished in the sixties, with many computer manufacturers developing their own systems ([Kaskey 61],[Rosenthal 61], [Button 60], and others). Design automation was spurred on by tighter design constraints and complexity. These systems were generally not shared

among manufacturers, because they reflected each manufacturer's own design philosophy, circuit technology and design computer.

Meanwhile in an attempt to reduce the number of engineering changes caused by errors in design, logic simulation was introduced. The reasoning applied was that if the logic design was completely simulated, then automatic wiring machines, which used these "proven" designs, could produce an accurate reliable product. As system complexity increased, engineers quickly found out that they could not contain the entire design that they wanted to simulate on a small computer. Simulation had run into trouble. Simulation could not give full coverage. This problem was partially solved by the introduction of hierarchical design and the use of standardized components. Many current design systems are based on these principles. Now simulation could occur above the detailed level, and consequently could be more rigorous.

Hierarchical design became the first technique to deal with design complexity. In hierarchical design, initial design occures at the highest level of abstraction and proceeds to lower detailed levels of design. As each level of the design is completed, it becomes a specification for the lower levels of the design. With hierarchical design techniques, optimization is hard to achieve because designs have downwardly imposing *design* constraints and upwardly imposing *physical* constraints. Failure in one or more levels of the design results in a redesign of that level and possibly of other levels in the design.

The physical constraints of design have become more complex as technology has evolved. In a first generation computer, one could point to a relay that performed some primitive Boolean operation, and hold it in one's hand. Fabrication technology has advanced to where it is now impossible, without the aid of a microscope, to find the spot in an integrated circuit where that function is now performed. While the manufacturing design elements of the components in a microcomputer are considerably reduced compared to a first generation computer, the increase in the number of logic design elements, and increased the logic design task. Clock speeds are now much faster and so timing simulation is more important. Physical layout on silicon requires technology specific logic design.

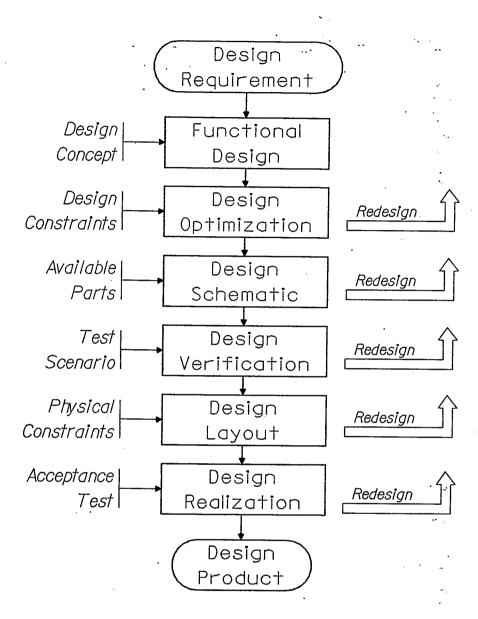

The *Design Process* is the sequence of tasks required to create a design subject to constraints. In the design of digital systems, the design process takes a set of conceptual ideas which describe a proposed digital system, and transforms it into a set of detailed design data, such as part numbers, logic schematics etc., which provide suitable information required for manufacture. The conceptual design process is illustrated in Figure 1-1.

The functional design is the initial process of deriving a potential and realizable solution to the input design requirements. This is sometimes referred to as architectural analysis and design, and includes such activities as hardware/software tradeoffs and speed/power tradeoffs. With a firm functional design, analysis is then performed to determine the best way to implement the design, subject to the design constraints (technology, size, power, and cost). A schematic can then be drawn to show the proposed interconnections of available parts.

This proposed implementation is analyzed for proper functioning by applying a test sequence that emulates a subset of the conditions to be expected in real use. Once a designer is confident that the design will meet functional requirements, the physical lay-

#### FIGURE 1-1 The Design Process

out of the actual interconnection of devices is formulated. Finally the design is realized, tested and ready for release as a product.

The design workflow is the sequence of tasks required to accomplish the design process. It is sequential only in an ideal conceptual case. It is conceivable that during

1.1

physical layout, flaws in the functional or schematic design may be uncovered, which would cause redesign at the conceptual level. During product acceptance tests, flaws in the functional design may be uncovered, making a major redesign necessary. The key to efficient design is to strive for a **sequential design workflow**, keeping any backtracking and recycling to one or two stages in the design flow. The purpose of Computer-Aided Design (CAD) is to assist the designer through each stage of the design workflow.

#### **1.2 The Challenge to CAD**

The expansion in the electronics field has occurred as a result of amazing progress over the past few years in the semiconductor fabrication technology. Gate densities and chip sizes both increased to make it possible to design larger, and more complex systems. This rapid change in the complexity of what could be made, changed the focus from "How to *make* it ? " to "How to *design* it ?" The challenge to CAD is to provide design automation which offers the opposing characteristics of flexibility and automation.

Provided with incredible potential for system integration, the electronic industry has been both innovative and reactionary in their response to the logic and system design problem. Innovative in their adoption of new fabrication technology, but reactive in advances in the use of CAD for design. The net result is the generally accepted belief that design is the major bottleneck to even greater system integration. This bottleneck occurs for a variety of reasons. Design systems are technology specific and have problems adapting to changes in the fabrication technology. But, the most important, and yet subtle problem which plagues design systems is their evolutionary nature. Most design automation systems are based on a level of Man Computer interaction which was

1.2

appropriate a few years ago.

Most designers readily admit that their designs do not occur in a rigorous scientific manner. They start a new design with only a sketchy knowledge of how the final design might turn out. This allows them to keep their options open until later in the design cycle. At the early stages, they are exploring possibilities of design. These specifications are solidified as design options are explored at various levels of the design hierarchy. When they look back at the process involved in creating a new design, they often believe that they stumbled upon the design rather than it being the result of a coherent design process. While it may be feasible for designs to occur in such a haphazard manner today, in future more complex designs will lay pressure for a more coherent approach. Inadequacies of current Computer-Aided Design (CAD), caused by a philosophy which considers CAD to *facilitate* design, makes design more of an art than a science, and places greater reliance upon the designer to direct the design process.

While most designers agree that CAD is the interaction of the designer with the computer to aid design decision making, they do not always agree as to what level of interaction is the most appropriate. Several implementation styles for CAD have evolved as a result, and are identified [McKinsey 84]. These design approaches are the result of the perceived role of CAD by corporate senior management. The roles can be classified as follows;

#### **Electronic Pencil**

An elementary role as an *Electronic Pencil* is suitable for very small designs, and for manual design workflow procedures. With this approach the CAD system provides only

the means for a designer to develop a new design. Yet, it is surprising how many design companies use CAD in this fashion.

#### **Interactive Design**

An *interactive* design system automates some common tedious step in the design process, but requires the designer to design the system. This is the approach adopted by design groups faced with a wide variety of design tasks, where a fully automated design system does not have the flexibility to address these design realms.

#### **Automated Design Synthesis**

An *automated design system* designs the system based on specifications entered by the designer. The CAD system is characterized by its complete involvement and active participation in the design process. Although this approach is new, it has been applied successfully in specialized design areas. ([Darringer 80], [Fox 84], [Fujita 86] etc.)

#### **1.3 Logic Design & Computer Aided Engineering**

The commercial CAE (*Computer Aided Electronics*) marketplace is rapidly expanding in North America at an annual rate of approximately 35 % and, now represents approximately \$200 billion for both hardware and software. Despite these impressive figures the commercial use of design automation is in its infancy. Reviewing current CAD techniques, [Wayne 85] comments that it is the designers'reluctance to advance from low level design techniques which has restrained the advance of automation in commercial design environments. Design automation tools offer the logic designer greater productivity and reduced errors, but they require commitment to implement. It is this requirement to change methodologies, the comfort level in current low level design techniques, and the inflexibility of high level design techniques, which are responsible for the slow transition in the design community to higher level design techniques.

Vendors in the CAE/CAD marketplace have been classified [Bogert 87] according to the design systems offered. These classifications are;

#### (1) High-end Electronic Generalist

These companies attempt to provide an integrated set of design and management methodologies that address diverse types of design. These companies stress comprehensive management techniques, integrated hardware, and file and database computing. Although the design software of the electronic generalist is not as sophisticated as the semiconductor specialists', their ability to integrate and transfer information is superior.

#### (2) Low-end Electronic Generalist

These companies have built their electronic design automation products around the personal computer. The report's authors [Bogert 87] commented that these systems offer good design and management capabilities for their unusually low prices, but do not have the functionality of high-end systems. These systems are most suited to the "single-user" environment, but this is likely to change as low cost networking "engineer workstations" become available.

#### (3) Integrated Circuit Specialist

Included in this group are silicon compiler companies, and other sophisticated design techniques for VLSI, (*Very Large Scale Integration*). The "IC Specialist" is considered to offer "leading edge" IC design tools, but users are warned to make sure that implementations of these circuit designs are straightforward.

#### (4) Semiconductor & Engineering Tools

These specialists offer design tools as an adjunct to their semiconductor manufacturing businesses. These tools are usually finely tuned to their own semicustom products and processes, and have design centers where customers can use CAE tools to design circuits.

The following sub sections review example design systems from these defined categories.

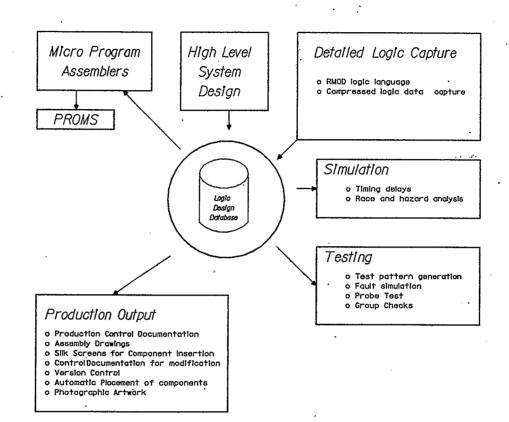

#### 1.3.1 DA4 - International Computers Ltd.

DA4 [Adshead 81] is the design automation system used by International Computers Limited in the United Kingdom. Following earlier experiments with design automation systems it was introduced in its basic form in 1974 as DA1. It is now a very comprehensive system, supporting designs in nearly 20 different classes of interconnection technology. Thus DA4 is typical of an *integrated* CAD system, which It represents over 400 man years of internal development. The goals of DA4 were;

(1) To provide a common design system for the whole company.

- (2) To provide the basis for LSI (Large Scale Integration) design.

- (3) To support hierarchical logical and physical design.

A system diagram is shown in Figure 1-2. High level system design uses a language to represent a computer at the architectural level in terms of structure and behaviour. The design can be expanded in a "top down" fashion. Logic input is represented in the RMOD [Wager 81] language, which describes the circuit at the register level. Logic designs can be keyed directly into alphanumeric terminals or entered graphically at the design stations. RMOD achieves compression of input data by expressing a circuit at the "register level", rather than at the conventional "circuit-element level."

*Multi-strings* are used to represent parallel data-paths, and are given structured signal names. *Multi-symbols* represent logic functions that are available as a functional block.

DA4 provides logic simulation for complex logic elements reporting on worst case delays, timing race etc. DA4 can also be used for automatic circuit testing. DA4 facilitates many production outputs such as schematics and photographic artwork.

DA4 is typical of an in-house CAD system. These systems have evolved from a simple design automation tool to a complex workflow solution system which have been adapted to the evolving design automation needs of the company. With source code available within the company, future evolution of the design system can be controlled to conform to design practices and technologies. The result of this development guidance is a system which performs well in its intended environment, but fails to be adaptable in many other environments. This lack of flexibility means that DA4 is probably of no use

DA4 - International Computers Ltd.

to any other company.

#### **1.3.2 IEDS - Intergraph Corporation**

IEDS (*Interactive Electronic Design System*) which runs on an Intergraph augmented DEC VAX and proprietary dual screen graphic workstations, is a typical graphical turnkey electronic design system for MSI and LSI circuit design. This system can be classified under "High end Electronic Generalist" The approach to the design is *interactive* where the designer can see instantly a graphical representation of the work he has performed. The design is stored in graphical and linked attribute databases. To speed the development of the schematic drawing, the designer can develop circuit cells and place these in the drawing with one operation. The schematic can be defined hierarchically, so that the design is partitioned into smaller functional blocks. Once the schematic of the circuit has been developed, the following automatic functions are available from IEDS.

#### (1) Automatic Net-list generation

This is based upon schematic connectivity.

#### (2) Automatic component packaging for MSI

IEDS packages gates into standard MSI logic ICs, and also assigns pin numbers.

#### (3) Best initial PC Component Placement

When placing components on a printed circuit board, IEDS will show the outline of the component and "rubber banded" interconnects to other components already placed on the board. :

#### (4) Automatic Trace Routing

IEDS is provided with a multi-layer circuit board router.

### (5) Manufacturing Interfaces

Interfaces to manufacturing equipment such as drilling machines and photo masks are available.

Intergraph's IEDS electronic design software is typical of many turnkey CAD vendors such as Computervision, Calma or Applicon. Although most digital design groups use commercially available CAD systems, such as IEDS from Intergraph, they must put up with the lack of source code to make minor modifications and the lack of control in product evolution. These two drawbacks have not discouraged the use of commercial systems.

, . .

#### 1.4 VLSI Design

VLSI (Very Large Scale Integrated) increases the size and complexity of logic design, and thus poses the following special design problems.

#### [a] Verified Designs

A traditional design approach which uses repeated low level iterations through tasks such as layout, detailed simulation, timing analysis, fault simulation, automatic test generation is prohibitively expensive for VLSI due to the complexity of the circuit. Circuits are more complex, where changes can have knock on effects which are difficult for the designer to comprehend and control. Design techniques must evolve to the stage where design is sequential to the greatest extent. This requires that testing and evaluation be performed as the design evolves and the use of design techniques which produce *verified* designs.

#### [b] **Design Input**

VLSI circuit design creates new problems for design input. Graphical input for logic design and layout is the traditional approach. It is based on using CAD as an "electronic pencil" allowing the designer to develop his design. For VLSI this becomes a combersome technique which limits the potential to improve the efficiency of the design. As the design is entered, it cannot be fully validated until completion and as a result, errors are not discovered until late in the design process.

#### [c] Design Representation.

Traditional design representation is in the form of a schematic which shows functional blocks, devices and the inter-relationships. These schematics describe only the physical domain. There are two other domains of interest which, when combined with the physical domain, characterize any VLSI design. These are the structural and behavioural domains. These domains may be defined as follows. The *physical* domain is concerned with the specification of the physical layout of the integrated circuit via patterns on fabrication masks. The *structural* domain is concerned with describing the electrical characteristics of the design in terms of electrical components and their interconnections. The *behavioural* domain describes a design in terms of its function.

Any design language must interface directly with the design verification system, both at the structural and behavioural level. The necessity for having both structural and behavioural design verification is that, initially, it is likely that simple behavioural characteristics would be all that would be available. Hence design verification can begin at this level. As the design matures, structural design can be specified, and to some extent, automatically generated from the behavioural specification. The design verification process can then continue, until the behavioural and structural descriptions are verified to whatever degree of accuracy deemed necessary. This process can involve the elimination of numerous design errors and description errors. Furthermore, it can aid in the addition of testing hardware in the design to test those areas of logic that were found to be insufficiently tested by the design verification process.

#### [d] Hierarchical Design.

In a structured VLSI design environment there exists one hierarchy of description for all three domains. The VLSI design system should address functional and

physical problems at each level. SHIFT [Liblong 84] is an example of a hierarchic design language whose purpose is to capture the various descriptions of a circuit in a consistent manner.

#### **1.4.1 Design Styles for VLSI**

Integrated electronics has developed in a heatedly competitive and often secretive business environment. As a result there has been a proliferation of different device technologies, circuit design families, logic design techniques, mask making techniques, and wafer fabrication techniques, etc. Another obstacle is the high rate of change in the electronics industry, which is driven by improvements in fabrication technology.

Design constraints have caused the evolution of several *design styles*. These design styles have evolved to meet the requirements of particular design scenario.

The fully custom design method is an *ad hoc* implementation. To date, CAD techniques support custom design only to a limited extent, and as a consequence, custom design is profitable only for large production of complex systems, such as microprocessors or memories, or for circuits where special performance is required. Many industry analysts believe that fully custom IC design will be a growth market in the 1990's, and will be performed by designers whose current approach is MSI logic.

In gate-array design, a circuit is implemented in silicon by personalizing a master array of uncommitted gates using a set of interconnections. The design is constrained by the fixed structure of the master array, and is limited to routing the interconnections. CAD for gate-array design allows complex circuits to be implemented in a short time. Gate-arrays are widely used, in particular for small volume production or for prototyping new designs.

The design of a VLSI circuit in a standard-cell (or poly-cell) design method requires partitioning the circuit into atomic units that are implemented by precommitted cells. Placement and routing of the cells is supported by computer-aided design tools. The standard-cell and gate-array design methods alone do not support highly optimized designs. Standard cell designs are more flexible than gate-array designs, but require longer development time. An approach which combines the speed of gate-arrays and the flexibility of standard-cells has been developed [Brown 74] called *CMOS Cell Arrays*. The CMOS Cell Array uses transistor isolation within pre-characterized standard cells to allow the cell row locations to be defined. This allows all wafers to be pre-processed with all necessary diffusions - final transistor size and placement are part of the customization and add to the flexibility. This technique is so similar to standard cell, that the same CAD software can be used. Even the CCA library has the function and performance as a SC library. Transistor isolation is the feature that allows pre-processing of the CCA wafer.

Designing using algorithmically generated macro-cells, bridges the gap between custom and standard cell design and is compatible with both methods. Macro-cells can implement functional units that are specified by design parameters and by their functionality. Macro-cells are usually highly regular and structured allowing computer programs, called module generators, to produce the layout of a macro-cell from its functional description. The macro-cell approach is attractive because its flexibility allows the designer to exploit the advantages of both custom and standard cell methods. Highly optimized and area-efficient modules can be designed in a short time. In particular *Programmable Logic Arrays (PLA)* macros have been shown to be efficient for designing both combinatorial and sequential functions.

#### 1.4.2 TANCELL - Tangent Systems Corp.

TANCELL is a Cell-based IC design system, developed by Tangent Systems Corp. TANCELL offers *timing driven* layout [Teig 86]. Timing-driven layout of semicustom ICs incorporates circuit timing requirements as basic criteria for layout optimization. The timing-driven layout process consists of circuit timing analysis, automatic layout using timing analysis results, and report generation documenting circuit performance. Properly applied, timing-driven layout can produce, in a single pass ICs that satisfy difficult timing specifications. Performed repeatedly during the layout process, timing analysis uses the latest layout information to calculate the propagation delay for every circuit path in the design. The timing analysis also measures the timing margin or criticality, which is used to drive the automatic layout tools. Each automatic layout tool uses this *criticality* in making placement and routing decisions. The frequent feedback from the analysis of how the layout is progressing, keeps the designer in control over the performance of the design.

This cell-based approach to IC design migrates timing analysis earlier in the design to reduce circuit design changes.

#### CHAPTER 2

#### Synthesis of Combinational Logic

This chapter presents Logic Synthesis and a number of systems which use that approach to design. It is a relatively new design technique which will extend the current role of CAD in logic design. The technique is characterised, its strengths and weaknesses highlighted, and various research systems are discussed... Later chapter 7 will show how logic programming can be used to implement a logic synthesis system.

#### 2.1 What is Logic Synthesis

Logic Synthesis is a technique which generates a logic implementation in the desired technology from a designers functional specifications.

Logic synthesis programs are designed to improve engineering productivity by designing combinational circuits automatically. The effectiveness of such programs depend on their ease of use and the quality of the circuits they produce in the light of constraints applied to the design. Circuits are constrained by the types and characteristics of components available, and by area, delay and power, and testing requirements. Synthesis programs should therefore be capable of generating circuits with competitive area, speed, power and testibility characteristics. Different constraints are not always compatible, ie. the smallest implementation is not always the fastest. So, an automatic synthesis program should also be able to make tradeoffs between competing constraint goals. The logic synthesis problem is defined as follows:

- Given a circuit family of components, including all constraints and circuit limitations associated with each circuit element type.

- (2) Given a logical description of a digital system in some language, such as the language of register transfers, Boolean equations or functions, or even gate equations.

- (3) Realize the system described in item (2) using components given in item (1) and in addition minimize the total implementation cost. This cost consists of both the circuit costs and the per-unit design costs. Usually these two costs are inversely proportional to each other.

The logic synthesis problem is analogous to the problem of machine-language translation. Logic synthesis implements a given digital system in terms of elements from a given circuit family. The compilation of a Fortran program, which consists of a set of high level language statements, results in a set of object level code which the computer understands.

The goal of generating an acceptable, technology-specific hardware implementation from a functional specification is not new. Three strategies have been developed.

One approach concentrated on translating Boolean functions into minimum twolevel networks of Boolean primitives ([Breuer 72],[Dietmeyer 78]) and were later extended to limited circuit fan-in and alternative cost functions. Unfortunately, since these systems had algorithms which searched for true circuit minimums, they require time exponential in the number of circuits and cannot be used on most actual designs. A second approach viewed the problem as one of assembling large macros. In these design systems, the data flow of the machine was generated in terms of predesigned or generated macros, such as multiplexors and ALUs. The control logic was usually implemented by PLAs, Weinberger arrays, or ROMs with microcode. Most of the current silicon compiler work falls into this category ([Johannsen 79],[Southard 83]).

Other research attempted to raise the level of specification. The DDL at Wisconsin [Duley 68], APDL at Carnegie-Mellon University [Darringer 69], and ALERT at IBM [Friedman 70], all began with behavioral specifications and produced technologyindependent implementations at the level of Boolean equations. Designs produced were less efficient than a manually produced design, and they did not take advantage of the target technology. These systems pointed out the need for an appropriate level of efficiency and control for the designer over the circuit.

#### 2.2 Why Logic Synthesis

Logic synthesis and optimization has recently gained significant credibility and practical use. Earlier systems only optimized cell counts, while current systems attempt to synthesis and optimize digital systems based on many technology criteria. With timing constraints, testability, wirability, and efficient use of available primitives in addition to cell counts, the system is able to produce quality designs which do not need further re-design. Such systems are favoured because of their ability to produce efficient technology specific logic.

Hand crafted logic designs are normally checked by modeling and simulation. But,

simulation alone is an inadequate check. The growing complexity of circuits, together with the increasing number of parameters, do not allow thorough simulation with a complete set of test patterns. Circuits which have been subjected to some incomplete functional testing are not guaranteed to be safe and reliable in operation. More thorough testing increases design costs, and introduces additional cost if flaws in the design are found.

A system which produces a *verified* design avoids costs associated with design iteration. The major difference to conventional design, is the requirement to completely determine behavior and interface description *before* starting any concrete design steps. Designers often decline to take this step because a very early detailed definition is not possible real circumstances. The alternative is for design to proceed unguided, where parts are added as necessary. The introduction of a formal task specification primarily shifts activities from a late stage in design to an early one, with subsequent time savings brought about through a reduction in design process cycling. A designer who adopts this approach has to change his interests at the early stage of design ; he must try to validate synthesis procedures used to produce a design rather than rely on simulation to later verify that his design will work.

This approach presents a number of challenges which are problems with current systems.

#### (1) Modifiable & Extendible

Synthesis algorithms should be easy to understand, and should be modifiable by the designer. This is a common problem with design automation tools and the most common reason why design automation is not so widespread. With pro-

cedural languages like Fortran, or C, this requirement is very difficult to satisfy.

#### (2) Sub-optimal Results

The design system should be able to develop suboptimal results where optimal results are not practical. This is important when designs are complex and sub-optimal results are of more value.

(3) **Portability**

The CAD system should be portable to different hardware.

#### 2.3 Automatic Logic Synthesis & Optimization

A number of logic synthesis systems have been developed, and are listed in Table

2-1. Several of these systems are described in detail.

| SYSTEM   | DESCRIPTION                         | INSTITUTION                |

|----------|-------------------------------------|----------------------------|

| ALERT    | Logic design generator              | IBM Watson Research Center |

| DAA      | Knowledge based synthesis           | Carnegie-Mellon University |

| DDL/SX   | Rule based logic synthesis          | Fujitsu Laboratories Ltd   |

| DFT      | Synthesis with testability          | Syracuse University        |

| EL/SYN   | Expert analog circuit synthesis     | MIT                        |

| LSS      | Logic synthesis system              | IBM Watson Research Center |

| MACDAS   | AND/OR circuit synthesis            | Osaka University           |

| MACPITTS | VLSI synthesis                      | MIT                        |

| Socrates | Synthesis & Optimization            | University of Colorado     |

| Tokio    | Automatic CMOS gate array synthesis | University of Tokyo        |

Table 2-1 Logic Synthesis Systems

#### 2.3.1 ALERT

The ALERT system [Friedman 69] converts preliminary high-level descriptions of computers into logic. ALERT is unique in its use of Iverson notation [Falkoff 64] to

describe the architecture of the computer. This input is processed by eight routines in series. First the "translator" checks the input and translates it into a less compact internal representation. Then the "selection decoding" routine scans for variable subscripts and if found replaces it with an appropriate block of logic. The "macro generator" replaces higher order logic elements with the complete combinational logic required to accomplish that operation, and the "sequence analyzer" determines the sequence and control requirements. The "consolidation" process eliminates duplicate logic blocks, and inefficiently connected arrays of elements.

#### 2.3.2 LSS (Logic Synthesis System)

#### Introduction

LSS (*Logic Synthesis System*) ([Darringer 84],[Joyner 86]) is an experimental logic synthesis production system used to produce bipolar gate array chips. It has slowly developed from initial logic synthesis experiments at IBM's Poughkeepsie laboratory in New York. The development team background of automatic theorem proving (D Brand,W Joyner), program verification (J Darringer) and logic design tools (J Gerbi) is reflected in the approach used in LSS. What follows is a brief description of LSS.

#### Design Approach

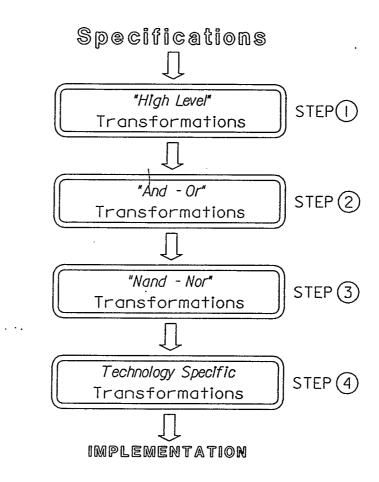

In LSS, logic is transformed from the high-level specification into productionquality implementation through a sequence of local transformations. The system takes (as one of several input forms) a description language at the register transfer level, and attempts to transform it into an interconnection of gates specific to a target technology.

2.3.1

LSS uses levels of description, to which local transformations are applied. These local transformations have the effect of simplifying the design and moving it to towards the next level. Figure 2-1 illustrates this transformation process.

At the initial level, advantage is taken of "high level" constructs such as adders, decoders and parity generators. For example, decoders may be present in the logic

FIGURE 2-1 Levels of Description in LSS

because of their presence in the initial description, or because they are discovered by a transformation. Transformations are applied at this level before the information inherent in these operators is obscured by their expansion to more primitive gates.

At the AND/OR level of description, transformations simplify the logic by bunching together nested AND/ORs and by doing straightforward simplification. In addition transformations convert the design into an equivalent NAND or NOR representation.

At the final technology specific level of description, technology constraints are enforced and advantage is taken of technology opportunities. Complex primitives present in the target technology, such as exclusive-ORs and parity functions, AND-OR and OR-AND combinations and multiplexors are utilized. Timing requirements are enforced at this stage of synthesis.

#### LSS In Use

LSS is used in a production environment as an automatic tool even though it was originally conceived as an interactive design system. With standard scenarios of transformation occurring repeatedly, users become familiar with the resulting output logic and performed less manual examination. LSS is particularly suited to completing first pass designs rapidly. With LSS sweeping design changes can be considered to solve timing problems. This ability to correct timing problems through *high-level* changes rather than low-level path tuning has contributed to the success of the project.

LSS did not fair well in refining logic designs. To make a design better seems to require information which is not available to the synthesis system such as global planning and "don't care" conditions. LSS would benefit from a knowledge engineering approach. With this approach, the designer would have the flexibility to incorporate additional rules as required to improve LSS design refinement performance. LSS is implemented in PL/1, and suffers from the limitations associated with that programming style.

#### Technology Adaptation

LSS has been designed to produce efficient, technology-specific implementations. Rather than using technology information throughout the scenario of transformations, LSS uses table driven transformations to give LSS adaptability to different technologies while maintaining the ability to produce designs which take the most advantage of the technology. With this technique, new technologies can be incorporated quickly. Technology specific information is used in the technology independent parts of the synthesis scenario as well as in the technology-specific section to help decide whether a particular transformation should be applied. This information is typically used to calculate the potential savings in replacing a grouping of gates. For example, size information about a generic primitive ( such as **OR** ), which gives the number of cells it would take to implement in the target technology, can be used to evaluate the potential savings in replacing a group of **NAND** or **NOR** gates by such a primitive. In fact LSS will evaluate all the potential replacement candidates, and perform the conversions in the ranked savings order.

## Timing

Timing is an important design criteria which must be considered for optimal circuit performance. The design goal of "speed" is usually to shorten certain critical paths on a

chip to meet design constraints, rather than to minimize all paths or total path length. LSS uses a technology specific delay calculator which computes the difference between the required and actual arrival times. This information is then used for timing correction transformations within LSS. These timing correction transformations attempt to meet the user-specified timing constraints, sometimes at the cost of area and power. The timing analysis procedure computes the worst case arrival time of a signal at any logic block input pin by tracing forward through the logic starting at the primary inputs, and it computes the worst case required time by tracing backwards through the logic ending at the primary outputs. The difference between the required and arrival times is the *slack*, which when negative indicates that a signal does not meet the required timing. The slack information is used by the timing correction transformations to determine their course of action.

## 2.3.3 DDL/SX (Digital Design Language/Synthesis eXpert)

DDL/SX [Saito 86] is a CMOS gate-array rule-based system for logic circuit synthesis. The system inputs technology-independent functional diagrams, and automatically generates conventional technology-dependent logic diagrams. A rule-based approach was adopted because the synthesis steps were not clear and were likely to change. This approach made it easy to incrementally improve the system's capabilities by adding, deleting, or modifying design knowledge represented as rules. Experimental results reported at Fujitsu in Japan, reveals that logic designs generated automatically are almost as good as the manual design, and that the design time is reduced by a factor of four. The DDL/SX synthesis system's development was motivated by a desire to avoid errors introduced by manual gate-level design, and to automate a task which occurs regularly in electronic telephone system design.

The production system was implemented using *ESHELL* which is a general purpose tool for building expert systems. It provides the kernal of a production system based on a "backboard model" [Craig 86], and an environment which facilitates knowledge base construction. Knowledge rules are classified as follows;

### (1) Macro expansion

These rules are knowledge about how to organize cells in order to implement a function of a macro.

## (2) **Optimization Rules**

These rules are for removing redundant cells, and for replacing a group of cells with a single cell.

## (3) **Constraint Check Rules**

These rules are for detecting and eliminating violations of design constraints such as fanout.

#### (4) Miscellaneous Rules

To interface the LSI with external circuits, I/O buffer cells and clock buffers must be inserted. Unused pins of the components should be connected to dummy cells which represent connections to ground or pull-up circuits. Scan path design rules are also included.

## (5) Scheduling Synthesis Tasks

Rules for scheduling the synthesis tasks and checking whether the problem has been solved are in this category.

Experimental results shows that designs generated automatically have approximately 20 % more unit cells, but are created in approximately one quarter the time (allowing for input and slight modification) compared to manual design. Actual CPU times for a circuit with 2,000 basic cells is approximately 10 secs on a FACOM M-380 15 MIPS machine.

#### 2.3.4 MACDAS Circuit Design System

MACDAS (Multi-level AND-OR Circuit Design Automation System) [Sasao 86] is a system developed at Osaka University which designs a multi-level circuit with fan-in limited AND-OR gates. To use MACDAS, the user presents the specification of the circuit in the form of a truth table, or a net-list of the circuit diagram, or an arithmetic expression. This input is processed as follows;

#### (1) **AND-OR Conversion**

The given specification is converted into an AND-OR two level circuit.

#### (2) **Two variable function generators**

Input variables are paired to produce an AND-OR two level circuit with twovariable function generators (TVFG). A TVFG generates all the functions of one and two-variables, and when inputs are paired each TVFG represents a "super variable"

31

#### (3) **Complement**

Some of the outputs are complemented to obtain a circuit with fewer AND gates.

## (4) Factorization

The circuit is transformed into a multi-level fan-in limited AND-OR circuit. This algorithm is based on finding common factors to resolve the fan-in limitations. The algorithm, which maximally reduces the number of gates is drawn from [Dietmeyer 78].

## (5) Local transformation

Finally the circuit is optimized by local transformations.

MACDAS uses two PLA optimization techniques. The first one is the optimal assignment of the input variables to PLA's with two bit decoders. The second is the optimal selection of the output phases. These optimization techniques produce designs which are better designed than would have been produced with a manual approach.

MACDAS is a useful tool for designing multi-level arithmetic circuits.

### 2.3.5 Socrates

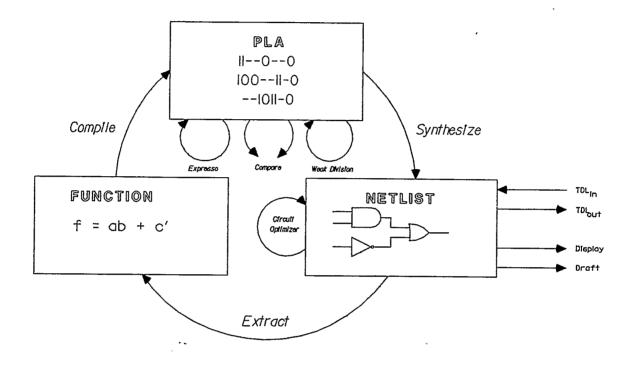

The *Socrates* System [Gregory 86] diagram is presented in Figure 2-2. To have the best representational form at each level, Socrates uses three different design representations.

A logic Level representation is required for operations which operate on the logic of the circuit. This *logic level* representation uses an extended version of *Expresso's* PLA format.[Brayton 84]

Figure 2-2 Socrates System Diagram

- (2) A circuit level representation is required for operations on circuits. They are represented using a *net-list format*.

- (3) A Boolean equation format for entering designs by hand.

Translators Compile, Synthesize and Extract, are provided to convert designs from one format to another. Compile converts Boolean equations to a two level Expresso format. Multilevel equations are flattened to two-level equations in this step. Synthesize

33

converts designs from the PLA format to the netlist format. Generic AND, OR and NOT gates are used to implement corresponding logic in this step. Extract converts a netlist to Boolean equations. *Extract uses a Boolean variable to represent each signal in the net-list, and writes an equation for each gate.*

A constraint specification allows designers to describe the desired characteristics of their circuit. Designers can specify when signals arrive at inputs, and the drive factor associated with them. Designers can specify the maximum propagation delays to individual outputs and the loads that must be driven at those outputs. Two programs *Expresso* and Weak Division perform logic level manipulations on designs. Expresso finds a minimum sum of products for each two level function. Weak Division decomposes two level functions into multiple levels by iteratively dividing out common subexpressions algebraically. The circuit optimizer program manipulates designs at the circuit level. The program improves circuit characteristics by iteratively replacing and rearranging groups of components in the circuit. It uses a library of alternate circuit implementations. The alternatives are given in the form of a rule, where conditions that are required to be true for the circuit are listed, if that alternative circuit is to be considered. Competing alternatives can thus be implemented in turn, and the performance of the circuit measured. After each rule application, an incremental timing and area analysis is performed. These analysis are based on user supplied values for timing and area models of each gate.

Before a rule is selected, transformations on the circuit resulting from its application are attempted. The program evaluates the effects a transformation will have on other transformations in the future by performing a state search. The depth and breadth of the search tree determine how far, and how exhaustively the program looks into the future before selecting a new rule. This look-ahead mechanism enables the *circuit optimizer* to choose transformations which do not immediately improve a circuit, but which lead to other transformations which do. This look-ahead feature is an example of the application of *meta-level inferencing* in SOCRATES. Meta rules control how area and speed are traded off against each other, and when and where CPU time is used.

## 2.3.6 Logic Design using Tokio & C-Prolog

A program which automatically synthesizes logical circuits for CMOS gate array from state diagram has been developed at the University of Tokyo ([Fujita 86]). This system is written in Prolog and Tokio [Aoyagi 85], where Tokio is a logic programming language which is based on temporal logic. Tokio can be considered as a version of Prolog that has been extended to describe concurrent processing.

#### Synthesis Program Description

The synthesis process is divided into six steps:

(1) **Convert DDL description to Prolog.**

DDL [Duley 68] is a well accepted hardware description language, which is used as a neutral file format to input the design. The DDL description includes "Terminal Transfer Tables", "Register Transfer Tables" and "State Transition Tables"

(2) Expand & Fetch common parts from similar logic expressions.

This is the first stage of simplification, which is illustrated by the following example:

$$T1 = A.B.C.D T2 = A.B.C.E$$

is converted to:

$$COM = A.B.C$$

$$T1 = COM.D$$

$$T2 = COM.E$$

## (3) **Primary Simplification: Eliminate duplicate units**

Four simplification rules are applied as appropriate.

**1.** Unification of units that have the same functions, same inputs, but different nets.

2. Simplification of AND or OR gates that have several identical inputs.

3. Simplification of multiplexer gates containing sets that have the same source under different conditions.

4. Simplification according to the replacement rules. Prolog is used to find circuit patterns where the replacement rules are applicable. Then the replacement rule is applied.

# (4) Analysis & modify the design according to the results.

Perform and analysis the number of gates, the delay time, the fan-in and fan-out and modify the result if there are any design constraint violations.

#### **Processing Results**

Performance of this synthesis system is quoted for a Unify Processor. This processor consists of approximately 500 TTL IC circuits and 17 internal registers. The DDL description consisted of 1000 lines.

The processing time on a VAX 11/730 is as follows;

|                 | Hours:mins |

|-----------------|------------|

| Phase 1         | 5:30       |

| Phase 2         |            |

| Expansion       | :40        |

| Cross-Reference | 11:30      |

| Phase 3         | 74:30      |

| Phase 4         |            |

| Fan-out         | 3:30       |

| Gate count      | :10        |

| Delay Time      | 2:00       |

|                 |            |

| Total           | 97:50      |

The initial design consisted of over 26,000 gates which was reduced, through simplification, by 10,000 gates or 40%.

## Conclusions

While this system shows that logic synthesis is practical, the processing times shows that 20,000 gates is approximately the limit of capability for an interpretive system. The greatest processing time occurred for primary simplification. It occurs as a result of the repeated backtracking as the various simplification rules are tested. With more clever program design it should be possible to reduce this processing time.

#### 2.3.7 DAA (Design Automation Assistant)

The Design Automation Assistant (DAA) [Kowalski 83] expert system was developed at Carnegie-Mellon University to investigate the application of Knowledge Based Expert Systems (KBES) for cost effective design of low-volume special purpose VLSI systems. DAA's area of expertise is allocating an architecture for a VLSI system. Its input is an algorithmic data-flow description of a VLSI system, and its output is a list of technology independent registers, operators, data paths and control signals. DA4 is implemented as a production system using the OPS5 [Forgy 81] Knowledge Based Expert System writing system. OPS5 facilitated the separation of expert knowledge from reasoning in DAA. Incremental addition of new rules and the refinement of old ones is easy because the rules have minimal interaction with one another.

DAA uses ordered subtasks to design the VLSI architecture. These subtasks are implemented using about 130 rules. Particular rules are applied if the specified conditions of the rule are met.

Experimental results from DAA indicate that a KBES approach to logic synthesis improves the performance of logic synthesis. Such an approach requires that the expert knowledge of design be explicitly defined. The definition of this knowledge aids our understanding of the design process and can also be used in the teaching process.

## **CHAPTER 3**

## Logic Programming

Logic programming is emerging as one possible technique for Computer-Aided Design (CAD) system development to cope with the recent increase in complexity of VLSI designs. Logic programming contrasts with current algorithmic solutions which are based on languages such as Fortran or C. This chapter discusses what logic programming is, and some specific advantages in its application to logic design.

#### **3.1 Logic Programming**

Logic Programming is a technique which combines logic clauses (or hypotheses) and a form of automatic logic deduction. Logic programming has gained acceptance as a suitable technique for implementing expert systems, and as a suitable programming technique for Japan's Fifth-Generation computer research and development project [Feigenbaum 83]. The theoretical basis of logic programming is Predicate Logic and the Resolution theorem [Chang 73].

The logic programming language **Prolog** ([Clocksin 81], [Cambell 84],[Pereira 84]) has gained wide acceptance throughout the AI community, and has been selected as one of the basic languages for Japan's fifth generation computer project. Prolog is a relatively new language, developed in the early seventies, which already has been used to develop specific expert systems for logic synthesis. Specific expert systems such as DFT (Design for Testability) [Hortmann 84] and DEMO, (meta Prolog experimentation sys-

tem), have been implemented in Prolog. Another system is under development at the University of Tokyo [Fujita 86]. Supporting such system development are numerous research papers which propose the use of the language for logic synthesis, simulation and testing ([Suzuki 85],[Gullichen 85], and [Noda 85]).

### **3.1.1 Prolog Logic Programming**

A Prolog program is a set of "Horn" clauses, but the notation differs slightly from the traditional notation. In classical logic, a Horn clause may be written as,

## P1&P2...&Pn -> Q

In Prolog syntax, the same clause would be expressed as,

### Q :- P1,P2,...Pn.

where the antecedent is written to the right of the implication arrow, the consequent to the left of the arrow, the arrow itself is reversed and is written as ":-" and the "&" signs are replaced by commas, with a full stop at the end. "Q" is put at the left of the antecedent to put emphasis that the antecedent constitutes the body of a procedure for calculating "Q" These clauses are both declarative, describing objects and their relationships and procedural, in that they are executed as functions. The symbol ":-" means "implied by" in the clause context. Each consequent and antecedent can be thought of as a function call of the form:

where "p" is an arbitrary predicate symbol, and "t1" through "tn" are terms. Clauses without antecedents are the facts of the system, while those without consequent clauses are used as goals.

A Prolog logic program usually consists of a set of rule and fact clauses which is used for the resolution of the goal clause. The goal clause is supplied from an external source. The resolution process involves matching the antecedents in the goal with conseqents in the fact and rule set, and then using those antecedents as subgoals. This resolution process continues sometimes recursively until either the empty goal is reached (thereby proving the goal to be true) or a match is unavailable. When a match is unavailable backtracking occurs. Backtracking is the process by which the Prolog interpreter selects alternative choices for subgoals if they are defined. If backtracking exhausts all possible alternative definitions of the subgoal, then the subgoal is unprovable, and it fails for the given set of facts and clauses. During this resolution process the variable terms encountered are unified ( "instantiated" ) across antecedents and consequents. It is these *instantiations* of variables that are used as answers when the goal is proved. Logic programs prove or disprove goals only in relation to the set of clauses (facts, rules and goals) provided.

Prolog has been criticized as falling short of the ideal logic programming language in two areas [Naish 83]

#### (1) **Poor Implementation of Negation**

Horn clauses can only be used to deduce positive information. The best way of dealing with negation using Horn clauses is to use the *closed world assumption*,

that is anything which cannot be proved true is assumed to be false. This cannot be easily implemented so Prolog uses a weaker rule, *negation as failure*. A goal is assumed to be false if the interpreter finds a finite proof that the goal is unprovable. Most Prolog systems implement the clause not(p(X)) with a meaning of,

$$not(p(X)) \iff for all X, p(X)$$

rather than,

$$not(p(X)) \ll there exists X such that p(X)$$

### (2) Inadequate Control Facilities.

The basic control facilities of Prolog are just the ordering of clauses and atoms within clauses. Once a program has been written in a particular way, the clauses and sub-goals are always tried in the same order. While facilities such as *cut* and *var* partly overcome these problems, correctness and clarity suffers. Prolog's poor control facilities leads to poor program reliability, infinite loops and inefficient algorithms.

Two improved Prolog systems have been developed which overcome these problems of the basic system.

MU Prolog [Naish 83] comes closer to the goals of logic programming addressing the negation and control facility problems of Prolog. MU-Prolog uses a system of delaying and resuming calls to clauses to provide more flexibility, efficiency and termination. Negation is implemented soundly by delaying the computation of the clause to be negated. The clause is *woken up* when the variables in the clause are bound.

(2) IC-Prolog is probably the best known Prolog system with improved control [Clark 81]. In IC-Prolog, control information is specified by adding annotation to the program clauses. There are a wide range of annotations, and for certain applications IC-Prolog can achieve more efficient algorithms than MU-Prolog.

### 3.2 Prolog as an Expert System Shell

Rule-based languages are generally considered to be the most suitable for representing knowledge in expert systems. Rules are relatively easy to understand, and their modularity makes modification easy during knowledge base development and use.

Horn clause logic can be viewed as a rule-based language, which with appropriate extensions, it is a candidate for representing knowledge in an expert system. Any collection of Horn clauses can be run directly as a Prolog program. It has been commented [Hammond 83], that for some applications, running the expert system rules as a Prolog program is adequate, and the implementation of the expert system becomes trivial. However, two *important* expert system shell features are not automatically available in Prolog.

- (1) Prolog does not provide *automatically* an ability to explain and justify reasoning.

- (2) Prolog does not provide *automatically* a request for data based on inference.

However, such features can be added to a Prolog program.

3.2

Prolog has the advantages of uniformity and extensibility. Uniformity is provided in the form of rules that can perform both program control and data manipulation. To further refine the expert system, rules can be modified or added. One preliminary conclusions on the use of Prolog for DFT [Horstmann 84] [Horstmann 84] - CAD Using Logic Programming suggest that rules can be added or changed easily, even while using the system, and this feature was especially useful in developing and debuging the system. Careful system design which separates rule function gives a Prolog program "modularity" to adopt to design changes.

The efficiency of a Prolog program or the lack of it is a key concern for the acceptability of Prolog as the development language. If the task is numerically intensive, or if it can be procedurally defined then the task might be better suited to a procedural language which would execute more efficiently than Prolog. In later chapters it can be shown that there are many aspects of logic design which are best implemented in Prolog. Even if the task may be suitable to Prolog, if a subtask of the design process does not lend itself to Prolog programming, it can make sense to implement that task using a procedural language. A combination of Prolog and an efficient procedural language can provide considerably better overall performance when compared to a system programmed only in Prolog, without having to compromise any of the benefits offered by Prolog.

The performance and efficiency of Prolog depends on the system programmer understanding of the problem and how solutions can be obtained. It has been illustrated in many texts on logic programming [Bundy 83] that the existance of a solution does not guarantee that a solution will be found by the Prolog interpreter. It is thus necessary for searching to be guided to obtain the solution in the fastest possible way. A Prolog system designer should always place "likely" rules first in a Prolog program, so that those rules are tested first. Backtracking, as the Prolog interpreter "tests" alternate rules is the major source of inefficiency in Prolog programs.

### 3.3 The Case for a Clausal based Expert System Approach

The advent of VLSI technology has put considerable strains on current design techniques in dealing with the growth in design complexity. Even hierarchical design techniques, which were introduced to deal with the complexity issue, are often inadequate to match downwardly imposed design criteria and upwardly imposed physical constraints. This thesis is in support of a clausal based expert system approach to design as the most effective long term strategy for inexpensive exploitation of VLSI technology. Such a design technique will make low-volume special purpose chips economically feasible.

Others support this design approach [Brewer 86], and propose a new model of design which is based on communicating expert systems which operate at different levels of design abstraction. The purpose of the expert on a given level is to create a structure out of the design components predefined for that level. With this approach design is not forced in a top to bottom fashion with little consideration for factors which arise at lower levels. Design still proceeds top to bottom as each level is completed, with the provision that any level may fail in its attempt to achieve its goal. When this occurs, control passes back to the parent in the form of a failure report. The higher level task may decide to reallocate constraints, or change styles, or indeed fail itself. This procedure allows back-tracking of earlier design decisions between levels of the design hierarchy, forcing

iterative refinement of design. It also effectively manages both upward and downward propagation of design styles and parameters. Constraint propagation and failure reporting augment the completed design specification, and can aid the "expert designer" to complete his design in much the same way as the human designer.

Although [Brewer 86] does not propose any specific language for implementing this model of design, the author suggests Prolog as suitable for the task. Prolog has many characteristics which would facilitate such an expert system model for design;

### (1) **Backtracking**

Prolog's backtracking feature is directly useful for implementing the failure reporting feature between levels of design abstraction.

## (2) Expert System Language

Prolog has been used to implement Knowledge Based Expert Systems. There are KBES logic design systems ie DEMO, LSS.

#### (3) **Rule based Language**

Prolog is a rule based language with a built in simple inference mechanism.

## (4) **Timing Representation**

Concurrent Prolog is available to represent the timing element of a design.

#### (5) **Unifying Language**

Prolog could be used for all aspects of system development, thereby unifying or linking these expert systems together. Prolog clauses are both declarative, in that they describe objects and relationships, and procedural in that they are executed as functions.

# (6) Circuit Transformation

Prolog re-write rules facilitate circuit transformations. These transformations are required frequently in logic synthesis, logic minimization and for technology conversion.

\*\*

### **CHAPTER 4**

#### **Circuit Representation in Prolog**

This chapter presents two techniques for representing and manipulating circuits which are available in Prolog - data structures and Horn clauses. Circuit representational techniques are introduced first because they determine which manipulations can be performed easily. The PCD program (described in chapter 7) is based on a Prolog data structure circuit representation.

## 4.1 Circuit Representation in Prolog

In choosing a representational technique two questions are normally posed. Does the representational technique make efficient use of memory ? Does the representational technique allow for efficient manipulation ? Unfortunately it is very hard to find a technique which optimizes both these requirements simultaneously. A circuit which is represented using sets of Horn clausal statements presents circuit information suitable for logic manipulations, but this representation does not make the most efficient use of memory. A circuit represented as a Prolog data structure is stored more efficiently, but cannot be accessed in the same manner as in a Horn clause representation. These techniques are fully described in the following sections.

## 4.2 Prolog Horn Clause Circuit Representation

Digital logic circuits can be viewed as a network of primative gates whose interconnection imposes constraints. Satisfying the constraints with some lines bound to some constant values serves to simulate the operation of the circuit. Many features of Prolog

48

:

make it suitable to direct representation and simple simulation of logic circuits.

The following are characteristics of a Prolog Horn clause circuit representation;

#### (1) Functional & Physical Characteristics

The Prolog database mechanism can record both functional and physical characteristics of logic elements.

#### (2) Hierarchical Circuit Representation

Prolog representation facilitates an abstraction of complexity using hierarchical descriptions. In digital circuitry, the subsystems tend to be homogeneous. Smaller components are replicated and interconnected to produce a larger piece of hardware. Hence, arbitrarily complex circuits, within implementation limits of the Prolog interpreter, may be constructed in a hierarchical manner.

### (3) **Parallel Circuit Representation**

Parallelism of physical computer components are closely modeled using Concurrent Prolog [Suzuki 85]. Concurrent Prolog is very similar to Prolog, but it has multiprocessing features which make it suitable for describing and simulating highly concurrent systems.

#### (4) Forward and Reverse Simulation

As inputs and outputs of a Prolog predicate need not be specified, but may be left unbound at the time a predicate is invoked. These inputs are instantiated through the action of the Prolog interpreter, to make the predicate true. With these features, Prolog is very amenable to functional simulation of many circuit types.

Functional simulation is an alternative to transistor-level logic simulation.

4.2

It is often a better alternative because the circuit model, which can be modeled at any desired level of abstraction, can be generated quickly and the functional simulation, which is written at an abstract level is more efficient. A Prolog simulator provides an effective methodology to create a functional specification in a high level language and to debug these specifications against test data. Simulation can occur in the forward as well as the reverse direction, and even bidirectionally. The ability to efficiently perform backwards simulation is useful in both fault detection test generation and deductive methods for fault isolation.

## (5) **Don't Care Values**

As Prolog can deal with unbound variables, the problem of "don't care" and "don't know" values is simplified.

Any logic gate, such as an AND gate, can be directly represented in Prolog as a collection of axioms which describe its behavior. For example, a 2-input AND gate is functionally specified by the following 4 Prolog axioms;

> and(in(0,0),out(0)). and(in(0,1),out(0)). and(in(1,0),out(0)). and(in(1,1),out(1)).

Queries may be posed to Prolog to simulate operation of the AND gate:

!?- and(in(0,1),out(X)).

X=0,

yes.

!?- and(in(X,Y),out(1)).

X=1,

Y=1,

yes

In the first query, the operation of the AND gate has been simulated in the forward direction, with gate inputs being propagated forward to the output. The second query is an example of a backward simulation, and operates in a manner in which the hardware cannot. Gate output is propagated backward to the inputs. The query asks what inputs X and Y to the AND produce an output of 1. By matching the axioms in the database, Prolog indicates that both inputs must be 1.

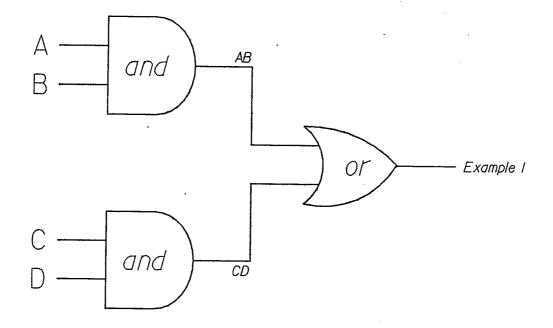

So far we have considered only the representation of a two value primative logic *AND* gate. This technique may be employed for representing gates which implement multivalue logic, and for representing more complex combinational circuits. Consider the representation of the logic function represented by Figure 4-1. Figure 4-1 represents a simple combinational logic circuit. Circuits are fashioned from an interconnected network of logic gates, and may be represented by Prolog implications in a manner amenable to simulation. This circuit could be represented as Prolog predicate circuit as: