UNIVERSITY OF CALGARY

# Differential Threshold Reliant Detectors for Ternary Partial Response Channels

by

Omole, Ibiyemi Akintomide

#### A DISSERTATION

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

NOVEMBER, 2003

© Omole, Ibiyemi Akintomide 2003

### UNIVERSITY OF CALGARY FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a dissertation entitled "Differential Threshold Reliant Detectors for Ternary Partial Response Channels" submitted by Omole, Ibiyemi Akintomide in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

and

Supervisor, Dr. B. J. Maundy Department of Electrical and Computer Engineering

Dr. A. B. Sesay Department of Electrical and Computer Engineering

Dr/J. W. Haslett Department of Electrical and Computer Engineering

Dr. N. El-Sheimy Department of Geomatics Engineering

Jaude

External Examiner, Dr. V. C. Gaudet Department of Electrical and Computer Engineering University of Alberta

10/03

### Abstract

An in-depth look at the detection problem of both fundamental Partial Response Signaling (PRS) channels; duobinary (1+D) and dicode (1-D) used in a ternary mode is addressed in this dissertation from the Maximum-Likelihood Sequence Detection (MLSD) stand-point. Literature surveys reveal that the ternary partial response signaling channel detector(s) would be very helpful in simplifying detectors for higher order partial response signaling channels.

Literature surveys further show that the detection problem of ternary duobinary and dicode channels have not been efficiently dealt with in either the analog or digital domain and only a handful of research publications exist on the issue.

Mathematical derivation from first principles for a new detection algorithm for both channels from the difference metrics perspective is presented. Analysis, interpretation and characterization of the algorithms in the analog domain were done to provide a better insight to their functionality. The algorithms sensitivity and robustness to undesirable analog effects such as saturation effects was investigated.

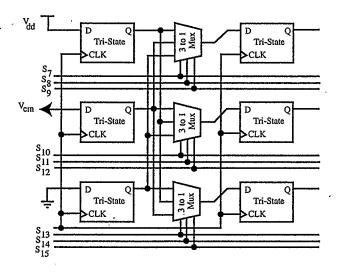

The algorithm translation for hardware implementation was carried out and implementation of an architecture was investigated. For proof of concept and also as the first to be reported for the ternary PRS channel detector implementation, a mixedsignal detector circuitry was designed using digital CMOS  $0.18\mu m$  technology with a single 3.3V supply and simulation showed a maximum working speed of 100MHz for the design.

The design was fabricated and experimental tests were conducted. Experimental analysis and problems encountered were discussed and the dissertation concludes with future work.

### Acknowledgement

My sincere and very profound gratitude goes to my supervisor Dr. Brent Maundy for providing me with the opportunity to be able to pursue my research interest, for always finding time to guide me through the course of the research, and for his patience and support during the time I was still groping for the way forward.

I would also like to thank Dr. Abu Sesay for his immense contributions, suggestions and positive critics to this research. Thanks for believing that a worthwhile research could stem from this topic. You are appreciated.

Also, Dr. Bob Davies (TRLabs) is well deserving of my thanks for helping to provide access to very vital equipments for the testing of my chip. To Simon Arseneault (TRLabs), I appreciate your help during the course of the experiment. John-Peter Vanzelm, thank you for all your assistance in securing the test space. Balvinder Vardee (Agilent Technologies), your provision of the Infiniium oscilloscope was timely and it is very well appreciated. John Shelley and Angela Morton you are both awesome; thanks for your technical assistance.

My parents, brother and sisters, I love you all for your continual support and prayers. My wife, thanks for being the light in my dark hours. You were always there for me when I was discouraged. Moreover, thank you for being selfless and understanding while my interest got in the way of our life together.

Lastly but not the least, I would like to show my appreciation to Mr. A. A. Akinola, Mr. Tony and Mrs. Idowu Osibodu, Dr. J. B. Olomo (Physics Department, O. A. U. Nigeria), Dr. G. O. Ajayi (Electronic and Electrical Engineering Department, O. A. U. Nigeria), and Dr. C. Papavassiliou (Imperial College, London) for your fatherly advice and timely support.

## Dedication

To my Parents, my wife Olanike

#### and

## my precious daughter Eyilayomi

v

# Contents

|          | App                              | roval Page                                                                     | i                                 |

|----------|----------------------------------|--------------------------------------------------------------------------------|-----------------------------------|

|          | Abst                             | tractii                                                                        | i                                 |

|          | Ackı                             | nowledgement                                                                   | v                                 |

|          | Dedi                             | ication                                                                        | v                                 |

|          | Cont                             | tentsi                                                                         | x                                 |

| •        |                                  |                                                                                | x                                 |

|          | List                             | of Figures                                                                     | v                                 |

|          | List                             | of Symbols                                                                     | ri                                |

|          | $\operatorname{List}$            | of Acronyms                                                                    | x                                 |

|          |                                  |                                                                                |                                   |

| 1        | Intr                             | oduction                                                                       | 1                                 |

| 1        | Intr<br>1.1                      |                                                                                | <b>1</b><br>1                     |

| 1        |                                  | Background                                                                     | -                                 |

| <b>1</b> | 1.1                              | Background                                                                     | 1                                 |

| 1        | 1.1 $1.2$                        | Background                                                                     | 1<br>3<br>4                       |

|          | 1.1<br>1.2<br>1.3<br>1.4         | Background       Trend and Motivation       Research Objectives       Overview | 1<br>3<br>4<br>6                  |

| 1<br>2   | 1.1<br>1.2<br>1.3<br>1.4         | Background                                                                     | 1<br>3<br>4                       |

|          | 1.1<br>1.2<br>1.3<br>1.4         | Background                                                                     | 1<br>3<br>4<br>6                  |

|          | 1.1<br>1.2<br>1.3<br>1.4<br>Lite | Background                                                                     | 1<br>3<br>4<br>6<br><b>8</b><br>8 |

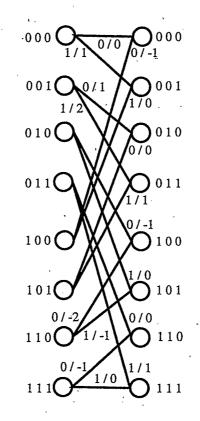

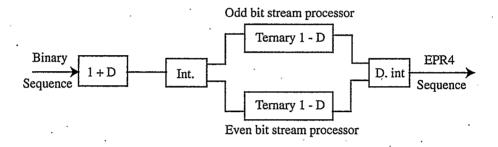

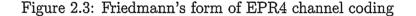

|     | 2.3            | EPR4 Channel Detection ,                        | 13 <sup>.</sup> |

|-----|----------------|-------------------------------------------------|-----------------|

|     |                | 2.3.1 Wood's Detection Scheme                   | 15              |

| ,   | 1              | 2.3.2 Friedmann's Detection Scheme              | 15              |

|     |                | 2.3.3 Knudson's Detection Scheme                | 17              |

| , g | B A P          | ew Detection Algorithm: The Derivation          | 18              |

|     | $^{\cdot}$ 3.1 | A Preview                                       | 18              |

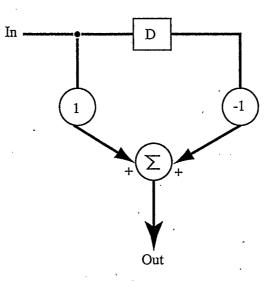

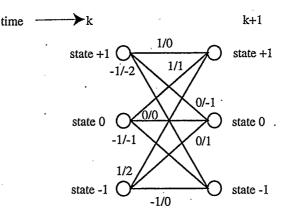

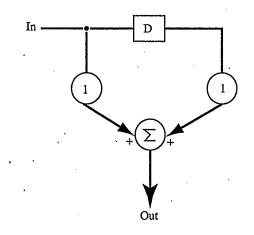

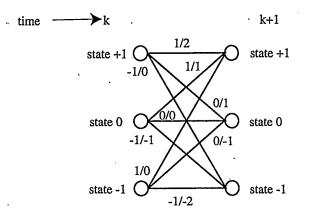

|     | 3.2            | Ternary Dicode Channel                          | 19              |

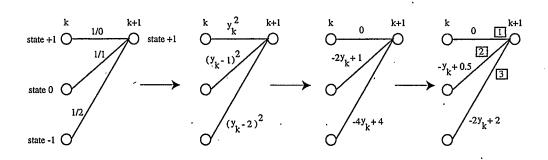

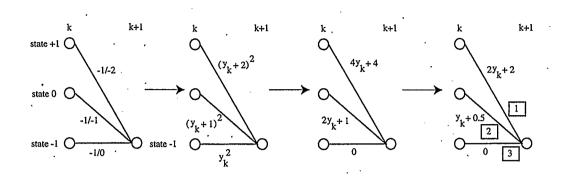

|     |                | 3.2.1 States Survivor Derivation                | 20              |

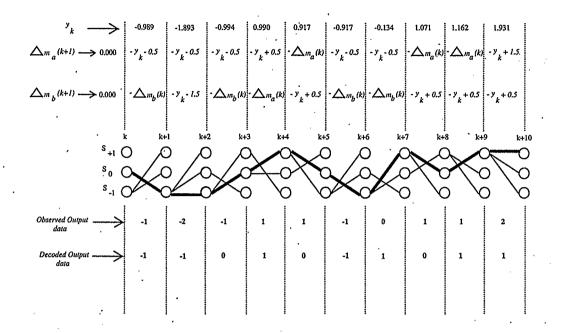

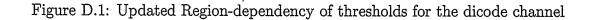

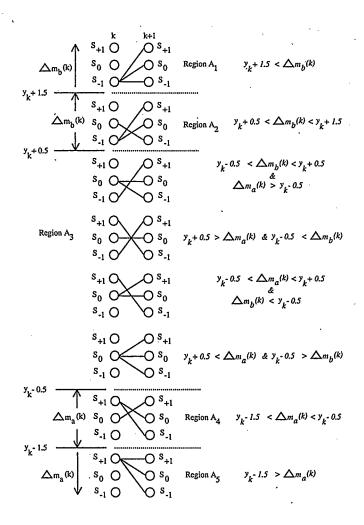

|     |                | 3.2.2 Merger Observations                       | 24              |

|     | •              | 3.2.3 The Updates                               | 26              |

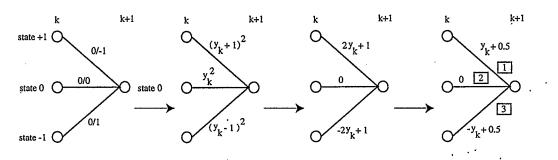

|     | 3.3            | Ternary Duobinary Channel                       | 31              |

|     |                | 3.3.1 States Survivor Derivation                | 32              |

| ٠   |                | 3.3.2 Merger Observations                       | 34              |

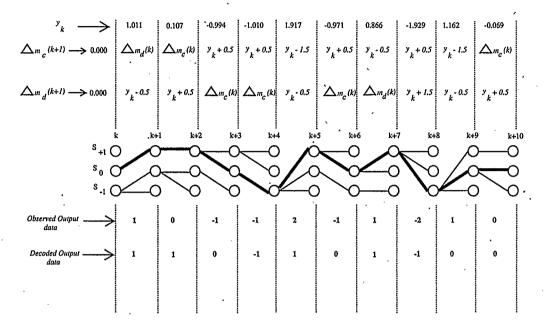

|     | 3.4            | Preliminary Evaluation                          | 36              |

| 4   | l Inte         | rpretation and Characterization                 | 42              |

|     | 4.1            | An Interpretation                               | 42              |

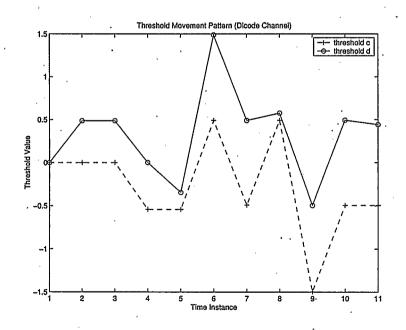

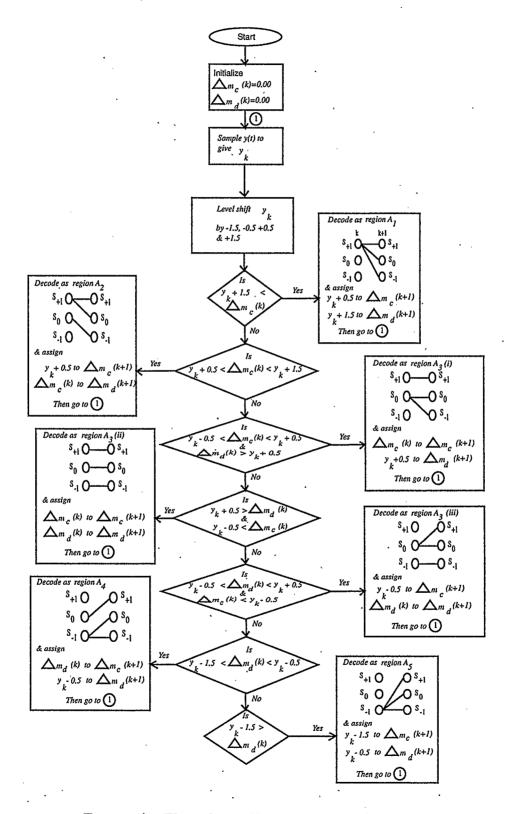

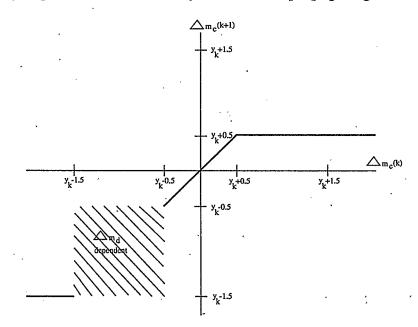

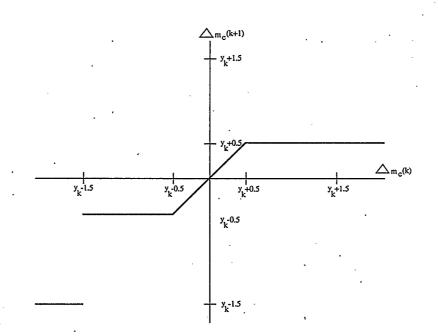

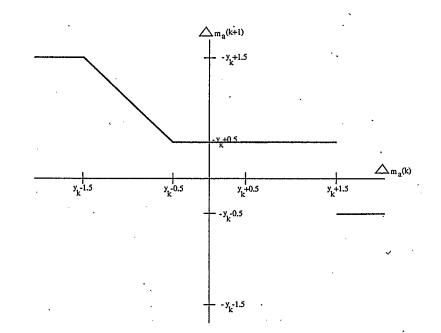

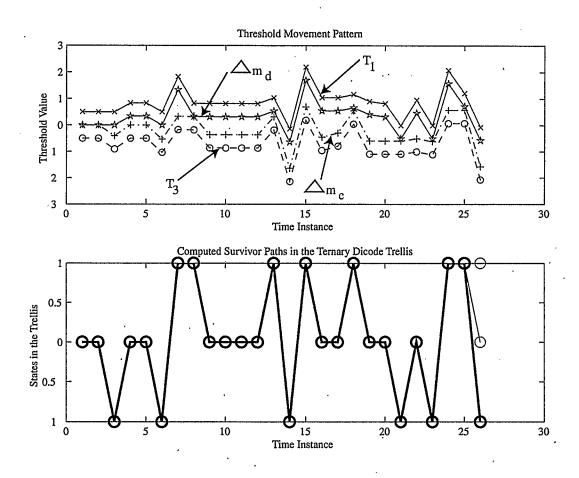

|     |                | 4.1.1 Ternary Dicode: Threshold $\Delta m_c$    | 43              |

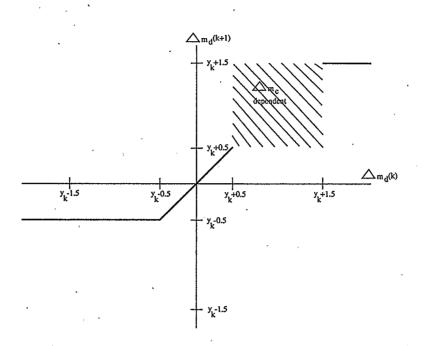

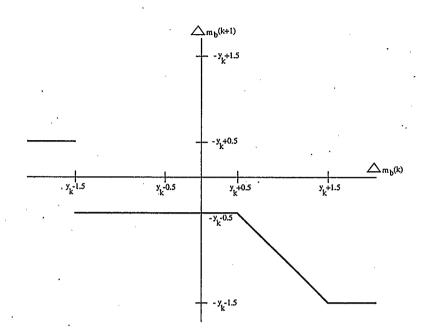

|     |                | 4.1.2 Ternary Dicode: Threshold $\Delta m_d$    | 46              |

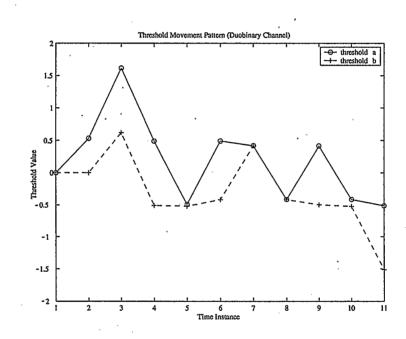

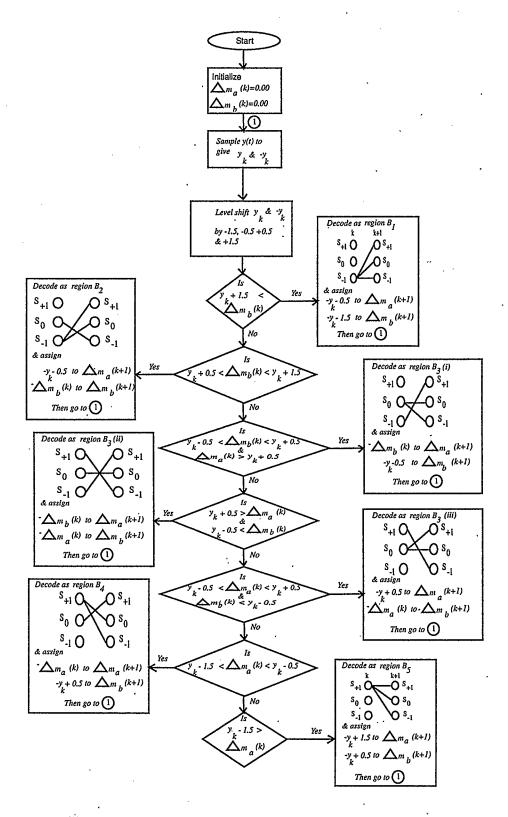

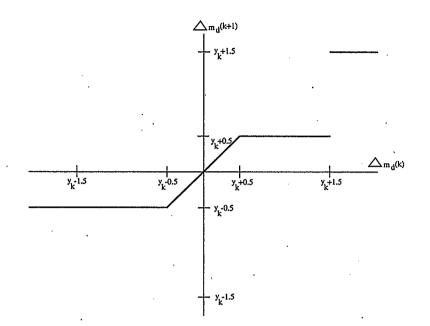

|     |                | 4.1.3 Ternary Duobinary: Threshold $\Delta m_a$ | 47              |

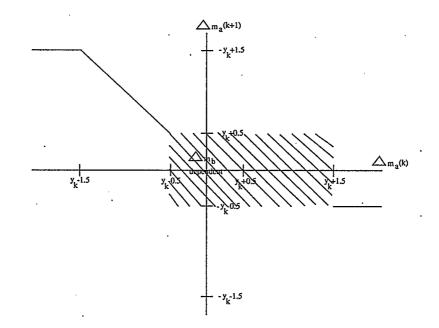

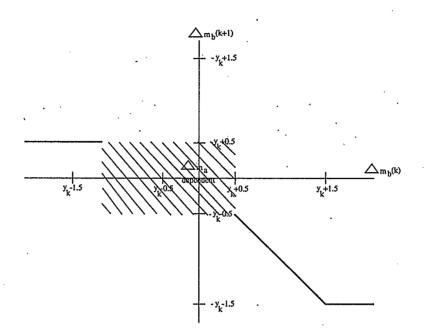

|     |                | 4.1.4 Ternary Duobinary: Threshold $\Delta m_b$ | 48              |

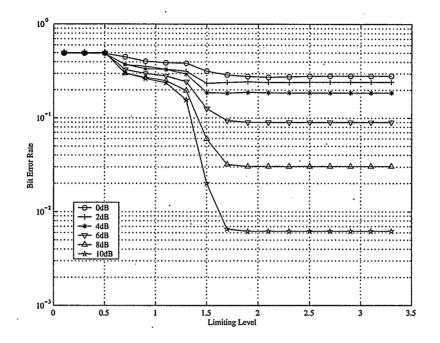

|     | 4.2            | Saturation Effect                               | 50              |

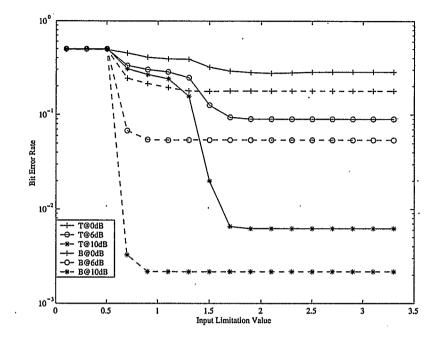

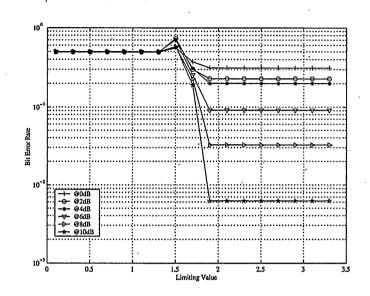

| ,   |                | 4.2.1 Ternary Dicode: Input Limitation          | 52              |

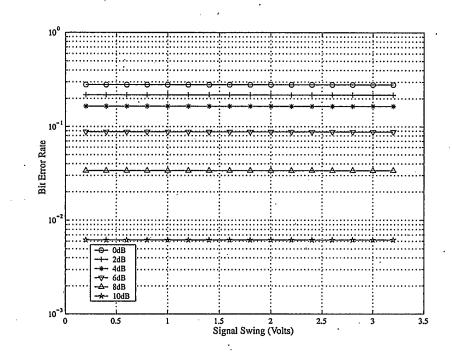

|     |                | 4.2.2 Ternary Dicode: Signal Swing Limitation   | 55              |

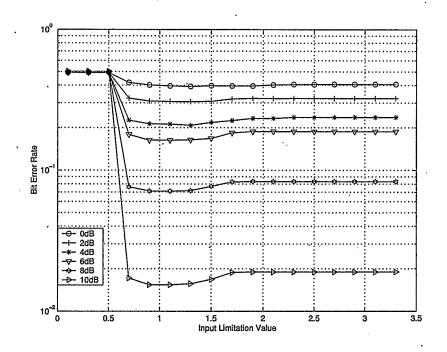

|     |                | 4.2.3 Ternary Duobinary: Input Limitation       | 56              |

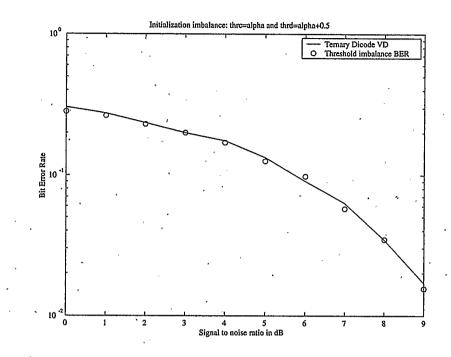

|   | 4.3                  | Error   | Rate Performance                                       | 57                |

|---|----------------------|---------|--------------------------------------------------------|-------------------|

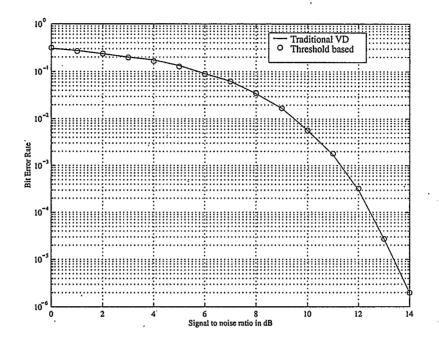

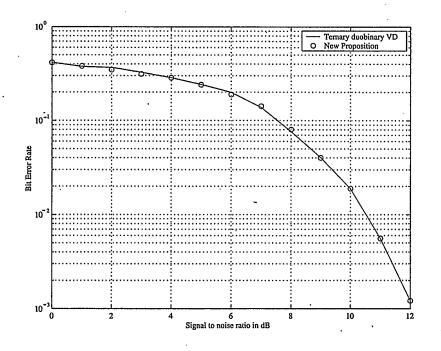

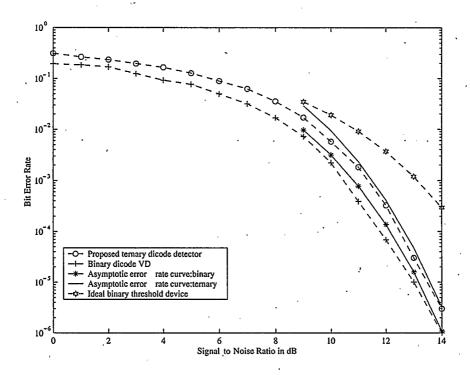

|   |                      | 4.3.1   | Ternary Channel Detection vs. Binary Channel Detection | 58                |

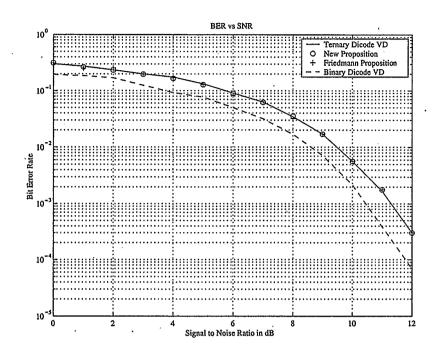

|   |                      | 4.3.2   | New technique vs. Friedmann's technique                | 61                |

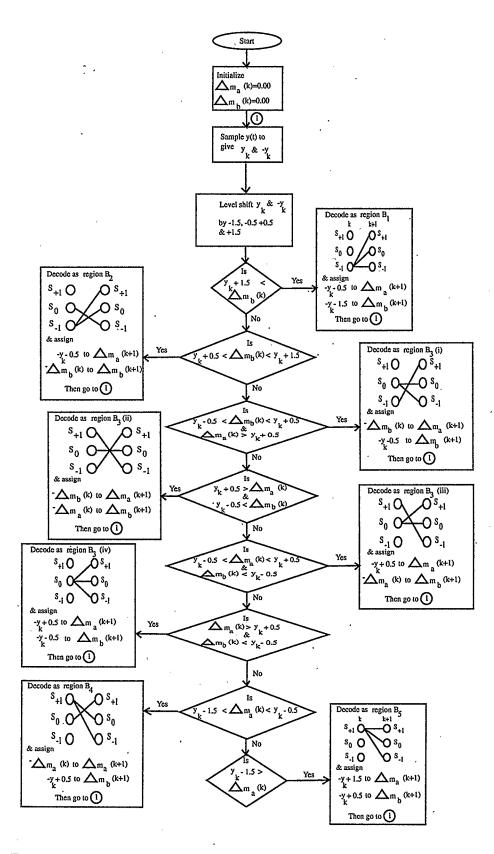

| • | 4.4                  | Algori  | thm translation for hardware implementation            | 64                |

| 5 | $\operatorname{Det}$ | ector ] | Design and Implementation                              | 68                |

|   | 5.1                  | Archit  | ectures                                                | 68                |

|   | 5.2                  | Detect  | or Design                                              | 71                |

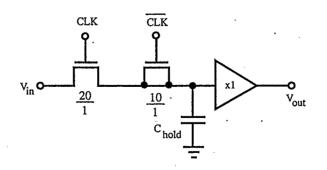

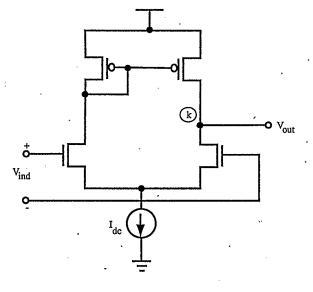

| • |                      | 5.2.1   | Input Track and Hold circuit                           | 71.               |

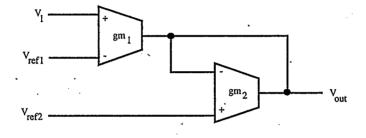

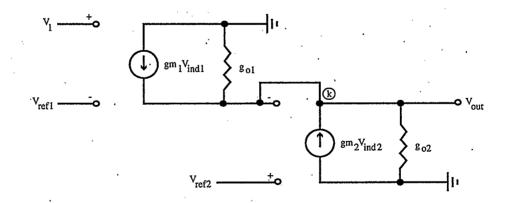

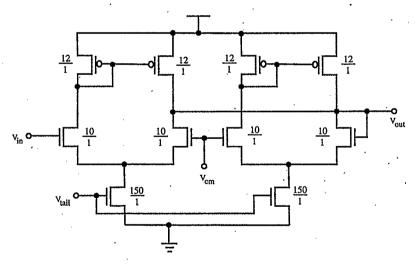

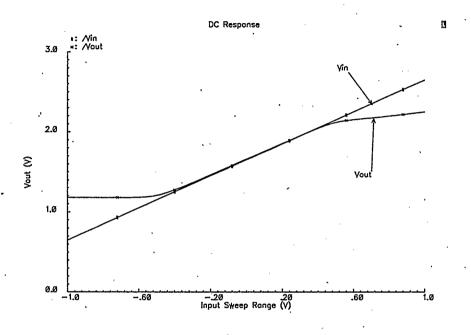

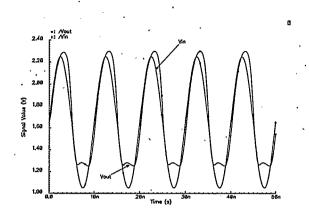

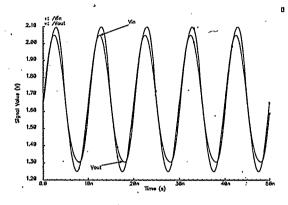

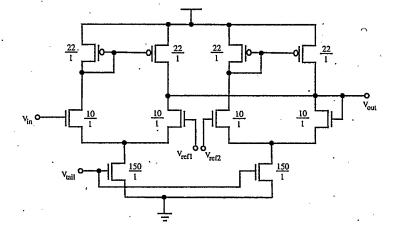

|   |                      | 5.2.2   | Buffer circuitry                                       | 74                |

| • |                      | 5.2.3   | Level-shifting circuitry                               | 77                |

|   | . ,                  | 5.2.4   | The clocked comparator                                 | · 79 <sub>.</sub> |

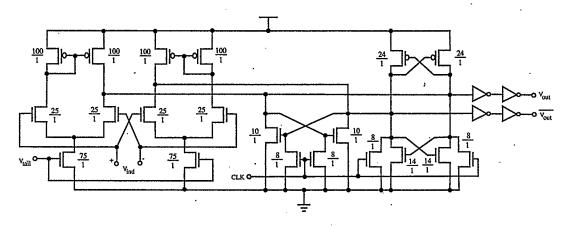

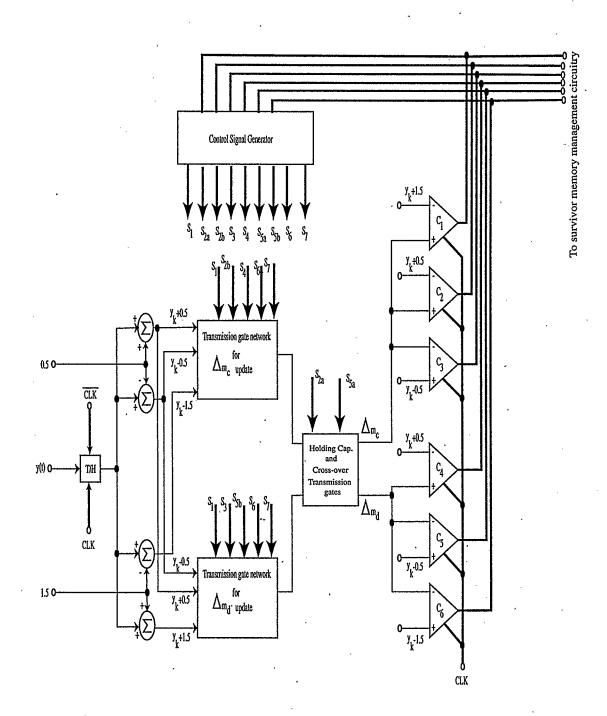

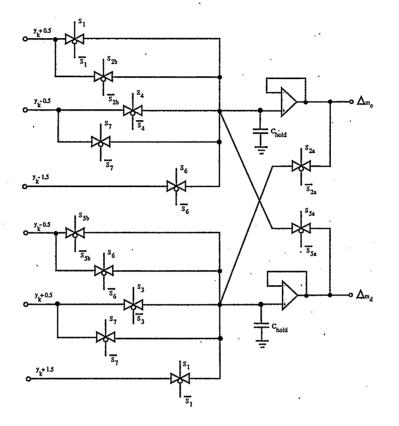

|   |                      | 5.2.5   | The Cross-over Multiplexing T/H                        | 83                |

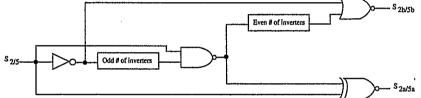

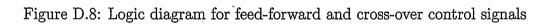

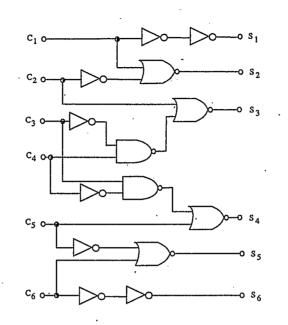

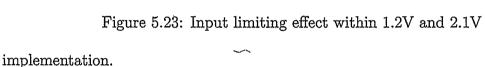

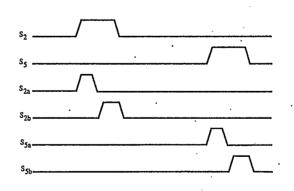

|   |                      | 5.2.6   | Control Signal Generator                               | 85                |

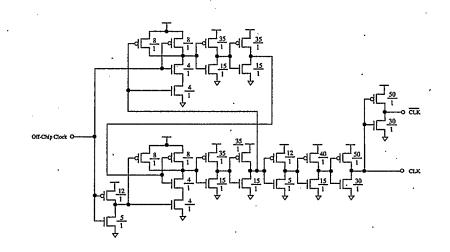

|   |                      | 5.2.7   | Clock Generator                                        | 85                |

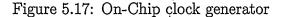

|   |                      | 5.2.8   | Bias Circuitry                                         | 86                |

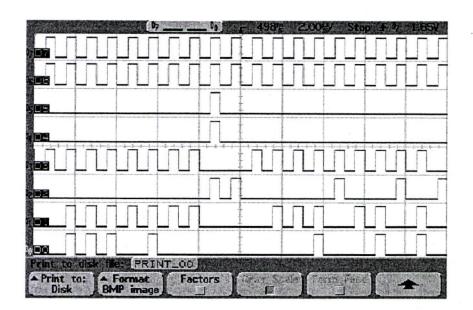

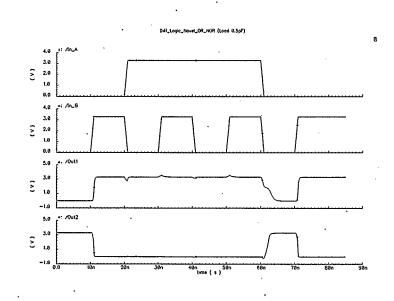

|   | 5.3                  | Detect  | tor simulation results                                 | 87                |

|   |                      | 5.3.1   | Detector decisions                                     | 90                |

|   | 5.4                  | Surviv  | vor Memory Management                                  | 94                |

|   | 5.5                  | Exper   | imental Results                                        | 97                |

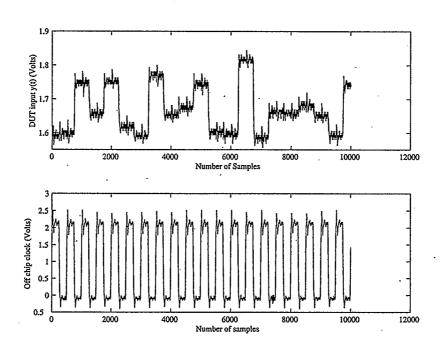

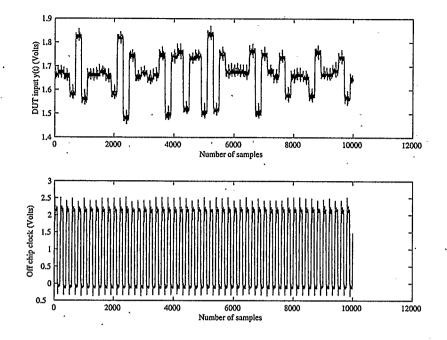

|   |                      | 5.5.1   | Test Signal Generation                                 | 97                |

|   |                      | 5.5.2   | Chip Test Bench                                        | 100               |

|   |                      | 5.5.3   | Experimental Data Analysis                             | 102               |

| 6 | Rela                 | ated R  | lesearch Work                                          | 112               |

|   | 6.1                  | Loser-  | Take-All Circuits                                      | 112               |

viii

|              |             |                                                                                                                                                      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |             | 6.1.1                                                                                                                                                | A New Proposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113 .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |             | 6.1.2                                                                                                                                                | First Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •            |             | 6.1.3                                                                                                                                                | Second Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

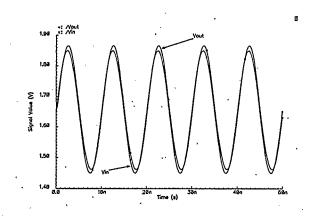

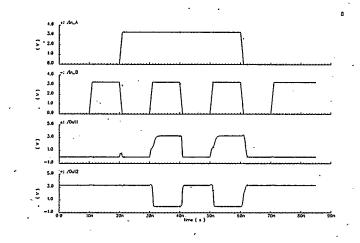

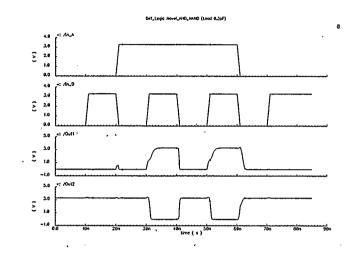

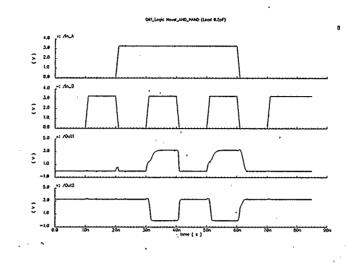

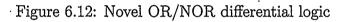

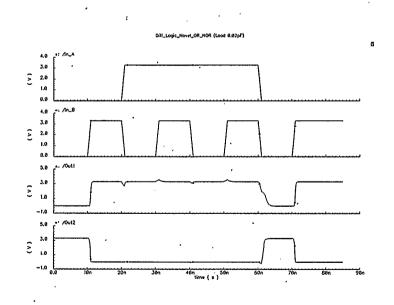

|              | -           | 6.1.4                                                                                                                                                | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | $6.2 \cdot$ | Novel                                                                                                                                                | Differential Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

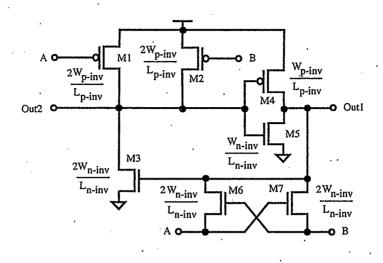

|              |             | 6.2.1                                                                                                                                                | Differential AND/NAND Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

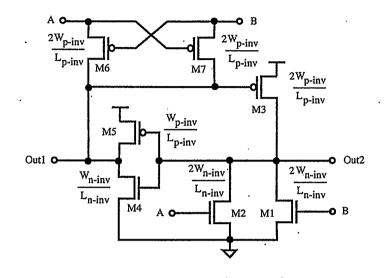

|              |             | 6.2.2                                                                                                                                                | Differential OR/NOR Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7            | Con         | tribut                                                                                                                                               | ions, Future Work and Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | 7.1         | Contr                                                                                                                                                | ibutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | 7.2         | Futur                                                                                                                                                | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ,            | 7.3         | Concl                                                                                                                                                | usion $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\mathbf{A}$ | Duc         | binar                                                                                                                                                | y channel detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | A.1         | Deriva                                                                                                                                               | ation of updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| в            | Lim         | itatio                                                                                                                                               | n Effect: Ternary 1-D channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | B.1         | Positi                                                                                                                                               | ve plane limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | B.2         | Negat                                                                                                                                                | ive plane limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| С            | Det         | ector                                                                                                                                                | Output Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

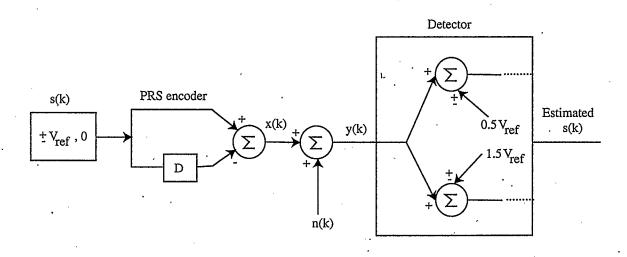

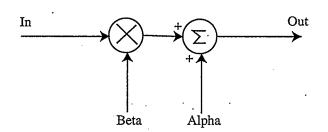

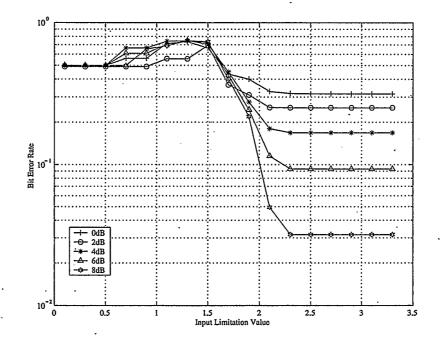

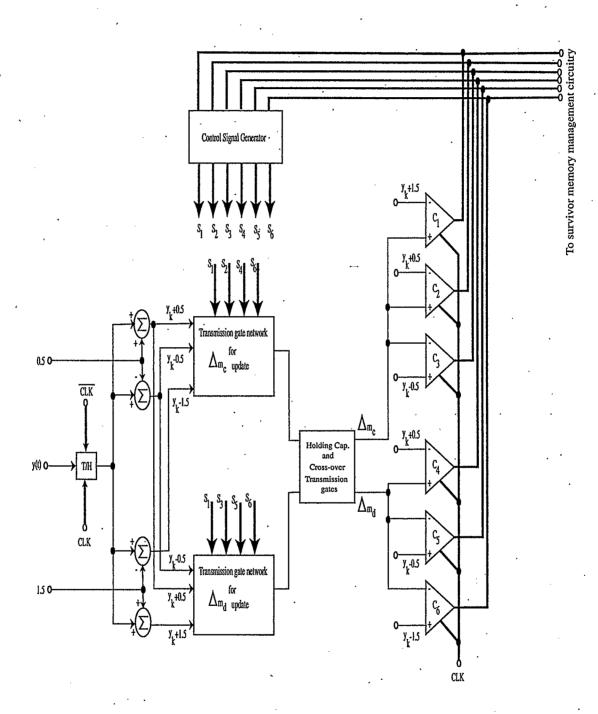

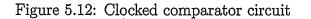

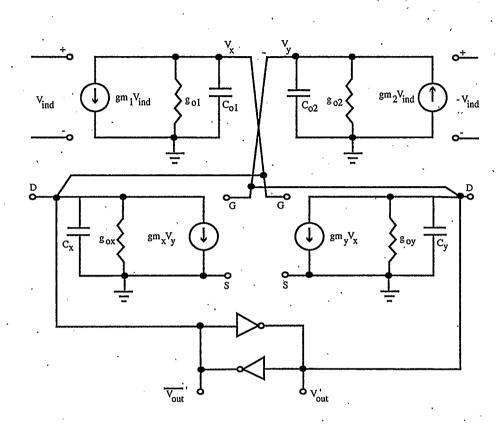

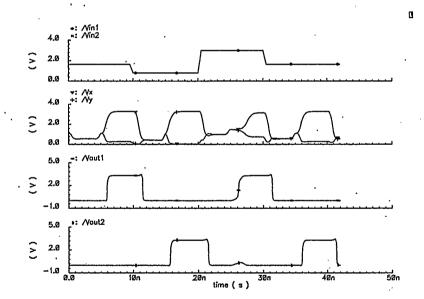

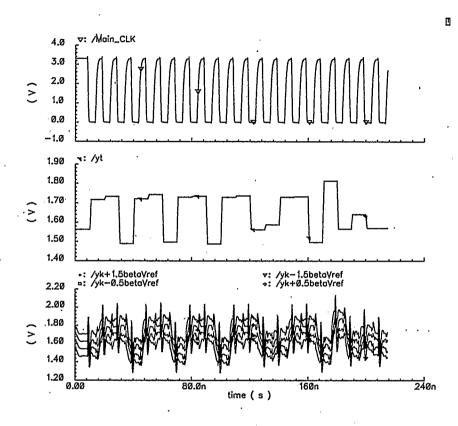

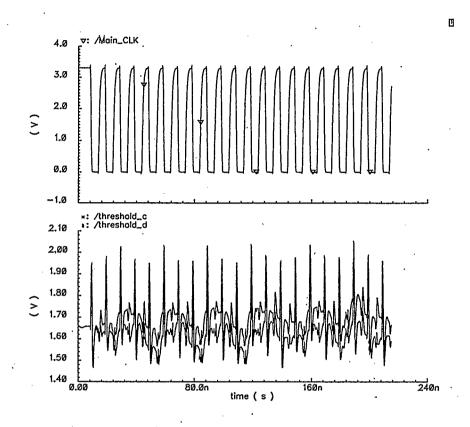

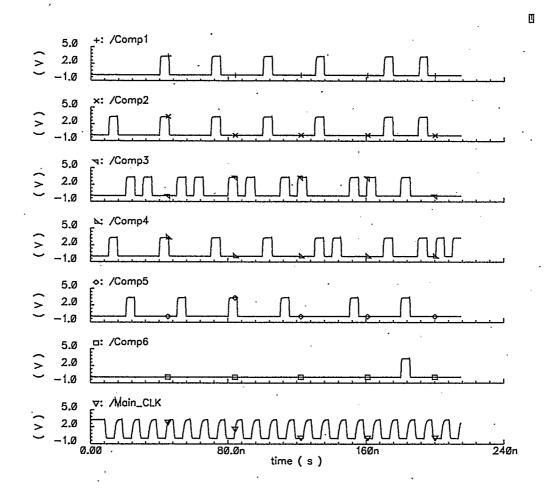

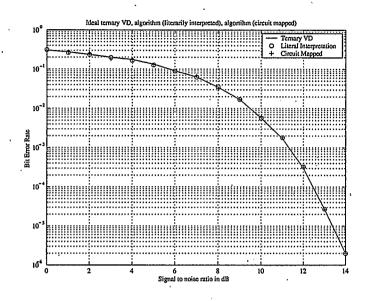

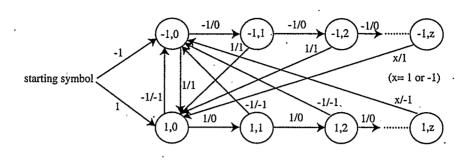

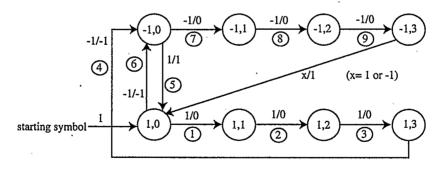

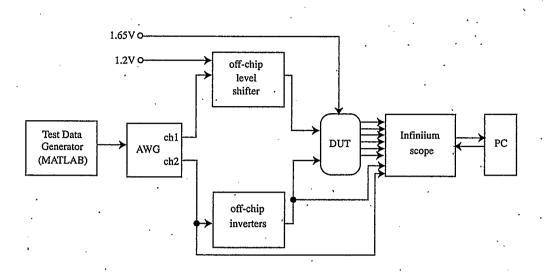

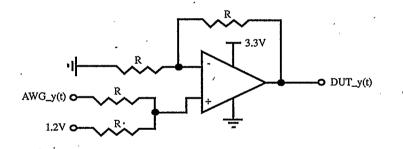

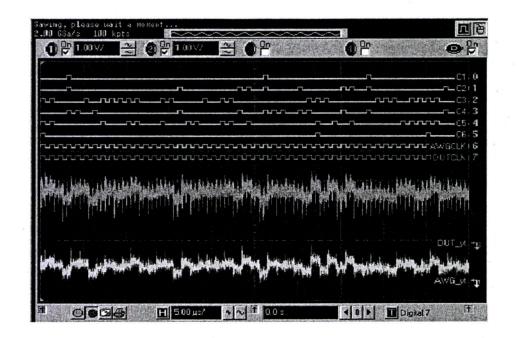

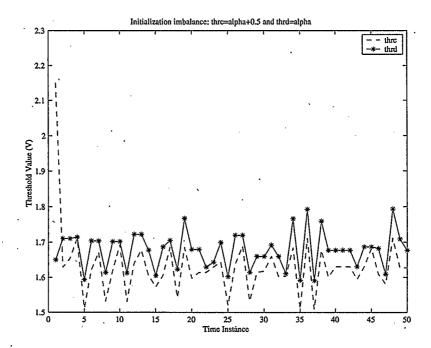

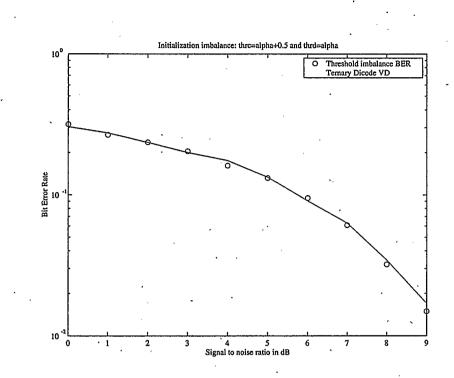

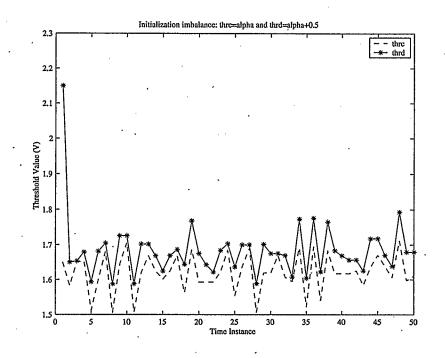

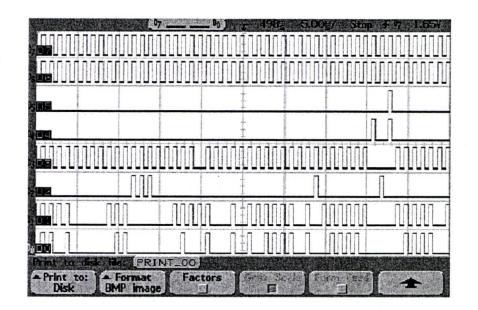

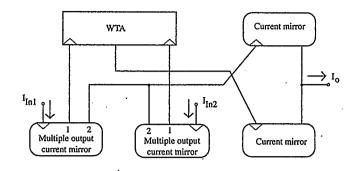

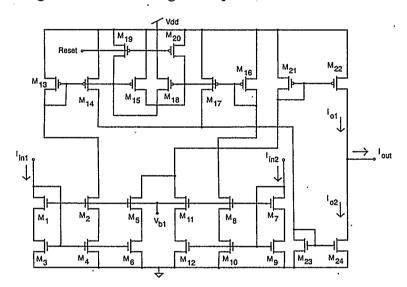

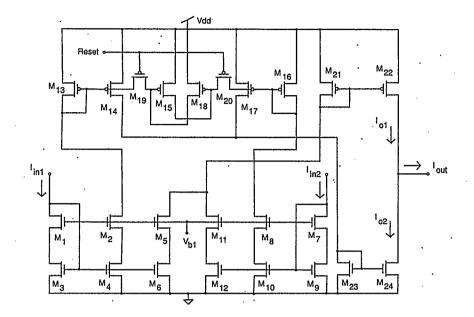

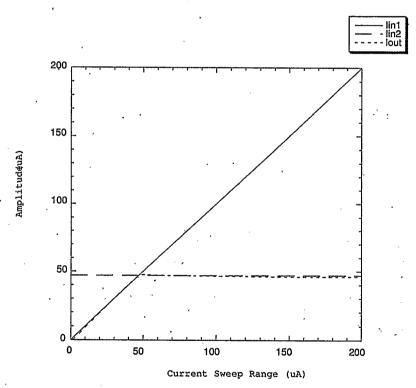

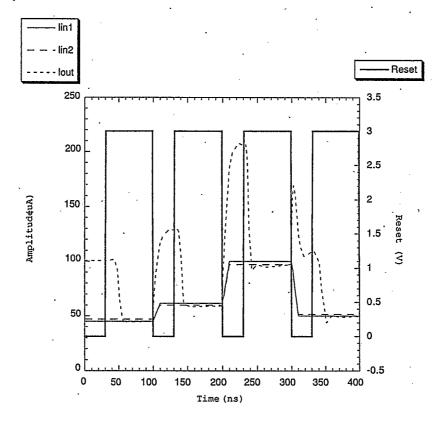

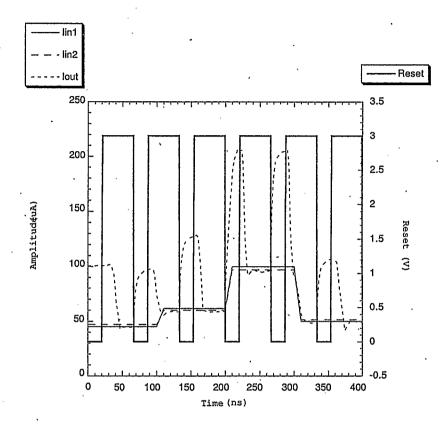

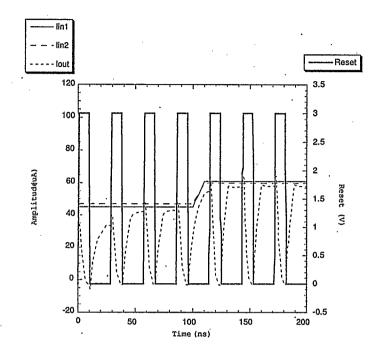

|              | C.1         | Outpu                                                                                                                                                | it Logic Combinations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |