#### https://prism.ucalgary.ca

The Vault

Open Theses and Dissertations

2013-01-25

# Force-Directed Partitioning Technique for 3D IC

# Fakheri Tabrizi, Aysa

Fakheri Tabrizi, A. (2013). Force-Directed Partitioning Technique for 3D IC (Master's thesis, University of Calgary, Canada). Retrieved from https://prism.ucalgary.ca. doi:10.11575/PRISM/26207 http://hdl.handle.net/11023/502

Downloaded from PRISM Repository, University of Calgary

#### UNIVERSITY OF CALGARY

Force-Directed Partitioning Technique for 3D IC

by

Aysa Fakheri Tabrizi

#### A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

January, 2013

© Aysa Fakheri Tabrizi 2013

## Abstract

3D IC design is one of the challenging problems of today. 3D partitioning solutions can significantly impact manufacturability and performance of a circuit. In this work, a 3D partitioning technique is developed that reduces the number of TSVs by using force directed placement technique. A circuit is partitioned into several layers and a force directed placement problem is solved to find the optimal locations of the partitions. This partitioning solution is improved by using a proposed force-based simulated annealing technique. The proposed technique is tested on ISPD04 circuits, and shows up to 20% reduction in the number of TSVs.

# Acknowledgements

I would like to express my profound gratitude to my supervisor Dr. Laleh Behjat for her invaluable guidance, infinite patience, and constant support. I would also like to show my greatest appreciation to Dr. Bill Swartz for his invaluable advices during this research. My gratitude also goes to my committee members for their insightful comments. In addition, I would like to thank all my teachers in the past for their motivations and encouragement and all the knowledge that I learned.

I would like to acknowledge the Department of Electrical and Computer Engineering wonderful staff for keeping things running smoothly.

This work would not have been possible without the support from colleagues at the lab: Dr. Logan Rakai, Amin, Bardia, Delaram, Yangyang, and Emily. Special thanks go to Dr. Logan Rakai, Amin and Bardia for constructive discussions. I would like to thank my friends in Calgary for all their support and all the fun we have had and my friends all over the world for being always beside me despite the distance. I owe special thanks to Mohammad and Benyamin for their assistance in writing this thesis. I would like to thank Mohammad for his support and keeping me encouraged during writing this thesis.

Last but not least, I would like to thank my family members, my mom and dad and my brother Arash for their unconditional love and support.

# Table of Contents

| Abs  | tract                                              |

|------|----------------------------------------------------|

| Ack  | $egin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Tabl | le of Contents                                     |

| List | of Tables                                          |

| List | of Figures                                         |

| List | of Symbols vii                                     |

| 1    | Introduction                                       |

| 1.1  | Physical Design                                    |

| 1.2  | Motivations                                        |

| 1.3  | Thesis Contributions                               |

| 1.4  | Thesis Structure                                   |

| 2    | Background                                         |

| 2.1  | Introduction                                       |

| 2.2  | Partitioning                                       |

|      | 2.2.1 Terminology                                  |

|      | 2.2.2 2D Partitioning Problem                      |

|      | 2.2.3 Kernighan Lin (KL) Algorithm                 |

|      | 2.2.4 Fiduccia-Mattheyses (FM) Algorithm           |

|      | 2.2.5 Multilevel Partitioning                      |

| 2.3  | 3D IC                                              |

|      | 2.3.1 3D partitioning                              |

|      | 2.3.2 3D Partitioning Techniques                   |

| 2.4  | Simulated Annealing (SA)                           |

| 2.5  | Force Directed Placement                           |

| 3    | Constructive 3D Partitioning                       |

| 3.1  | Introduction                                       |

| 3.2  | Problem Statement                                  |

| 3.3  | Proposed Constructive 3D Partitioning              |

|      | 3.3.1 Multilevel Partitioning                      |

|      | 3.3.2 Linear Ordering                              |

|      | 3.3.3 Layer Merging                                |

| 3.4  | Numerical Results                                  |

|      | 3.4.1 Benchmarks                                   |

|      | 3.4.2 Initial Partitioning Results                 |

|      | 3.4.3 Linear Ordering Results 6                    |

| 3.5  | Summary                                            |

| 4    | Force Based Simulated Annealing                    |

| 4.1  | Introduction                                       |

| 4.2  | Force Based Simulated Annealing 6                  |

|      | 4.2.1 Force Calculation                            |

|      | 4.2.2 Neighbor Function                            |

|      | 4.2.3 Cost Function                                |

|      | 4.2.4 Selecting SA parameters |

|------|-------------------------------|

| 4.3  | Experimental Results          |

| 4.4  | Summary                       |

| 5    | Conclusion and Future Work    |

| 5.1  | Contributions                 |

| 5.2  | Future Work                   |

| Α    | Supplementary Results         |

| Bibl | iography                      |

# List of Tables

| 2.1 | Annealing analogy                                                                                                                        | 40  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | ISPD 2004 Benchmarks                                                                                                                     | 59  |

| 3.2 | The effect of different initial partition number on net cut and run time targeting 3 tier IC                                             | 60  |

| 3.3 | The effect of different initial partition number on the net cut and run                                                                  | 00  |

| 0.0 | time targeting 4 tier IC                                                                                                                 | 61  |

| 3.4 | The effect of different initial partition number on the net cut and run                                                                  | -   |

|     | time targeting 5 tier IC                                                                                                                 | 62  |

| 3.5 | The effect of different initial partition number on the net cut on exam-                                                                 |     |

|     | ple circuit in Figure 3.5 and Figure 3.4                                                                                                 | 62  |

| 3.6 | Maximum and average number of net cuts exceeding the number of<br>net cuts obtained by using the default order in hMetis algorithm for 3 |     |

|     | tier IC                                                                                                                                  | 64  |

| 3.7 | Maximum and average number of net cuts exceeding the number of                                                                           | 0.1 |

|     | net cuts obtained by using the default order in hMetis algorithm for 4                                                                   |     |

|     | tier IC                                                                                                                                  | 64  |

| 3.8 | Maximum and average number of net cuts exceeding the number of<br>net cuts obtained by using the default order in hMetis algorithm for 5 |     |

|     | tier IC                                                                                                                                  | 65  |

| 3.9 | Best net cut number achieved                                                                                                             | 65  |

| 4.1 | Effect of force based refinement 4 tier using SA, FSA, MFSA on net cut                                                                   | 78  |

| 4.2 | Effect of force based refinement 4 tier using SA, FSA, MFSA on run                                                                       |     |

|     | time                                                                                                                                     | 78  |

| 4.3 | Effect of force based refinement 4 tier                                                                                                  | 79  |

| 4.4 | Effect of force based refinement 3 tier                                                                                                  | 79  |

| 4.5 | Effect of force based refinement 5 tier                                                                                                  | 80  |

| 4.6 | Tier area 3 Tier                                                                                                                         | 80  |

# List of Figures and Illustrations

| 2.1  | An example of a simple circuit schematic                               | 8  |  |  |

|------|------------------------------------------------------------------------|----|--|--|

| 2.2  | Hypergraph and graph representation of the circuit shown in Figure 2.1 | 10 |  |  |

| 2.3  | Netlist representation of the schematic given in Figure 2.1 10         |    |  |  |

| 2.4  | Connectivity matrix of the schematic given in Figure 2.1               | 11 |  |  |

| 2.5  | Initial partitions of an example circuit                               | 17 |  |  |

| 2.6  | Steps of KL algorithm in the first iteration for the example in Figure |    |  |  |

|      | 2.5                                                                    | 18 |  |  |

| 2.7  | Difference between the calculation of cuts in a graph, [a], and hyper- |    |  |  |

|      | graph, [b], representation of a circuit                                | 20 |  |  |

| 2.8  | An example of FM partitioning with initial partitions                  | 24 |  |  |

| 2.9  | Gain list of cells in the example                                      | 25 |  |  |

| 2.10 | Graph representing the circuit after the first move                    | 26 |  |  |

| 2.11 | Updated gain list of cells in the example                              | 27 |  |  |

|      | Graph representing the circuit after the second move                   | 27 |  |  |

| 2.13 | Updated gain list of cells in the example                              | 28 |  |  |

| 2.14 | Graph representing the circuit after the third move                    | 28 |  |  |

| 2.15 | Updated gain list of cells in the example                              | 29 |  |  |

| 2.16 | Graph representing the circuit after the fourth move                   | 29 |  |  |

| 2.17 | Updated gain list of cells in the example                              | 30 |  |  |

|      | Graph representing the circuit after the fifth move                    | 30 |  |  |

| 2.19 | Updated gain list of cells in the example                              | 31 |  |  |

| 2.20 | Graph representing the circuit after the sixth move                    | 31 |  |  |

| 2.21 | Updated gain list of cells in the example                              | 32 |  |  |

| 2.22 | Multilevel partitioning flowchart                                      | 33 |  |  |

| 2.23 | An example of a 3D circuit with TSV                                    | 34 |  |  |

| 2.24 | An example that shows how the 3D technology reduces the wire length    | 35 |  |  |

| 3.1  | The effect of stacking the partitions in proper order in reducing the  |    |  |  |

|      | number of vias                                                         | 47 |  |  |

| 3.2  | An example to show that the optimal 2D partitioning solution is not    |    |  |  |

|      | always the optimal 3D partitioning solution                            | 48 |  |  |

| 3.3  | Proposed constructive algorithm flowchart                              | 51 |  |  |

| 3.4  | The net list representation of the example circuit                     | 57 |  |  |

| 3.5  | The graph representation of the example circuit                        | 58 |  |  |

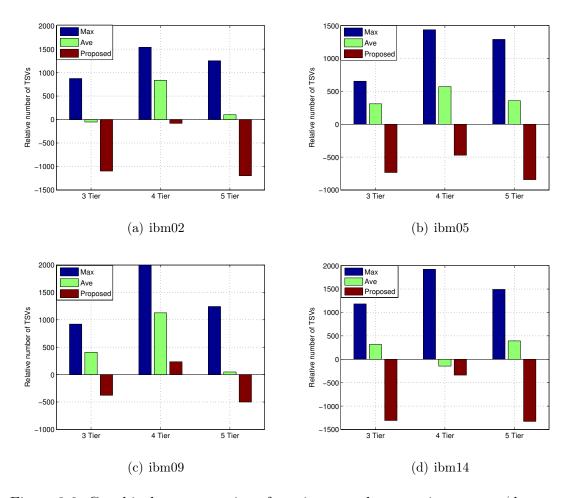

| 3.6  | Graphical representation of maximum and average increments/decrements  | 5  |  |  |

|      | in number of net cuts (the blue and the green bars respectively) and   |    |  |  |

|      | the increments/decrements in number of net cuts obtained by using the  |    |  |  |

|      | proposed order (the red bars) over the number of net cuts obtained by  |    |  |  |

|      | using the default order given by hMetis algorithm                      | 66 |  |  |

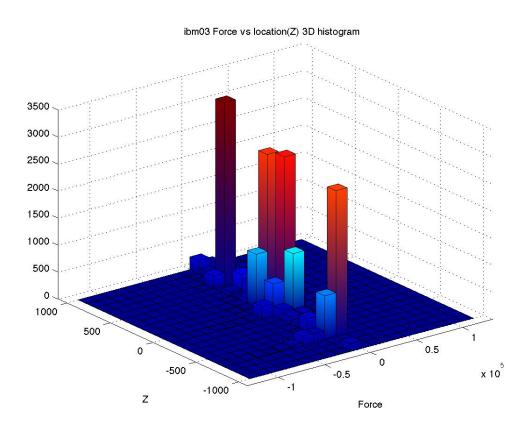

| 4.1  | Location of the cells on the z-axes and the amount of force exerted on |    |  |  |

|      | them after quadratic optimization                                      | 72 |  |  |

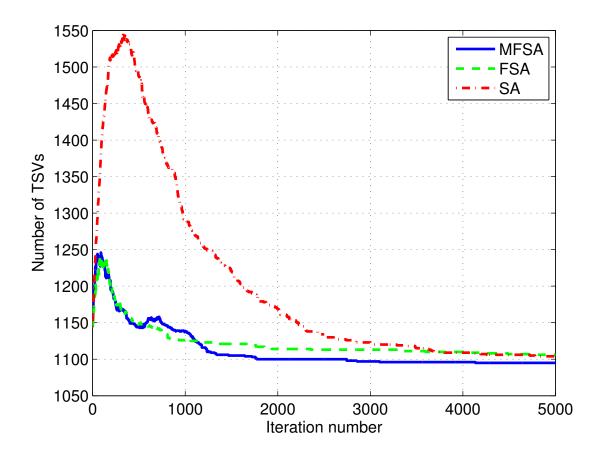

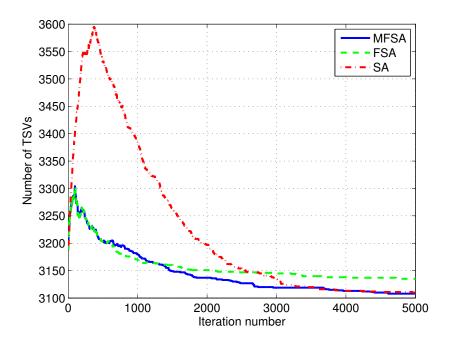

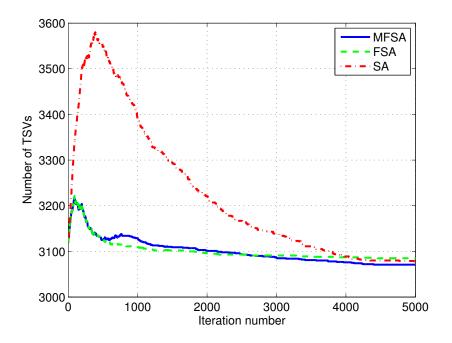

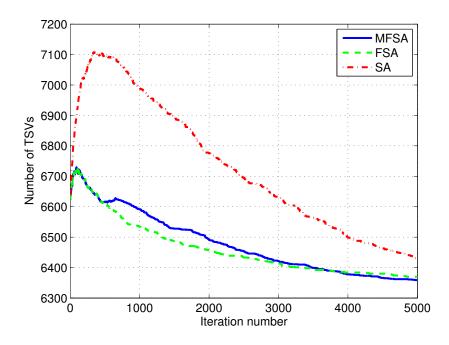

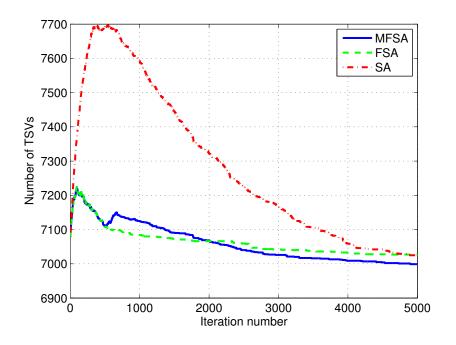

| 4.2  | Number of TSVs versus iteration number is | in S | SA, | FSA | , and | 1 N | ИF | SA | fo | r |    |

|------|-------------------------------------------|------|-----|-----|-------|-----|----|----|----|---|----|

|      | IBM02                                     |      |     |     |       |     |    |    |    |   | 81 |

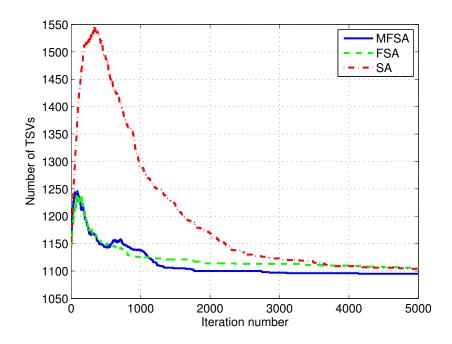

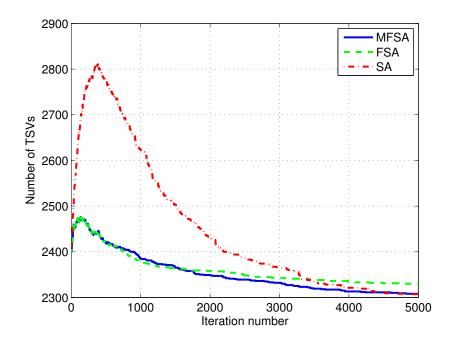

| A.1  | IBM02 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 87 |

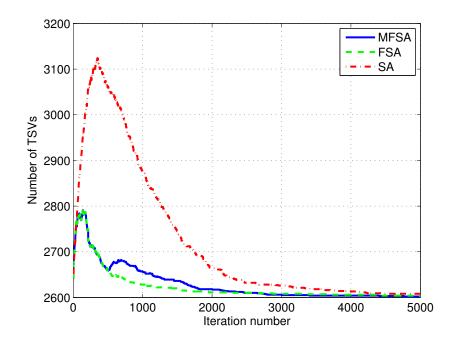

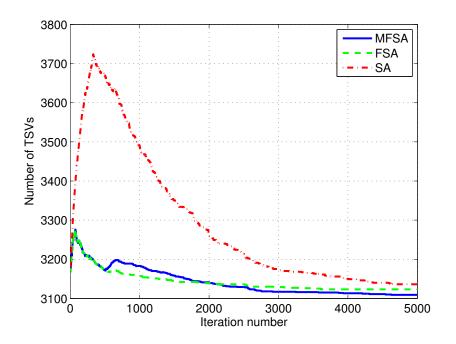

| A.2  | IBM03 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 87 |

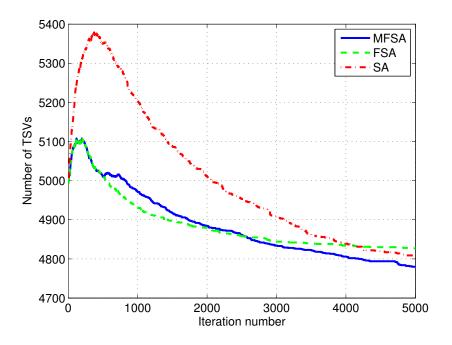

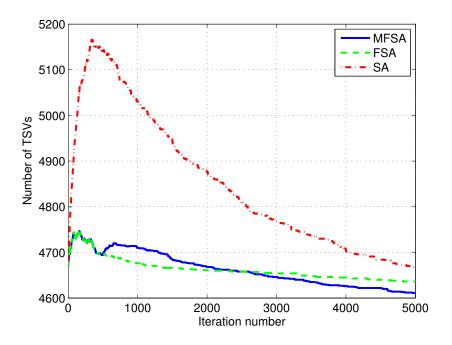

|      | IBM04 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 88 |

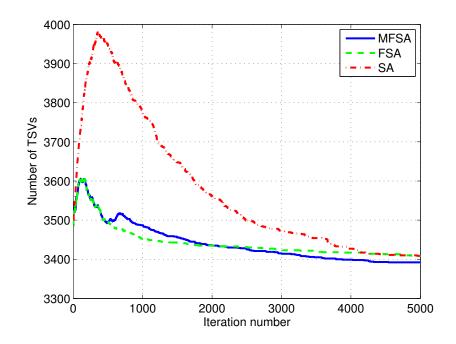

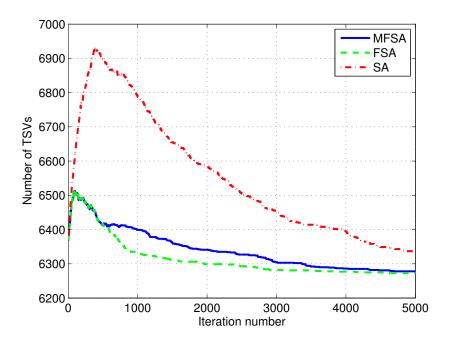

| A.4  | IBM05 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 88 |

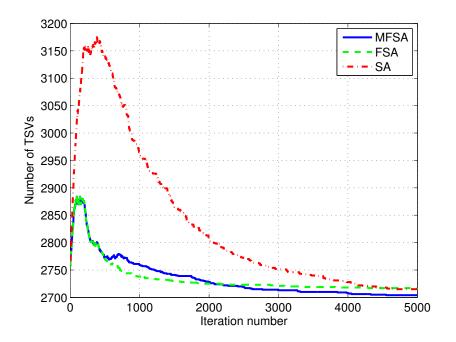

| A.5  | IBM06 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 89 |

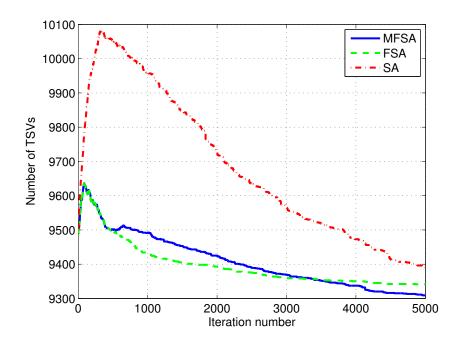

|      | IBM07 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 89 |

| A.7  | IBM09 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 90 |

| A.8  | IBM10 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 90 |

|      | IBM11 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 91 |

| A.10 | IBM12 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 91 |

|      | IBM13 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 92 |

|      | 2 IBM14 SA, FSA, and MFSA convergence     |      |     |     |       |     |    |    |    |   | 92 |

|      | B IBM15 SA, FSA, and MFSA convergence     |      |     |     |       |     |    |    |    |   | 93 |

|      | IBM16 SA, FSA, and MFSA convergence       |      |     |     |       |     |    |    |    |   | 93 |

# List of Symbols, Abbreviations and Nomenclature

Symbol Definition

1D One Dimensional

2D Two Dimensional

3D Three Dimensional

AMG Algebraic Multigrid

CAD Computer Aided Design

EC Edge Coarsening

FM Fiduccia-Mattheyses

FSA Force-based Simulated Annealing

HEC Hyperedge Coarsening

I/O Input/Output

IC Integrated Circuit

ISPD International Symposium on Physical Design

KL Kernighan-Lin

LOP Linear Ordering Problem

MFSA Modified Force-based Simulated Annealing

MHEC Modified Hyperedge Coarsening

NP-hard Non-deterministic Polynomial-time hard

SA Simulated Annealing

TPR Three Dimensional Place and Route

TSV Through Silicon Via

| Via | Vertical interconnect access |

|-----|------------------------------|

|     |                              |

VLSI Very Large Scaled Integration

## Chapter 1

## Introduction

In Very Large Scaled Integration (VLSI), millions of circuit components are integrated in a single chip. For example, Intel's Xeon X7460 released in 2008 contains more than 1.9 billion transistors [1]. As Moore predicted, in the past 50 years, the number of transistors have been increasing at exponential rates [2]. Therefore, innovative techniques had and still have to be designed to manage the complexity of the circuits. One of these techniques is to implement circuits in a Three Dimensional (3D) platform where several layers of silicon are stacked on top of each other [3, 4, 5, 6]. In this thesis, the partitioning problem for the physical design of 3D Integrated Circuits (ICs) is considered.

The rest of this chapter is organized as follows: In Section 1.1, the main stages of physical design are explained. In Section 1.2, the motivations of the thesis are discussed. Thesis contributions are briefly presented in Section 1.3. Finally, the organization of the thesis is described in Section 1.4.

### 1.1 Physical Design

Physical design is one of the main steps in IC design where the physical properties such as the exact locations of components and wires of the circuit are determined. Physical design includes several major stages: partitioning, floor planning, placement and routing [7, 8, 9, 10].

In the partitioning stage, the circuit is divided into several partitions that are relatively independent, i.e. as few wires as possible connect them. These partitions then can be designed individually or in parallel. As partitioning is the focus of this thesis, a more comprehensive introduction of this stage is presented in Chapter 2.

The arrangement of the partitions and their dimensions are determined in floor planning step. In the placement stage, the exact locations of the circuit components are determined. The main objective of placement is minimizing the total wire length while ensuring routability. Placement usually takes place in two phases: global placement and detailed placement. In global placement the approximate locations of the cells are determined. In this stage cells are allowed to overlap. In detailed placement, the exact locations to the cells are obtained and any overlaps are removed. Once all cell locations are determined, the paths for all of the wires of the circuit are determined in the routing stage.

#### 1.2 Motivations

3D design has become a viable solution to reduce wire length and enhance integration in circuits [11, 12, 13, 14]. One of the biggest issues to be addressed during 3D IC integration is the communication between tiers using Through-Silicon Vias (TSVs). Minimizing the total number of TSVs is of upmost importance, as they are expensive, bulky and unreliable [15].

One of the most effective ways to reduce the number of TSVs is to use partitioning. Partitioning of Two Dimensional (2D) circuits is a well developed field and is usually performed by multi-level algorithms such as hMetis [16, 17]. However, 2D partitioning techniques do not consider the number of times a net is cut, where net refers to the interconnection between circuit elements, or how many partitions exist between the end points of a net. In a 3D circuit, partitions are stacked and any connection between two non-adjacent partitions results in using more than one TSV. For example, considering a 3D IC with 5 tiers, if a terminal of a net is placed in the top tier and another terminal in the bottom tier, the net is effectively cut 4 times and 4 TSVs are required to complete one single connection. Therefor, during 3D partitioning a designer has two main optimization criteria: reduce the number of nets between partitions, and determine the optimal locations of tiers. In this thesis it is proposed to consider floor planning during 3D partitioning to reduce the number of TSVs and obtain better integration for 3D ICs.

Another motivation of this thesis is to show that different heuristics should be used for different situations to obtain best results. For example, multilevel partitioning techniques are very effective in finding a good partitioning solution in a small amount of time, however, they do not give any indication on where partitions should be placed or how and in which direction cells have to move in order to further improve their results. Therefore, it is proposed to combine a multilevel technique with other techniques such as force directed placement and simulated annealing to obtain best results. In other words, in this thesis it is proposed to use different partitioning techniques in different stages of the design in order to harness the strengths of each method.

#### 1.3 Thesis Contributions

In this work different optimization methods are combined to perform the 3D IC partitioning. These methods are used in different stages of IC physical design such as 2D partitioning, floor planning, and placement. Since these methods are developed targeting different applications they are not suitable for 3D IC partitioning in their current state. The main contributions of this thesis are as follows:

- Development of the a force directed partitioning technique.

- Development of force-based simulated annealing technique.

- Up to 20% reduction in the number of interconnections between Tiers.

A brief description of these contributions is given in the following.

#### Development of the a force directed partitioning technique:

In this thesis it is proposed to use state-of-the-art technique for 2D circuit partitioning which minimizes the number of connections between all partitions. However in a 3D IC, objective function is different from that of 2D IC and the goal is to minimize the number of vias between partitions that are stacked on one dimension. In this thesis, it is proposed to use a one dimensional placement to find a suitable ordering for the partitions. Ordering the initial partitions results in locating the partitions that have more connections close to each other and consequently reduce the length of connections and number of long connections.

#### Development of force-directed simulated annealing technique:

After the initial 3D partitioning solution is obtained an iterative improvement technique can be used to improve the results. Simulated Annealing (SA) [18] is shown to be effective to improve the partitioning solutions. In original SA, the cells to be moved and the direction of their move between the partitions are selected randomly. In this thesis, a variation is proposed to SA where random moves are replaced with moves that are directed by forces applied to cells. This method is combined with other methods in solving the particular 3D IC partitioning problem; however, it can be used in many other optimization problems. Unlike the original SA in which the current solution is replaced by a random neighbor solution, in the developed FSA, the selection of the new solution is probabilistic, i.e., not only the acceptance of a move, but also selecting the new solution is based on a probability. This probability of selection is based on the system information. In 3D partitioning problem this information is proposed to be the forces that connected cells impose on each other. Finally, numerical results on benchmarks released by IBM show that the proposed techniques outperform the existing 3D partitioning solutions for most cases.

#### 1.4 Thesis Structure

This thesis is structured as follows:

- Chapter 2: In this chapter the background for partitioning, forcedirected placement, simulated annealing and 3D IC design are given.

- Chapter 3: In this chapter one of the main contributions of this thesis, combining of several partitioning and floor planning techniques to

obtain better 3D partitions, is given. In addition, the experimental results of the 3D partitioning are given.

- Chapter 4: In this chapter, a novel force-directed iterative improvement technique is introduced to further improve the partitioning solution based on the tier location of the cells. In addition, experimental results obtained for 3D partitioning are given and compared with other 3D partitioning techniques.

- Chapter 5: Finally, a summary of the contributions of the thesis and future work are given in this chapter.

## Chapter 2

# Background

#### 2.1 Introduction

This chapter provides background on circuit partitioning and 3D ICs. Moreover, the techniques used in this thesis, simulated annealing and force directed placement, are reviewed.

This chapter is organized as follows: In Section 2.2, the partitioning problem is defined and existing partitioning algorithms are identified. Then, 3D IC, 3D IC partitioning problem and the existing 3D IC partitioning techniques are presented in Section 2.3. In Section 2.4, SA meta-heuristic is described. In Section 2.5, the force directed placement method is reviewed.

### 2.2 Partitioning

The modern integrated circuits consist of millions of transistors [15]. Due to this large and ever increasing scale of modern circuits, the design of such circuits has become a complex task. A common strategy to handle the complexity and to perform a computationally feasible design is to implement a divide and conquer strategy where circuits are partitioned into smaller sub-circuits which can be designed independently. Because of the large number of transistors, it is very difficult to make a full-chip layout. Hence, it is required to divide the circuit into smaller sub-circuits which can

be designed individually or in parallel. The procedure of dividing a circuit into smaller sub-circuits is called partitioning.

The wires that connect two different sub-circuits can be much more costly than those that are confined to a single sub-circuit. Moreover, as the design of each sub-circuit is done independently and without considering the other partitions in most cases, it is desired to generate partitions as independently as possible. Therefore, minimizing the connections between two sub-circuits is of great significance.

#### 2.2.1 Terminology

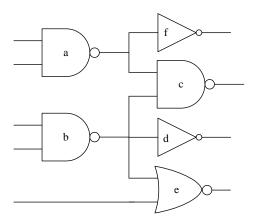

A circuit is a collection of logic elements, referred to in this thesis as cells, that are connected to each other. The connection between the cells are called nets. Figure 2.1 illustrates a simple circuit schematic. There are also contact points that connect some cells to the outside of a circuit. These contact points are called Input/Output Pins (I/O Pins).

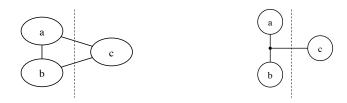

Figure 2.1: An example of a simple circuit schematic

Connectivity information of cells can be represented in different ways such as hypergraph/graph representation, netlist representation and connectivity matrix [7].

Each one of the representations is described in further detail here.

#### Hypergraph/Graph representation

A circuit can be represented by a graph G(V, E) where V is the set of vertices or nodes that includes the cells and set E represents the set of edges that are the connection between cells, i.e. nets [19].

In the graph representation each edge connects to only two cells. Since in practical circuit design, there are lots of nets that are connected to more than two cells, a graph representation is not an adequate representation of a circuit and hypergraph representation is mostly used. A hypergraph is generalization of graph in which one edge can connect two or more than two vertices. The nets that connect more than two cells are called hyperedges [19].

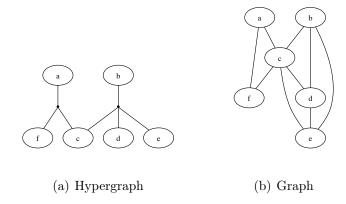

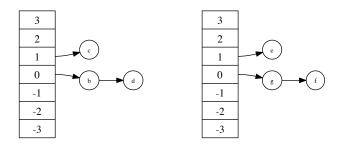

In Figure 2.2, a hypergraph representation of the circuit with five cells, shown in Figure 2.1, and its corresponding graph representation are shown. In this figure vertices a to e represent the logic elements a to e shown in Figure 2.1 and the the edges represent the connection between logic elements. In this example, in converting a hypergraph to a graph, all hyperedges are converted to a set of edges that connect each pair of the nodes connected to a given hyperedge.

A multigraph is a graph that can have more than one edge between a pair of nodes. A multigraph can be used to represent the nets with different weights. The weight, w(e), for an edge,  $e \in E$ , represents the weight of the corresponding edge. Finally, in a circuit, each logic element has a certain area. In this thesis, area(v), for each  $v \in V$  represents the area of each cell.

Figure 2.2: Hypergraph and graph representation of the circuit shown in Figure 2.1

#### Netlist representation

A netlist contains the names of the nets followed by the names of all the cells that are connected to a given net. An example of a netlist representation of the circuit shown in Figure 2.1 is given in Figure 2.3.

node: 6

nets: 2

net 0: a f c

net 1: b c d

Figure 2.3: Netlist representation of the schematic given in Figure 2.1

#### Connectivity matrix

A connectivity matrix, C, is an  $n \times n$  symmetric matrix where n is equal to the number of all cells including the I/Os. The value of element C(i,j),  $i \neq j$  is equal to the weight of the connection between cells i and j. Element C(i,j),  $i \neq j$  of C is zero if cell i is not connected to cell j and non-zero otherwise. The diagonal elements of the matrix are equal to the sum of the weights of the nets that are connected to

the cell. Note that the connectivity matrix doesn't show the information of nets i.e. which cells are connected to a particular net. An example of a connectivity matrix for the schematic of Figure 2.1 is shown in Figure 2.4.

$$\mathbf{C} = \begin{bmatrix} a & b & c & d & e & f \\ a & \begin{bmatrix} 2 & 0 & 1 & 0 & 0 & 1 \\ 0 & 3 & 1 & 1 & 1 & 0 \\ 1 & 1 & 5 & 1 & 1 & 1 \\ 0 & 1 & 1 & 3 & 1 & 0 \\ e & & & & & & & & \\ f & & & & & & & & \\ \end{bmatrix}$$

Figure 2.4: Connectivity matrix of the schematic given in Figure 2.1

#### 2.2.2 2D Partitioning Problem

The k-way partitioning divides a circuit into k partitions and is a combinatorial optimization problem<sup>1</sup>where the goal is to divide a circuit into several partitions that have as few wires as possible connecting them [8].

The first goal of partitioning is to divide the circuit in a way that the number of connections between the sub-circuits is minimized. The constraint of the problem is normally to keep balance between the size of the partitions, or in other worlds it is desired to produce partitions that are roughly from the same sizes. The mathematical formulation can be stated as [8, 9]:

$$\begin{split} & \min \quad \sum_{e \in \Phi} w(e), \\ & s.t. \quad \sum_{v \in V_i} area(v) \leq \frac{1}{k} \sum_{v \in V} area(v) = \frac{1}{k} area(V), \end{split}$$

<sup>&</sup>lt;sup>1</sup>A combinatorial optimization problem is a problem of finding the optimal solution from the finite number of possible solutions [20].

where  $\Phi$  denotes the set of cut edges and w(e) is the weight of each cut edge.  $V_i \subseteq V, i=1,...,k$  and k is the number of partitions. Since partitioning is an Non-deterministic Polynomial-time hard (NP-hard) problem [8], no deterministic algorithm is known which can find the optimal solution in polynomial time. However, several heuristics [21, 22, 23, 24] such as Kernighan-Lin (KL) algorithm [25] and Fidducia-Mattheyses (FM) algorithm [26] are developed that can improve the quality of a given partition. These algorithms are described in detail in the following sections. In these algorithms the partitioning problem is formulated as a graph partitioning problem. The vertices of the graph represent the circuit's nodes and the edges represent the interconnections between the cells or the nets.

With the increase in the number of circuit element, partitioning of 2D circuits is now performed by multi-level hypergraph partitioning algorithms such as hMetis [27, 17]. These multi-level algorithms on their own are based on iterative improvement techniques such as FM [26].

#### 2.2.3 Kernighan Lin (KL) Algorithm

Kernighan-Lin heuristic, proposed by B. W. Kernighan and S. Lin in 1970, is one of the earliest works in solving the partitioning problem [25]. The original algorithm was developed to perform 2-way partitioning where the cell areas are equal. KL algorithm divides a graph G(V, E) with |V| = 2n nodes to two sets with n nodes in a way that the two sets have the minimum number of connections with each other.

In KL an initial partitioning solution is improved by swapping two nodes from different partitions. The algorithm selects the pair of nodes that their exchange results in highest net cut reduction.

KL is an iterative algorithm. The first iteration starts with arbitrary initial partitions i.e. the nodes are divided to two equal size sets A and B where each set consists of n nodes. Then a pair of nodes from different partitions with maximum gain is selected and swapped. Once the nodes are swapped, they are fixed and are not allowed to be selected for other swaps until all nodes are fixed. After every swap the gains of free nodes are updated and the pair selection and the procedure is repeated until all nodes are fixed. At this point all nodes become free and the algorithm starts the next iteration and the pair swapping is repeated. The algorithm terminates if no improvement can be made during a given iteration.

The algorithm is described step by step after gain calculation and related concepts are presented. To calculate the gain of a pair of nodes, first the cost of moving a node is calculated. The following equation shows the cost of moving a node that belongs to partition A to the partition B:

$$D(v) = |E_{AB}(v)| - |E_A(v)|, \tag{2.1}$$

where  $E_{AB}(v)$  is the set of edges connected to node v that also has nodes in partition B and  $E_A(v)$  is the set of edges connected to v that only has nodes in partition A. In other words,  $E_{AB}(v)$  are the set of edges connected to node v that are cut by cut line and  $E_A(v)$  are the set of edges that are not cut by the cut line. The value of D(v) can be positive or negative. The high D(v) value indicates that the benefit of moving node v is high.

The gain of swapping two nodes from different partitions is calculated by adding

the cost of the move of each node and twice subtracting the connection weight between the pair. Notice that subtracting the connection weight between the nodes is necessary because the cost of each node is calculated with the assumption of not moving the other node. So the connected edge that was cut before the swap is counted in both cost calculations as moving only one node changes the status of the given edge to uncut, where it remains cut by swapping the pair. The gain of the  $x^{th}$  swap in a given iteration  $g_x(i,j)$ , is calculated by:

$$g_x(i,j) = D(i) + D(j) - 2C(i,j),$$

(2.2)

where D(i) and D(j) are the cost of moving node i and j respectively and C(i,j) is the connectivity weight between node i and node j.

The value of gain shows the reduction in cut size when the given pair is swapped. A positive gain indicates that the swap improves the quality of partitioning and a negative gain means the swap increases the cut size and lowers the quality of partitions.  $G_x$  is the cumulative gain that is calculated after each swap in a given iteration.

$$G_x = \sum_{i=1}^{x} g_i$$

$$G_m = max(G_x)$$

The swap with maximum  $G_x$  indicates that the partitioned graph after performing the given swap has the highest quality among all configurations of iteration. Therefore the moves are only applied up to swap number m. Notice that all the moves that are found until all the nodes are fixed were in order to find  $G_m$  and the swaps are only applied up to swap number m.

#### KL Algorithm Description

The KL partitioning algorithm (Algorithm 1) starts with dividing the graph to two random equal size initial partitions (line 1-2).  $G_m$  gets the initial value of  $\infty$  and iteration number is set to 1 (line 3-4). During each iteration, while  $G_m$  is greater than zero (line 5) all the nodes are set as free and the cost of all nodes are calculated (line 6-9). x is set to 1 to indicate the first swap (line 10). While there exist free nodes in the graph (line 11) the gain of swapping each pair of free nodes are calculated and the pair with maximum gain is swapped and fixed (line 12-18). The cumulative gain is calculated (line 19) and the cost of free nodes that are connected to swapped nodes are updated (line 20-22). The algorithm moves to next swap of the iteration (line 23). When all the nodes are fixed (line 24) the swap number with maximum cumulative gain is determined (line 25) and swaps up to a determined swap number are confirmed (line 26-28). The algorithm goes to next iteration if  $G_m$  is greater than zero (line 29-30) and terminates otherwise (line 31).

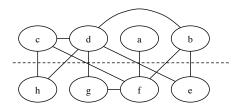

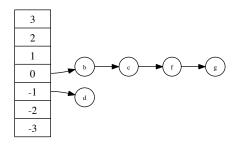

Example 2.2.1 An example of a given circuit represented as a graph and the initial partitions are shown in Figure 2.5. In this figure, nodes a to e represent the cells and edges of the graph represent the nets between the cells. The dashed line divides circuit into two initial partitions. The initial cut size is 8. The cost and the gain of each node can be calculated as follows:

$$D(a) = 1 - 0 = 1$$

,  $D(b) = 2 - 1 = 1$ ,  $D(c) = 2 - 1 = 1$ ,  $D(d) = 3 - 2 = 1$

$D(e) = 1 - 1 = 0$ ,  $D(f) = 3 - 1 = 2$ ,  $D(g) = 1 - 1 = 0$ ,  $D(h) = 2 - 0 = 2$

$g_1(a, h) = 1 + 2 - 2 \times 0 = 3$

#### Algorithm 1 KL partitioning Algorithm

31: **End**.

**Input:** Graph G(V, E)**Output:** Partitioned graph G(V, E)1: Begin 2:  $A, B \leftarrow$  random initial partitions 3:  $G_m \leftarrow \infty$  $4:\ iteration \leftarrow 1$ 5: while  $G_m > 0$  do for all  $v \in V$  do 6: 7:  $S(v) \leftarrow free$ Compute D(v)8: 9: end for  $x \leftarrow 1$ 10: while there are free nodes do 11: for all  $i \in A, S(i) = free do$ 12: for all  $j \in B, S(j) = free do$ 13:  $g_x(i,j) \leftarrow \text{gain of swapping } i \text{ and } j$ 14: end for 15: end for 16: swap a,b with  $max(g_x)$ 17:  $S(a), S(b) \leftarrow fixed$ 18: Compute  $G_x$ 19: 20: for all free v connected to a or b do 21: Update D(v)end for 22:  $x \leftarrow x + 1$ 23: end while 24:  $G_m = max(G_x)$ 25: if  $G_m > 0$  then 26: 27: Confirm swaps x = 1, ..., mend if 28: 29:  $iteration \leftarrow iteration + 1$ 30: end while

Figure 2.5: Initial partitions of an example circuit

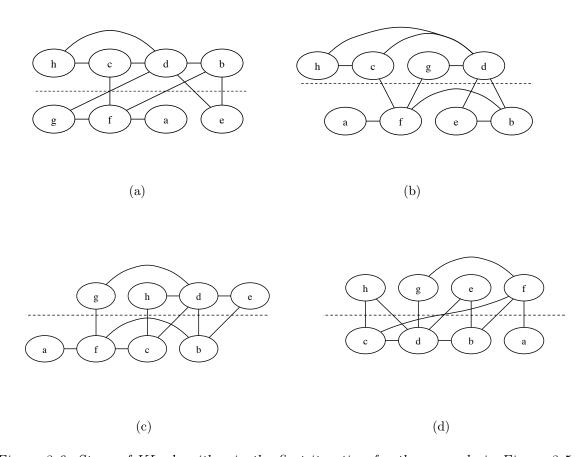

The maximum gain belongs to a and h. Nodes a and h are swapped and fixed and is shown in Figure 2.6(a). D(v) is updated for all free nodes that are connected to swapped nodes, a and h, which are c, d, and f.

$$D(c) = 1 - 2 = -1$$

,  $D(d) = 2 - 3 = -1$ ,  $D(f) = 2 - 2 = 0$

$g_2(b, g) = 1 + 0 - 2 \times 0 = 1$

Nodes b and g are swapped and fixed shown in Figure 2.6(b).

D(v) is updated for all free nodes that are connected to swapped nodes b and g which are d, e, and f.

$$D(d) = 2 - 3 = -1, D(e) = 1 - 1 = 0, D(f) = 2 - 2 = 0$$

$g_3(c, e) = -1 + 0 - 2 \times 0 = -1$

Nodes c and e are swapped and fixed.

D(v) is updated for all free nodes that are connected to swapped nodes c and e which are d, and f.

$$D(d) = 2 - 3 = -1, D(f) = 2 - 2 = 0$$

$g_4(d, f) = -1 + 0 - 2 \times 0 = -1$

Figure 2.6: Steps of KL algorithm in the first iteration for the example in Figure 2.5

Nodes d and f are swapped and fixed.

Cumulative gain is computed.

$$G_1 = g_1 = 3$$

$G_2 = g_1 + g_2 = 4$

$G_3 = g_1 + g_2 + g_3 = 3$

$G_4 = g_1 + g_2 + g_3 + g_4 = 2$

The maximum positive cumulative gain  $G_m$  is equal to 4 with m=2. Therefore the first 2 swaps are performed and the algorithm goes to next iteration (Figure 2.6(b)). The cut size is reduced to 4 from 8 in first iteration.

#### 2.2.4 Fiduccia-Mattheyses (FM) Algorithm

Feduccia-Mattheyeses is a partitioning heuristic introduced by Feduccia and Mattheyeses in 1982 [26]. FM divides the graph G(V, E) into partitions so as minimize the total cut nets.

Unlike KL that swaps a pair of cells between two partitions, FM moves cells independently which makes the algorithm more flexible in solving unequal partition sizes. Another advantage of FM over KL is that hypergraphs can be used in FM. While KL minimizes the number of edges, FM minimizes the number of nets cut. That means if one net is connected to more than two cells and the net is cut, KL might count the cut more than once, while FM counts that only once which is practical. Figure 2.7 shows the shortcoming of partitioning methods using graph representation vs. hypergraph representation. Another advantage of FM is that it is applicable on

graphs with different node areas.

- (a) Grapph representation

- (b) Hypergraph representation

Figure 2.7: Difference between the calculation of cuts in a graph, [a], and hypergraph, [b], representation of a circuit

#### Definitions used in FM

Cut - a net is cut if it has cells in more than one partition.

Uncut - a net is uncut if all its connected cells are located in one partition.

Gain - gain of a cell is the change in the number of cuts when cell is moved to other partition. The gain is defined as

$$q(v) = FS(v) - TE(v)$$

where FS(v) is the number of cut nets that are only connected to v in v's partition. TE(v) are the nets, connected to v, that all their other cells are in v's partition i.e. the uncut nets that are connected to v.

There are 3 type of nets connected to a node v. The first type is the nets that are cut and have other cells connected in the same partition that v is located. Moving v to the other partition doesn't affect the state of these kind of nets i.e. they remain cut. The second types are the nets that are cut and are only connected to v in v's

partition. Moving v to the other partition changes the state of these nets to uncut, since all their connected cells are in the partition that v is moved to. These are the nets that are counted in calculating FS(v). The third type of nets are the nets that are uncut. So moving cell v to the other partition changes the state of these nets to cut. These are the nets that are counted in calculating TE(v).

Cumulative gain -  $G_s$  is the cumulative gain after  $s^{\text{th}}$  move in an iteration. As in KL, after each move in an iteration, the cumulative gain is calculated and at the end of the iteration the maximum cumulative gain  $G_m$  and its corresponding move number m is determined. Then, the moves are performed up to  $m^{\text{th}}$  move.

$$G_s = \sum_{i=1}^{s} g_i$$

$$(G_m, m) = (max(G_s), s)$$

Critical nets - A critical net is a net that is either uncut or has exactly one cell in one partition and the rest of its cells in the other partition. These are the only nets that moving their connected cells might change their state from cut to uncut or vice versa.

Critical cells - Critical cells are the cells that are connected to the critical nets.

Ratio factor- The ratio factor is a parameter that shows the relation of the size of a partition to the size of graph.

$$r = \frac{|A|}{|A| + |B|}$$

where |A| and |B| are the sizes of the partition A and B respectively i.e. the total

respective area of the all cells in partition A and partition B and

$$|A| + |B| = |V|,$$

where, V is the total area of all cells.

To set the balance criterion the size of the largest node must be considered. The partitioning is balanced if

$$r.|V| - |v|_{max} \le |A| \le r.|V| + |v|_{max},$$

where,  $|v|_{max}$  is the size of the largest node in graph.

#### FM Algorithm description

The Algorithm 2 presents the pseudocode for FM algorithm. FM starts with computing the balance criterion (line 1-2) and arbitrarily divides the graph into two subgraphs or partitions (line 3). The value of  $G_m$  is set to  $\infty$  and the first iteration starts (line 4-5). All the nodes are set as free and FS, TE, and g are calculated for all (line 7-13). A free cell that maximizes gain while satisfying the balance criterion is selected, moved to the opposite partition and fixed, then the track of moved cell is kept (line 15-19). The criticalnets and criticalcells connected to the moved cell are determined (line 20-21). The gain is updated for the critical cells that are connected to the moved cell i.e. the cells that are connected to the moved cell by critical nets (line 22-26). The cumulative gain is calculated (line 27). Then algorithm continues to the next move (line 28). When all the nodes are fixed (line 29) the move number with maximum cumulative gain is determined (line 30) and moves up to the determined move number are confirmed (line 31-33). The algorithm goes to next iteration if  $G_m$  is greater than zero (line 34-35) and terminates otherwise (line 36).

#### Algorithm 2 FM partitioning Algorithm

Input: Graph G(V, E)Output: Partitioned graph G(V, E)

```

1: Begin

2: Balance criterion

3: initial partition

4: G_m \leftarrow \infty

5: iteration \leftarrow 1

6: while G_m > 0 do

G_s \leftarrow 0

7:

8:

for all v \in V do

S(v) \leftarrow free

9:

FS(v) \leftarrow number of nets connected to v and cut

10:

TE(v) \leftarrow number of nets connected to v but not cut

11:

g_x(i,j) \leftarrow FS(v) - TE(v)

12:

end for

13:

x \leftarrow 1

14:

while there are free nodes do

15:

a \leftarrow \text{cell} with max gain

16:

order \leftarrow \{order, a\}

17:

move a to opposite partition

18:

S(a) \leftarrow fixed

19:

criticalnets \leftarrow \text{nets connected to } a

20:

critical cells \leftarrow cells connected to <math>critical nets

21:

for all c \in critical cells connected to a do

22:

if then S(c) == free

23:

Update g_x(c)

24:

end if

25:

end for

26:

G_s \leftarrow G_s + g_x(a)

27:

x \leftarrow x + 1

28:

end while

29:

30:

G_m = max(G_s)

if G_m > 0 then

31:

Confirm swaps order(1:m)

32:

end if

33:

iteration \leftarrow iteration + 1

34:

35: end while

36: End.

```

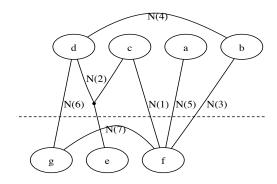

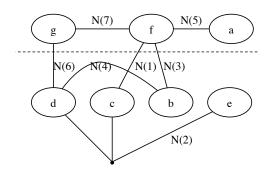

**Example 2.2.2** The weighted cells and the nets of a circuit and the ratio factor for partitioning are given. The initial partitions are as shown in Figure 2.8.

Figure 2.8: An example of FM partitioning with initial partitions

Cell areas:

$$area(a) = 4, \ area(b) = 2, \ area(c) = 2, \ area(d) = 5,$$

$area(e) = 1, \ area(f) = 5, \ area(g) = 3.$

The nets are as follows:

$$N(1) = (c, f), N(2) = (c, d, e), N(3) = (b, f),$$

$N(4) = (b, d), N(5) = (a, f), N(6) = (d, g).$

And the balance factor is r = 0.4. Tie breaking rule: alphabetical order. Perform the

first iteration of FM algorithm. Balance criterion can be calculated as follows:

$$\begin{split} r.|V| - |v|_{max} &\leq |A| \leq r.|V| + |v|_{max} \\ r.|V| - |v|_{max} &= 0.4 \cdot 22 - 5 = 3.8 \\ r.|V| - |v|_{max} &= 0.4 \cdot 22 + 5 = 13.8 \\ 3.8 &\leq |A| \leq 13.8 \end{split}$$

Initial partition sizes: |A| = 13, |B| = 9

$$FS(a) = 1, TE(a) = 0, g_1(a) = 1$$

$FS(b) = 1, TE(b) = 1, g_1(b) = 0$

$FS(c) = 1, TE(c) = 0, g_1(c) = 1$

$FS(d) = 1, TE(d) = 1, g_1(d) = 0$

$FS(e) = 1, TE(e) = 0, g_1(e) = 1$

$FS(f) = 3, TE(f) = 1, g_1(f) = 2$

$FS(g) = 1, TE(g) = 1, g_1(g) = 0$

Figure 2.9: Gain list of cells in the example

The best gain is 2 which can be obtained by moving f.

Balance criterion after moving f is |A| = 18, |B| = 4 which doesn't satisfy the balance criterion. The next maximum gain is selected. Possible cells are a, c, and e with the gain of 1.

Balance criterion after moving a is |A| = 9, |B| = 13

Balance criterion after moving c is |A| = 11, |B| = 11

Balance criterion after moving e is |A| = 14, |B| = 8

All three moves satisfy the balance criterion, the a is selected based on alphabetical order.

Now the critical nets connected to a and the corresponding critical cells are determined and the gain of critical cells are updated.

$$g_1 = 1$$

criticalnets connected to a: N(5)

critical cells: f

Figure 2.10: Graph representing the circuit after the first move

The best gain is 1 which can be obtained by moving c or e.

Balance criterion after moving c is |A| = 7, |B| = 15

Figure 2.11: Updated gain list of cells in the example

Balance criterion after moving e is |A| = 10, |B| = 12

Moving c doesn't satisfy the balance criterion and cell e is selected to move.

$$g_2 = 1$$

criticalnets connected to e: N(6)

$critical cells \colon c,d$

Figure 2.12: Graph representing the circuit after the second move

The best gain is 0 which can be obtained by moving b, c, f, or g.

Balance criterion after moving b is |A| = 8, |B| = 14

Balance criterion after moving c is |A| = 8, |B| = 14

Balance criterion after moving f is |A| = 15, |B| = 7

Balance criterion after moving g is |A| = 13, |B| = 9

Figure 2.13: Updated gain list of cells in the example

Only moving g satisfies the balance criterion, so cell g is selected to move.

$g_3 = 0$

criticalnets connected to g: N(6), N(7)

critical cells: d, f

Figure 2.14: Graph representing the circuit after the third move

The best gain is 2 which can be obtained by moving f; however it doesn't satisfy the balance criterion. and b with the next best gain of 0 is selected.

Balance criterion after moving b is |A| = 11, |B| = 11

Figure 2.15: Updated gain list of cells in the example

$g_4 = 0$

$critical nets \ connected \ to \ b: \ N(3), N(4)$

critical cells: d, f

Figure 2.16: Graph representing the circuit after the fourth move

The next cell to be moved is c with the gain of 0 and satisfying the balance criterion.

Balance criterion after moving c is |A|=9, |B|=13

$g_5 = 0$

$critical nets \ connected \ to \ c: \ N(1), N(2)$

Figure 2.17: Updated gain list of cells in the example

critical cells: f, d

Figure 2.18: Graph representing the circuit after the fifth move

The best gain belongs to d however it doesn't satisfy the balance criterion. Therefore, f is moved.

Balance criterion after moving f is |A|=14, |B|=8

$g_6 = -2$

$critical nets\ connected\ to\ c\colon\thinspace N(1),N(3),N(5),N(7)$

No criticalcells.

Figure 2.19: Updated gain list of cells in the example

Figure 2.20: Graph representing the circuit after the sixth move

Cell e is moved.

$$g_7 = 0$$

In order to find the best move sequence the cumulative gains are calculated.

$$G_1 = g_1 = 1$$

$$G_2 = g_1 + g_2 = 1 + 1 = 2$$

$$G_3 = g_1 + g_2 + g_3 = 1 + 1 + 0 = 2$$

$$G_4 = g_1 + g_2 + g_3 + g_4 = 1 + 1 + 0 + 0 = 2$$

$$G_5 = g_1 + g_2 + g_3 + g_4 + g_5 = 1 + 1 + 0 + 0 + 0 = 2$$

Figure 2.21: Updated gain list of cells in the example

$$G_6 = g_1 + g_2 + g_3 + g_4 + g_5 + g_6 = 1 + 1 + 0 + 0 + 0 + (-2) = 0$$

$$G_7 = g_1 + g_2 + g_3 + g_4 + g_5 + g_6 + g_7 = 1 + 1 + 0 + 0 + 0 + (-2) + 0 = 0$$

### 2.2.5 Multilevel Partitioning

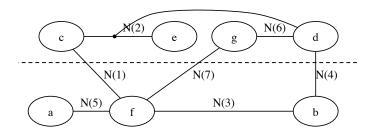

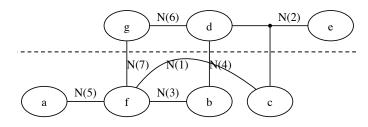

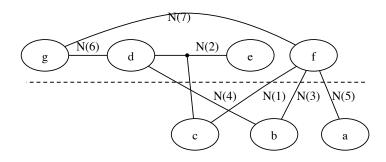

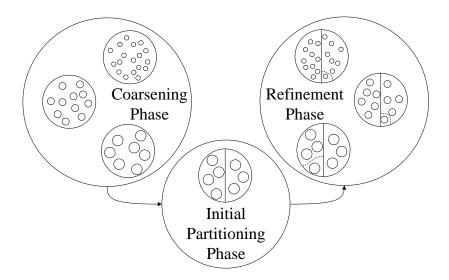

As circuit sizes have been growing exponentially, new techniques were needed to deal with this increase. In multilevel partitioning methods first the size of a graph is reduced using clustering techniques in the coarsening phase. Then, the coarsened circuit is partitioned using partitioning techniques in the initial partitioning phase. The last step of the algorithm is uncoarsening and refinement phase [27, 16, 17]. In Figure 2.22 the three phases of multilevel hypergraph partitioning are shown. Each one of these phases is described in the following.

### Coarsening phase

During this phase the smaller hypergraphs are constructed by clustering groups of vertices with common hyperedges. The clustered vertices form a single vertices and the hyperedges inside a cluster are removed from the reduced hypergraph. In Figure 2.22 two levels of coarsening is shown. In this figure the original hypergraph consists

Figure 2.22: Multilevel partitioning flowchart

of 18 vertices and the number of vertices are reduced to 12 after one level coarsening and it is reduced to 7 vertices after two level coarsening. There are different methods to cluster the vertices such as Edge Coarsening (EC), Hyperedge Coarsening (HEC), Modified Hyperedge Coarsening (MHEC) [27, 16, 17], best choice [28] and Netcluster [29].

### Initial partitioning phase

At this phase, the coarsest hypergraph is partitioned such that it has the smallest number of net cut, and the sizes of the partitions are almost equal. FM algorithm [26] is mainly used to perform this step. The coarsest hypergraph typically contains 75-200 nodes for which the FM algorithm performance is nearly optimal.

### Uncoarsening and refinement phase

In this phase at each level the coarse hypergraph is uncoarsened to one level finer hypergraph and every sub-cluster is assigned to the partition to which its parent cluster was located and a refinement algorithm is used to reduce the number of net cuts by moving the vertices between the partitions while maintaining the balance criteria. The most common algorithms that is used for the refinement is FM algorithm. Uncoarsening and refinement continue until the original graph is partitioned.

### 2.3 3D IC

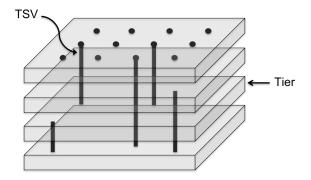

A 3D IC is a single chip in which the circuit elements are integrated in multiple vertical layers, called tiers or dies [3, 4, 5, 6, 30]. The interconnection between the tiers are known as 3D-Vias or TSVs of a 3D IC is shown in Figure 2.23.

Figure 2.23: An example of a 3D circuit with TSV

3D technology is a promising technology that aims to provide higher integration and reduced wire length. The higher integration results in smaller footprint and the reduced wire length reduces the power consumption of the circuit which leads to longer battery life and less operational cost. Also, reducing the wire length by 3D technology, especially reducing the length of long wires can decrease circuit delay.

3D ICs are not widely used yet; however among the notable 3D circuits, the 3D version of Pentium 4 CPU, presented by Intel in 2004, can be mentioned which

demonstrates 15% power saving and 15% performance improvement compared to its 2D version [1].

With the advances of 3D ICs, many new problems are added to the domain of physical design that are unique to these circuits. That's because the optimal design for 3D circuit is different from conventional 2D circuit design. Unlike the conventional 2D circuits, the circuit components lie on multiple tiers. One of the motivations of 3D technology is reducing the connection lengths.

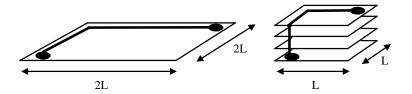

The example illustrated in Figure 2.24 shows how 3D technology reduces the wire length. For a given circuit, partitioning the circuit to four partitions as a 2D circuit, the longest connection would be between the point a and point b that would be 4l. However, 3D technology reduce the length of longest connection to 2l as shown in figure. Notice that TSV are used for the vertical connection and the thickness is not added to wire length. Reducing the wire length results in reduction of circuit delay as circuit delay is directly proportional to wire length. Also reduced wire length results in a better wire distribution and less congestion and less power consumption.

Figure 2.24: An example that shows how the 3D technology reduces the wire length

### 2.3.1 3D partitioning

In 3D IC partitioning, each partition forms a tier and the TSVs are used for the connections between layers [31, 32, 33]. The connection between two adjacent layer consumes 1 TSV but connection between two non-adjacent layer consumes m-n TSVs, where m and n are the numbers of the given layers, m > n. For example in a 4 tier circuit, a connection between tier 2 and tier 4 needs two TSVs. Therefore a 3D partitioning problem can be formulated as:

$$\min \sum_{e_{m,n} \in \Phi} w(e_{m,n})|m-n|, \tag{2.3}$$

$$s.t. \quad \sum_{v \in V_i} area(v) \le \frac{1}{k} \sum_{v \in V} area(v).$$

### 2.3.2 3D Partitioning Techniques

Several 3D computer-aided design tools exist. Three Dimensional Place and Route (TPR) is CAD tool that performs 3D physical design [34]. This tool uses hMetis algorithm to perform partitioning and divides the netlist to the number of partitions equal to the number of desired tiers. After dividing a circuit to tiers, the cells are placed and routed in each tier.

The partitioning step of TPR is performed using hMetis algorithm. Then, the partitions are ordered using a linear placement technique to minimize the total number of nets that are cut between two adjacent layers.

### I/O pins method

In I/O pin method [35, 11], 3D partitioning is performed by first partitioning and placing the I/O pins and then the cells based on the I/O locations. The reason that

this algorithm balances the I/Os is that the analytical placers use the I/O locations as the starting point.

There are different versions of I/O pins partitioning: Alternate pins, Unlocked pins, I/O Pins method and Refinement I/O Pins method.

The *I/O Pins method* algorithm computes the logical distance between I/O pins and considers the distance between each pair as the net weight in the first step. In order to find the logical distance between a pair of I/O pins the shortest paths between them are found. The algorithm uses hMetis tool to partition the I/O pins. Then the cells are partitioned based on the I/O pin locations and uses SA to stack the partitions.

The Alternate pins assigns the pins to the partitions alternatively and randomly. This algorithm replaces the first step of I/O pin method by assigning I/O nodes alternatively to different tiers. This algorithm provides a solution with balanced I/O pins.

The *Unlocked pins* partitions the whole netlist using hMetis and uses SA to stack the partitions. In this method I/O pins are not spread evenly.

Refinement I/O Pins method performs a refinement on solutions obtained from The I/O Pins method. In its refinement stage, the algorithm generates random perturbations of a solution and accepts or rejects the new solution based on cost variation. The new solution that decreases the cost is accepted and the solution that increases the cost is rejected.

The perform perturbation on a solution two alternatives are considered and one is selected each time with the probability of 50%. Either a cell or a I/O pin is randomly

moved to a random partition, or a pair of random cells or I/O pins are exchanged.

The cost function is composed of three factors: Number of 3D vias, area balance and I/O pin balance. The cost function is represented by following equation:

$$Cost = \frac{(w_v \times v)}{v_1} + \frac{(w_a \times a)}{a_1} + \frac{(w_p \times p)}{p_1}$$

where v, a, and p are normalized values for usage of 3D vias, area and I/O pin balance respectively. v is is the sum of square via number of each net. a is the subtraction of area of the largest tier by smallest one. And p is sum of I/O pin area of the tier with largest I/O pin area subtracted by sum of I/O pin area of the tier with smallest I/O pin area. v, a, and p are divided by their initial value before any perturbation  $v_1, a_1$ , and  $p_1$  to be normalized.  $w_v, w_a$ , and  $w_p$  are the weights imposed to tune the cost.

# 2.4 Simulated Annealing (SA)

SA is an iterative meta-heuristic optimization method introduced in [18, 36], based on Metroplis algorithm presented in [37]. This method simulates the process of annealing of metal, in which the metal is heated up to the melting temperature and then gradually cooled to allow the molecules (atomic structure) to get to an optimum energy state. Heating the metal allows the atoms to move from their initial position, wander randomly and move to higher energy states. Cooling gradually moves the atoms to lower energy states and finds better configuration than the initial configuration. That means the material which is in a certain energy level, changes its state to higher energy by heating and then goes to a lower energy level by being cooled

gradually.

In simulated annealing, the cost of function is analogous to the energy level of the material. The objective of an optimization problem is to minimize the cost function<sup>2</sup>(i.e. maximize the fitness function<sup>3</sup>), where the objective of annealing in metallurgy is to minimize the energy level. A high value for cost function of the problem is analogous to high energy state of a metal and a low value for cost function of the problem is analogous to low energy state of a metal.

The search space is simulated to the possible configurations of atoms. Each variable of the problem acts as an atom and possible values for each variable are analogous to possible positions of an atom. A candidate solution corresponds to a configuration of material.

The temperature in each step of annealing is simulated to a parameter T in SA. T is a parameter to be set according to the problem. Setting the initial T and the ratio of its decreasing depends on the problem. i.e. a certain value for initial T could be too high in solving one problem where the same value for initial T might be very low in solving another problem depending on the ratio of change in cost by a small change in the value of variables. This can be described by referring to annealing process. e.g. in metallurgy the material is heated to the stress-relief point which is called annealing temperature or annealing point. The annealing point and cooling rate for different materials are different e.g. for the glass it depends on thickness, thermal conductivity, heat capacity, and other features of the glass. In Table 2.1, the

<sup>&</sup>lt;sup>2</sup>Cost function is the objective function of a minimization problem.

<sup>&</sup>lt;sup>3</sup>Fitness function is the objective function of a maximization problem.

analogies between annealing and SA are described.

Table 2.1: Annealing analogy

|         | Metallurgy                       | Energy Level                              |

|---------|----------------------------------|-------------------------------------------|

| Analogy | General Optimization Problem     | Cost of Function                          |

|         | Specific 3D Partitioning Problem | Number of TSVs                            |

| Analogy | Metallurgy                       | Possible configuration of atoms           |

|         | General Optimization Problem     | Search space                              |

|         | Specific 3D Partitioning Problem | Position of cells in different tiers      |

|         | Metallurgy                       | Atom                                      |

| Analogy | General Optimization Problem     | Variable                                  |

|         | Specific 3D Partitioning Problem | Cell                                      |

|         | Metallurgy                       | Position of an atom                       |

| Analogy | General Optimization Problem     | Value of a variable                       |

|         | Specific 3D Partitioning Problem | Location of a cell                        |

|         | Metallurgy                       | Configuration of Material                 |

| Analogy | General Optimization Problem     | Candidate solution                        |

|         | Specific 3D Partitioning Problem | Partitioning Solution                     |

|         | Matalurgy                        | Temperature                               |

| Analogy | General Optimization Problem     | T Parameter                               |

|         | Specific 3D Partitioning Problem | T Parameter                               |

|         | Matalurgy                        | New Configuration with small change in    |

| Analogy |                                  | atoms position                            |

|         | General Optimization Problem     | Neighbor solution                         |

|         | Specific 3D Partitioning Problem | New partitioning Solution by moving a few |

|         |                                  | cells between partitions                  |

SA starts from an initial solution in the feasible space. This initial solution can be either random or a semi optimal solution obtained by another optimization method. Unlike hill climbing algorithms<sup>4</sup> that reject new solutions with the cost more than the cost of the current solution, SA accepts solutions with higher cost with a certain probability. At each iteration, a new candidate solution is selected randomly in the neighbourhood of the current solution. If the cost of the new solution is lower than the

<sup>&</sup>lt;sup>4</sup>Hill climbing algorithms are iterative local search algorithms that start with an arbitrary solution and generate new solution by a change in the current solution. If the change produces a better solution, the current solution is replaced with the new solution repeating until no further improvements can be found.

cost of the current solution, the new solution is accepted. Otherwise the probability of its acceptance depends on the difference of the cost of the current solution and the candidate solution and the value of T. The higher the value of T, the higher is the chance of accepting the solution with higher cost. At the early stages of the algorithm, the T is set to be large and the probability of acceptance of high cost solutions is close to one. Therefore the algorithm gives chance for both uphill and downhill moves. Uphill moves are the moves that increase the cost of solution and downhill moves are the moves that decrease the cost of solution. As the temperature is decreased during the algorithm operation the probability of accepting high cost solutions goes down.

SA is an iterative method. In each iteration, algorithm considers a neighbour solution s' and decides between moving to the neighbour solution s' or staying at the current solution s. The decision is based on the quality of neighbour solution or a probability. If the neighbour solution s' is better than current solution s, i.e. The value of function at s' is smaller than the value of function at s, then s is replaced by s'. Otherwise, if s' results in a higher cost, the algorithm accepts the s' with a probability. This probability depends on the difference of costs between current solution and the candidate solution and also on the varying parameter T. This probability is specified by the acceptance probability function P which is based on Boltzmann acceptance criterion [18]:

$$P = e^{-\Delta cost/T} \tag{2.4}$$

### $\Delta cost = cost_{new} - cost_{current}$

The neighbour solution is a state in search space that is produced by a small perturbation to the current solution i.e. a small change in value of one or more variable. The action of changing the state is called a "move". For a particular problem different moves can be considered.

# Algorithm 3 Simulated Annealing

Input: Initial Solution  $s_{init}$ Output: Optimized Solution

```

1: Begin

2: T \leftarrow T_0

3: i \leftarrow 0

4: s \leftarrow s_{init}

5: cost_{current} \leftarrow Cost(s)

6: while T > T_{min} do

while stopping criteria do

7:

8:

i \leftarrow i + 1

s' \leftarrow \text{neighbor}(s)

9:

10:

cost_{new} \leftarrow Cost(s')

\Delta cost = cost_{new} - cost_{current}

11:

if \Delta cost < 0 then

12:

s \leftarrow s'

13:

14:

cost_{current} \leftarrow cost_{new}

else

15:

16:

r \leftarrow Random(0,1)

if r < e^{-\Delta cost/T} then

17:

s \leftarrow s'

18:

19:

cost_{current} \leftarrow cost_{new}

end if

20:

end if

21:

end while

22:

23:

T \leftarrow \alpha.T

24: end while

25: End.

```

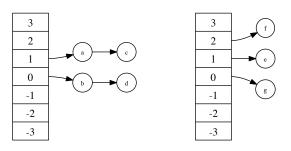

### 2.5 Force Directed Placement

In recent years, many placement algorithms have been proposed to minimize a measure of total wire length [38, 39, 40]. Analytical placers are designed based on the global optimization algorithms and have recently received much consideration from both academia and industry. These placers usually spread the cells over the placement area and minimize the total wire length simultaneously. Force directed placement is a type of analytical placement during which cells and their connections are modelled as a mass-spring system [41]. The connected cells attract each other and the magnitude of attraction is directly proportional to the distance between the cells or the connection length. In mass-spring system, the cells, which are free to move, will move in the direction of their forces and will settle in a configuration with the minimum energy. In the force directed placement, cells that are free to move are allowed to move in the direction of the forces applied to them. Therefore, the placement problem is reduced to solving an optimization problem.

The most used wire length measure is the squared Euclidean distance as it is a continuously twice differentiable function. Therefore, the placement problem formulation is as follows:

$$\min L = \sum_{i=1,j=1}^{n} c(i,j)((x_i - x_j)^2 + (y_i - y_j)^2), \tag{2.5}$$

where n represents the total number of cells and c(i, j) is the corresponding connection cost between the cells i and j if they are connected and 0, otherwise. During global placement, each dimension can be considered independently. Therefore, the

formulation can be divided into two separate optimization problems as follows:

$$\min L_x = \sum_{i=1,j=1}^n c(i,j)(x_i - x_j)^2,$$

$$\min L_y = \sum_{i=1,j=1}^n c(i,j)(y_i - y_j)^2.$$

This type of force directed technique is in a new capacity to perform partitioning in this thesis.

# Chapter 3

# Constructive 3D Partitioning

### 3.1 Introduction

In 3D partitioning, the quality of the solution does not only depend on the quality of the partitioning stage, but also on the quality of the floor planning where the locations of different tiers are determined.

A major contribution of this thesis is combining several partitioning and floor planning techniques so as to obtain better 3D partitions. The proposed technique reduces the number of nets between partitions and the number of times that a net is cut, and consequently, reduces the TSV usage by both providing high quality partitions and reducing the number of long connections.

First, different 2D partitioning methods are studied and the best technique for obtaining initial partitions is determined. In addition, experiments are performed to determine the best trade-off between the number of initial partitions and run time of the algorithm. The 1D force-directed placement is developed and solved for the partitioning problem to obtain the best locations of the partitions. Finally, it is proposed to obtain an initial 3D partitioning solution by merging layers together.

The rest of this chapter is organized as fallows. The proposed constructive 3D partitioning algorithm is introduced and described in Section 3.3. In Section 3.4, the results of the proposed 3D partitioning are given. Finally, a summary of the chapter

### 3.2 Problem Statement

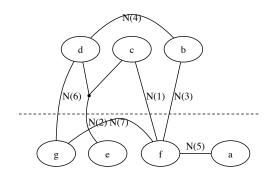

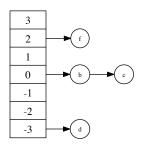

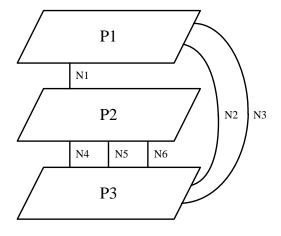

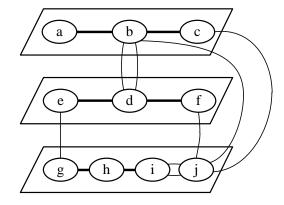

In a 3D circuit, partitions are stacked on top of each other and any connection between two non-adjacent partitions results in using more than one TSV. For example, considering a 3D IC with 5 tiers, if one terminal of a net is placed in the top tier and the other terminal in the bottom tier, the net is effectively cut 4 times and 4 TSVs will be required to complete one single connection. The example in Figure 3.1 shows how the location of tiers affects the number of TSVs. Stacking the partitions in the order shown in 3.1(a) results in usage of 8 TSVs, while changing the order of partitions to the order shown in 3.1(b) reduces the number of TSV usage to 7.

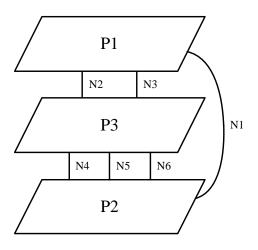

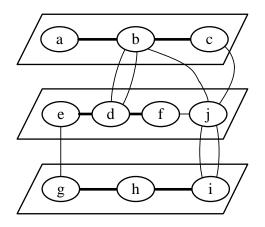

On the other hand, the produced partitions targeting 2D partitioning are not always the optimal partitions targeting 3D partitioning, even if they are stacked in their best possible order. This fact is shown using an example given in Figure 3.2. In 3.2(a) the best 2D partitioning solution of a circuit is given, where the number of 2D net cuts is equal to 6. Theses partitions are stacked in their best order in 3.2(a) and the number of 3D net cuts is equal to 8. However another partitioning solution for the same circuit, which is given in 3.2(b), results in 7 2D net cuts and 7 3D net cuts in its best stacking order. This is an example showing that the optimal partitions for 3D circuits may be different from the optimal partitions targeting 2D partitioning.

In this thesis, the goal of 3D partitioning is set to be to minimize the number of nets that are cut by any horizontal line drawn between any pair of adjacent tiers.

(a) Net cuts in 3D partitioning = 8

(b) Net cuts in 3D partitioning = 7

Figure 3.1: The effect of stacking the partitions in proper order in reducing the number of vias.

(a) Optimal partitioning solution targeting 2D circuit

(b) Optimal partitioning solution targeting 3D circuit

Figure 3.2: An example that shows the optimal 2D partitioning solution is not always the optimal 3D partitioning solution. The weight of thick edges is equal to 20 and the weight of narrow edges is equal to 1.

This means that, during partitioning, two optimization criteria are considered: form the optimal tiers, and determine the optimal locations of different tiers. These two optimization can not be done in series, since it is not possible to verify the optimal partitions before they are stacked. In this work, a technique that considers both of the mentioned criteria is introduced.

In developing the proposed constructive 3D partitioning algorithm, partitioning methods are combined with floor planning methods and the partitioning and floor planning stages are performed simultaneously.

# 3.3 Proposed Constructive 3D Partitioning

In this work a new approach is utilized to form the initial tiers i.e it is proposed to divide the circuit to several partitions (3 to 5 times of the number of desired tiers) instead of traditionally dividing the circuit to the exact number of desired tiers and form the tiers by finding the best combination of initial partitions while determining the best location of partitions at the same time.

Among the different partitioning methods, multilevel hypergraph partitioning is selected to perform initial partitioning. hMetis tool is used to perform this task, which provides high quality 2D partitions and renders an efficient run time of the algorithm. Another technique used in the proposed algorithm is the linear ordering, which is mainly used in floor planning stage of the physical design. The algorithm arranges the previously generated partitions in a single row in a way that minimizes the length of connections and consequently the number of net cuts. Ordering the initial partitions

rather than stacking them randomly results in locating the partitions that have more connections close to each other. This consequently reduces the length of connections and the number of long connections and gives the semi optimal combination of the partitions to form the tiers.

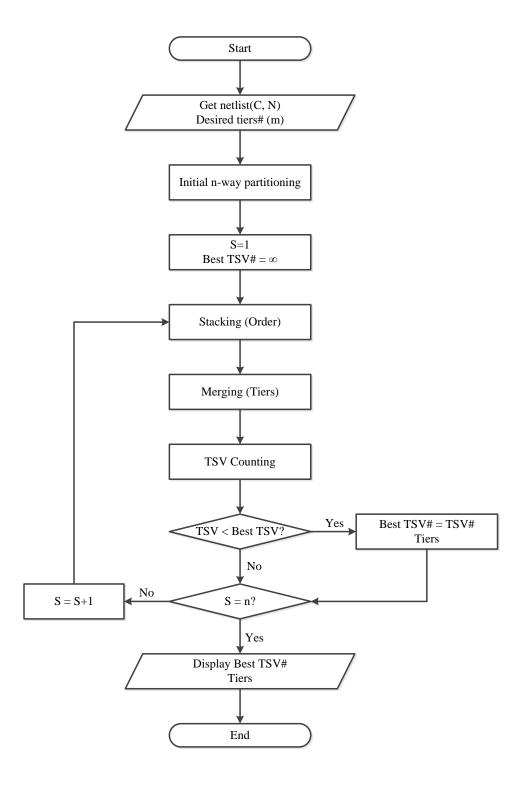

The flowchart of proposed 3D constructive partitioning algorithm is shown in Figure 3.3. This algorithm has three main phases: k-way partitioning, stacking and merging. The steps of the algorithm are described in this section. First, the netlist and the desired number of tiers are fed to the algorithm. Then, an initial k-way partitioning is performed. A detailed description of this step can be found in Subsection 3.3.1. At this point and after the initial partitioning, each initial partition is selected as a seed cell (parameter S) and forms the bottom layer and the following procedure is implemented: (1) Stacking, through solving a linear ordering problem, for which the detailed explanation can be found in Subsection 3.3.2. The ordered partitions form the initial layers of the circuit. At this point, each cell belongs to a layer which has a location on the z-axes assigned to it. (2) merging, whose details are given elsewhere (refer to Subsection 3.3.3). Via merging, depending on the desired number of tiers, the initial layers are combined and form the initial tiers. Afterwards, the number of TSVs is counted to determine the suitable order that generates the minimum number of TSVs.

The inputs of the algorithm shown in Figure 3.3 are the netlist and the desired number of tiers, m. The output of the algorithm is the 3D partitioned netlist i.e. the tiers and their order and the number of TSVs needed. First, the netlist is divided into n partitions using multilevel hypergraph partitioning technique, where n is a

Figure 3.3: Proposed constructive algorithm flowchart

multiple of m. Then the generated partitions are stacked using a linear ordering heuristic. Every n/m successive layers are merged and form the 3D tiers.

In Section 3.3.1 the initial partitioning step is described. The linear ordering stage and merging the layers are described in Sections 3.3.2 and 3.3.3 respectively.

### 3.3.1 Multilevel Partitioning