#### THE UNIVERSITY OF CALGARY

Implementing Digital Signal Processing Algorithms

**Using Serial Arithmetic**

by

#### P.J.W. Graumann

#### A THESIS

## SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

## CALGARY, ALBERTA SEPTEMBER, 1996

© P.J.W. Graumann 1996

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced with the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-20869-9

# Canadä

### Abstract

This thesis describes a set of computer aided design tools, implemented by the author, which can be used to shorten the design time of hard-wired digital signal processing systems. These tools convert a bit-serial or digit-serial register transfer level circuit. described in DFIRST, into a gate level technology specific implementation. The DSIM simulator used to perform design rule checks, serial timing alignment checks and circuit simulations on DFIRST netlists is introduced. The TRANS hardware compiler converts the DFIRST primitives to generic gate level implementations and then applies optimizations to the obtain a smaller/faster implementation in the target technology. Several digital filters are implemented using DFIRST and TRANS and the different TRANS optimizations, and the quality of solutions generated for different digit-width filters are presented and discussed.

## Acknowledgements

I am grateful to Micronet. Dr. Turner, and the Electrical Engineering Department for their financial support during this research. I would also like to thank Dr. Turner for his patience during the slow times and his good advice in the tough spots. I would escpecially like to thank the numerous graduate and summer students who implemented circuits using these tools. There were a lot of questions to answer, software bugs to exterminate and late nights, but most of these projects were successful in the end and the results of this research are the better for their efforts.

## Dedication

For my Beloved wife Koreen.

## **Table of Contents**

| T  | itle <b>I</b> | Page                                     | i        |

|----|---------------|------------------------------------------|----------|

| A  | ppro          | val Page                                 | ii       |

| A  | bstra         | ıct                                      | iii      |

| A  | ckno          | wledgements                              | iv       |

| D  | edica         | tion                                     | v        |

| Ta | able (        | of Contents                              | vi       |

| Li | ist of        | Tables                                   | x        |

| Li | ist of        | Figures                                  | cii      |

| 1  | Intr          | oduction                                 | 1        |

|    | 1.1           | Digital Signal Processing                | 1        |

|    | 1.2           | Digital Signal Processor Implementations | 2        |

|    |               | 1.2.1 Programmable Devices               | <b>2</b> |

|    |               | 1.2.2 Custom Implementations             | 3        |

|    |               | 1.2.3 Integrated Circuit Efficiency      | 4        |

|    | 1.3           | Architectures                            | 5        |

|    |               | 1.3.1 Number Formats                     | 6        |

|    |               | 1.3.2 Word Formats                       | 8        |

|    | 1.4           | Synthesis                                | 10       |

|    |               | 1.4.1 Y-Chart                            | 12       |

|    |               | 1.4.2 Silicon Compilation                | 15       |

|    |               | 1.4.3 Validation                         | 17       |

|    | 1.5           | Research Goals                           | 18       |

|    | 1.6           | Overview                                 | 19       |

| 2  | DFI           | IRST Language and Simulator              | 21       |

|    | 2.1           |                                          | 21       |

|    | 2.2           | Design Example                           | 24       |

|    | 2.3           | • •                                      | 26       |

|    |               |                                          | 27       |

|    |               |                                          | 29       |

|   |            | 2.3.3 Instantiation $\ldots$ 30                  |

|---|------------|--------------------------------------------------|

|   |            | 2.3.4 Encapsulation                              |

|   |            | 2.3.5 I/O Pads 32                                |

|   |            | 2.3.6 Constants                                  |

|   | 2.4        | DSIM                                             |

|   |            | 2.4.1 Signal timing                              |

|   |            | 2.4.2 Parallel vs. Serial Signals 35             |

|   |            | 2.4.3 Data File Format                           |

|   |            | 2.4.4 Signal Tracing 40                          |

|   |            | 2.4.5 Number Interpretation                      |

|   |            | 2.4.6 Simulation errors and warnings 41          |

|   | 2.5        | Summary                                          |

| - | -          |                                                  |

| 3 |            | IRST Primitives 44                               |

|   | 3.1        | Standard Components                              |

|   | 3.2        | Storage                                          |

|   | 3.3        | Serial Adder                                     |

|   | <b>.</b> . | 3.3.1 Adder schematic                            |

|   | 3.4        | Right Shift         51                           |

|   |            | 3.4.1 Digit Serial                               |

|   | • -        | 3.4.2 DFIRST instantiation                       |

|   | 3.5        | Left Shift                                       |

|   |            | 3.5.1 Digit Serial Left Shifter                  |

|   |            | 3.5.2 DFIRST 57                                  |

|   | 3.6        | Parallel to Serial                               |

|   |            | 3.6.1 Word Recirculation                         |

|   |            | 3.6.2 Fan-out Control                            |

|   |            | 3.6.3 DFIRST 62                                  |

|   | 3.7        | Serial to Parallel Converter                     |

|   |            | 3.7.1 DFIRST                                     |

|   | 3.8        | Multiplication                                   |

|   |            | 3.8.1 Two's Complement Multiplication            |

|   |            | 3.8.2 Two's Complement Multiplier Implementation |

|   | 3.9        | Coefficient Recoding                             |

|   |            | 3.9.1 Booth Recoding                             |

|   |            | 3.9.2 Modified Booth Recoding                    |

|   |            | Lyon's Multiplier                                |

|   |            | FIRST Multiplier                                 |

|   |            | Radix Four DFIRST multiplier7575                 |

|   | 3.13       | Radix Eight DFIRST Multiplier    78              |

|   | 3.14 | Evaluation of Bit-Serial DFIRST multipliers 80 |

|---|------|------------------------------------------------|

|   |      | 3.14.1 Hardware Complexity 80                  |

|   |      | 3.14.2 Critical Path                           |

|   | 3.15 | Digit-Serial multiplier                        |

|   |      | 3.15.1 DFIRST                                  |

|   | 3.16 | Parallel coefficient Multipliers               |

|   |      | 3.16.1 DFIRST                                  |

|   |      | 3.16.2 Extended Multiply                       |

|   |      | 3.16.3 DFIRST                                  |

|   |      | 3.16.4 Constant Multiplication                 |

|   |      | 3.16.5 DFIRST                                  |

|   | 3.17 | Controlgenerator                               |

|   | 3.18 | Other DFIRST Primitives                        |

|   | 3.19 | Summary                                        |

| 4 | TRA  | ANS Hardware Compiler 97                       |

|   | 4.1  | ASIC Architectures                             |

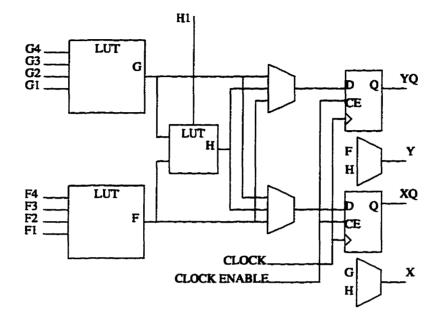

|   |      | 4.1.1 XILINX FPGAs                             |

|   |      | 4.1.2 ACTEL FPGAs                              |

|   |      | 4.1.3 ACTEL Software                           |

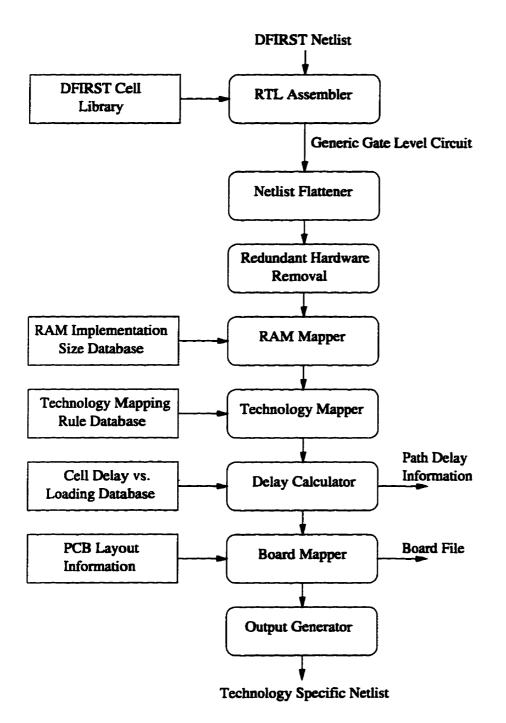

|   | 4.2  | TRANS overview                                 |

|   | 4.3  | Technology Files 103                           |

|   | 4.4  | Netlist Flattening                             |

|   | 4.5  | Redundant Hardware                             |

|   | 4.6  | Hardware Mapping                               |

|   |      | 4.6.1 Cell Internal Connections                |

|   |      | 4.6.2 XILINX Mappings                          |

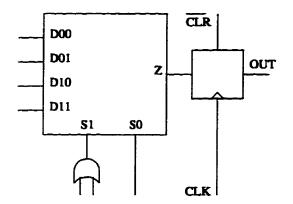

|   | 4.7  | RAM mapping                                    |

|   |      | 4.7.1 Shared Addressing Units                  |

|   | 4.8  | Delay Calculation                              |

|   | 4.9  | Summary                                        |

| 5 | Арр  | lications 120                                  |

|   | 5.1  | Digital Filters                                |

|   |      | 5.1.1 FIR Filters                              |

|   |      | 5.1.2 Bilinear LDI Digital Filter              |

|   |      | 5.1.3 Wave Digital Filter                      |

|   |      | 5.1.4 N2 Filter                                |

|   | 5.2  | High Level Synthesis Tools                     |

|   |      | 5.2.1 BITSYN                                   |

|    |       | 5.2.2   | SNAFU                             | . 127         |

|----|-------|---------|-----------------------------------|---------------|

|    |       | 5.2.3   | FIRGEN-DIGIPARSE                  | . 128         |

|    | 5.3   | Mappi   | ng Performance                    | . 129         |

|    |       | 5.3.1   | ACTEL Mapping                     | . 130         |

|    |       | 5.3.2   | RAM Mapper Performance            | . 131         |

|    |       | 5.3.3   | Overall Performance               | 134           |

|    |       | 5.3.4   | Filter Implementation Comparisons | 135           |

|    | 5.4   | 61 Tap  | FIR Filter                        | 137           |

|    | 5.5   | Digit-S | Serial Circuits                   | . 1 <b>40</b> |

|    |       | 5.5.1   | Digit-Serial Multipliers          | 140           |

|    |       | 5.5.2   | Digit-Serial Filters              | 143           |

|    |       | 5.5.3   | Optimization Performance          | 144           |

|    | 5.6   | Summ    | ary                               | 150           |

| 6  | Sum   | imary   | and Discussion                    | 152           |

|    | 6.1   | •       | Work                              | 154           |

|    |       | 6.1.1   | Design Entry and Validation       | 155           |

|    |       | 6.1.2   | Synthesis                         |               |

|    |       | 6.1.3   | Optimization                      | 157           |

| Bi | bliog | raphy   |                                   | 159           |

| A  | 61 J  | ap FII  | R Filter Coefficients             | 166           |

## List of Tables

| 2.1  | Possible DFIRST signal Declarations                                 | 28  |

|------|---------------------------------------------------------------------|-----|

| 3.1  | Timing Alignment Verification for Two's Complement Multiplier Stage | 68  |

| 3.2  | Booth Recoding for two coefficient bits                             | 71  |

| 3.3  | Modified Booth Recoding for three coefficient bits                  | 72  |

| 3.4  | Hardware Complexity for various Bit-Serial Multipliers              | 81  |

| 3.5  | Bit-Serial Multiplier Critical Paths                                | 82  |

| -1.1 | Cost in CLBs for Several Lengths of RAMs, 1                         | .15 |

| 5.1  | ACTEL Cell Counts for Test Filters                                  | .30 |

| 5.2  | ACTEL Critical Path Lengths (ns) 1                                  | .31 |

| 5.3  | Test Filter Contiguous Shift Register Lengths                       | 32  |

| 5.1  | TRANS Address Allocations and CLB Cost Estimate 1                   | .32 |

| 5,5  | User Address Allocations and CLB Cost Estimate                      | .33 |

| 5.6  | XILINX 4000 Series RAM Mapping                                      | 33  |

| 5.7  | DFFs/FG for XILINX 4000 Series RAM Mapping                          | 34  |

| 5.8  | Overall Area Reductions by TRANS Optimizations                      | 34  |

| 5.9  | Overall Critical Path Reductions by TRANS Optimizations 1           | 34  |

| 5.10 | Number of Clock Cycles per Input Sample                             | 35  |

| 5.11 | ACTEL Area-Time Products for Test Filters                           |     |

| 5.12 | ACTEL Area-Time Products for Test Filters                           | 38  |

| 5.13 | Area and Computation Time                                           | 42  |

| 5.14 | ACTEL Area Before and After TRANS Optimizations 1                   | 44  |

| 5.15 | ACTEL Critical Paths Before and After TRANS Optimizations 1         | 45  |

| 5.16 | Area Reductions and RAM Efficiency for                              | 47  |

| 5.17 | ACTEL Area for Different Digit Width LDI Filters 1                  | 48  |

| 5.18 | Efficiency data for Test LDI Filter                                 | 48  |

| 5.19 | Final AT Products for Different Digit Width LDI Filters 1           | 49  |

## List of Figures

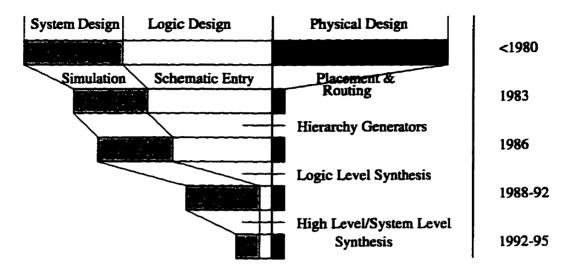

| 1.1  | Time Line                                                              | 11 |

|------|------------------------------------------------------------------------|----|

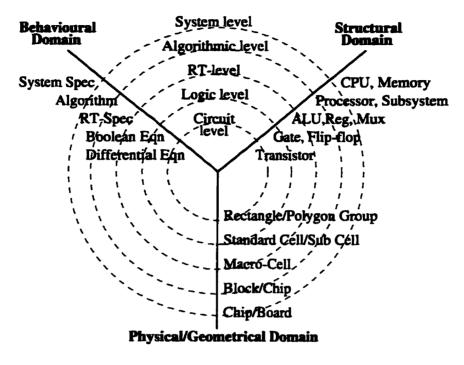

| 1.2  | Y-chart                                                                | 12 |

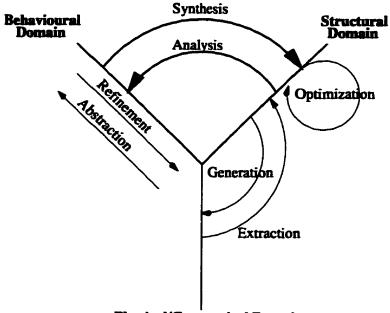

| 1.3  | Y-chart Transformations                                                | 14 |

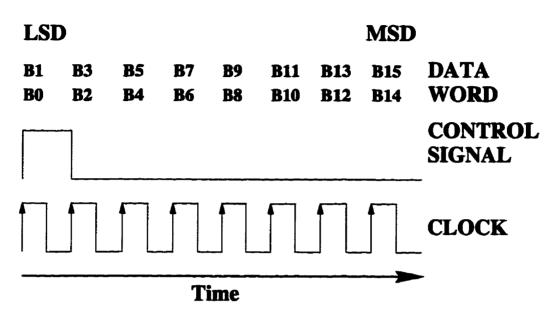

| 2.1  | Sample DFIRST DataWord                                                 | 22 |

| 2.2  | Generic DFIRST Operator                                                | 24 |

| 2.3  | Biquad Digital Filter Flow Graph                                       | 25 |

| 2.4  | Bit-Serial Implementation of Biquad Filter                             | 26 |

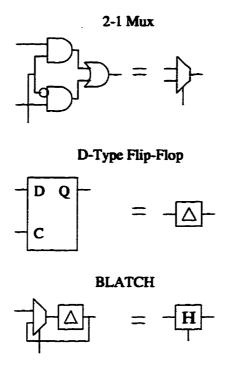

| 3.1  | Schematic Representation for a MUX. DFF and BLATCH element             | 45 |

| 3.2  | Bit-Serial Carry Save Adder                                            | 47 |

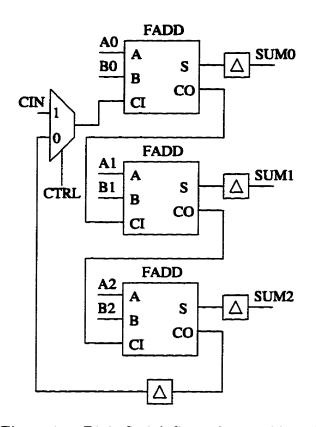

| 3.3  | Digit-Serial Carry Save Adder (W=3)                                    | 48 |

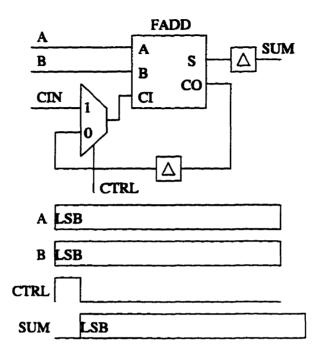

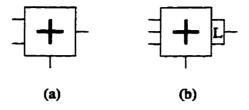

| 3.4  | Adder Schematics (a) cin grounded and zero delay (b) latency of L $$ . | 50 |

| 3.5  | Circuit for Bit-Serial right shift by P                                | 51 |

| 3.6  | Twelve bit $W=3$ serial data word and data word right shifted by two   | 52 |

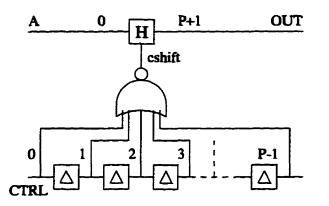

| 3.7  | Digit-Serial right shift operator for $W=3$ and $p=4$                  | 53 |

| 3.8  | Circuit for Bit-Serial left shift by P                                 | 55 |

| 3.9  | Sixteen bit $W=4$ serial data word and data word left shifted by three | 56 |

| 3.10 | Digit-serial Left shift operator with $W=3$ and $P=5$                  | 57 |

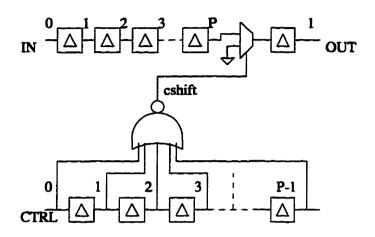

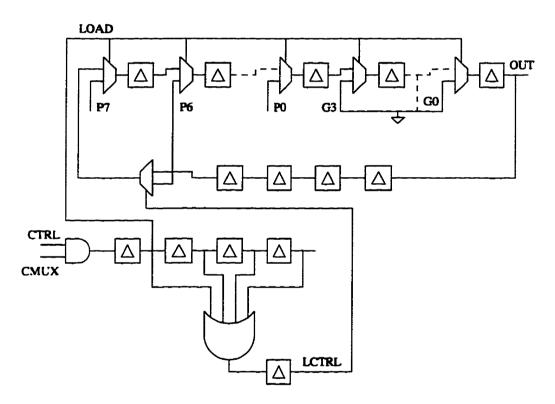

|      | Bit-Serial Parallel to Serial Converter                                | 58 |

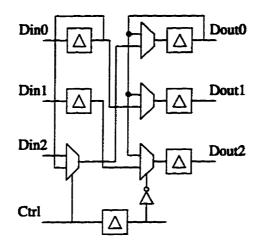

| 3.12 | Parallel to Serial Converter (W=3, NP=8, G=4)                          | 59 |

| 3.13 | Parallel to Serial Converter with data storage                         | 61 |

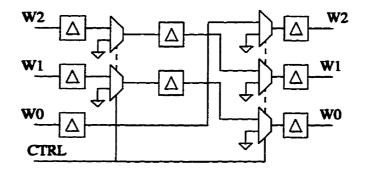

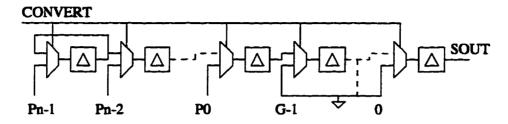

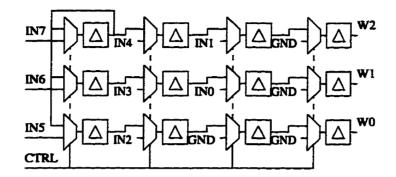

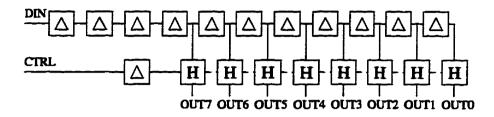

| 3.14 | Bit-Serial Serial to Parallel Converter (NP=8.SK=2)                    | 63 |

| 3.15 | Serial to Parallel Converter (W=3, NP=8. SK=2)                         | 64 |

|      | Two's Complement Long Multiplication                                   | 66 |

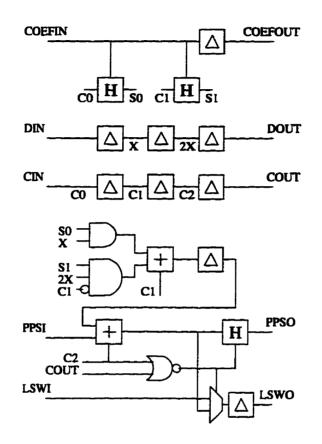

| 3.17 | Bit-Serial Two's Complement Multiplier Stage                           | 67 |

| 3.18 | Bit-Serial Two's Complement Multiplier Final Stage                     | 69 |

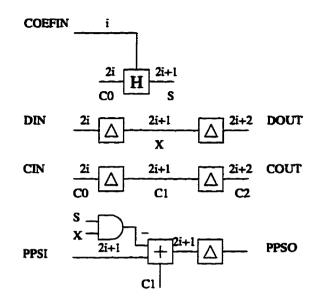

| 3.19 | Lyon Modified Booth Recoded Bit-Serial Multiplier Stage                | 73 |

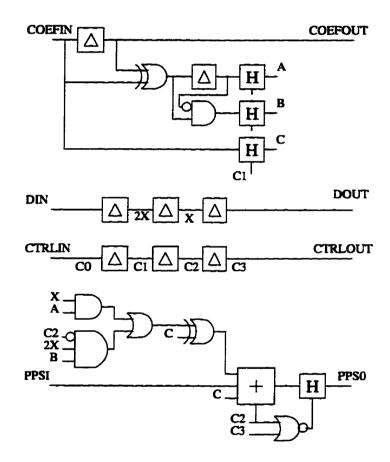

|      | Radix Four DFIRST Internal Multiplier Section                          | 76 |

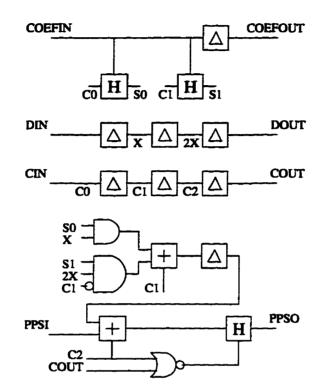

| 3.21 | Radix Four Bit-Serial Final Multiplier Stage                           | 77 |

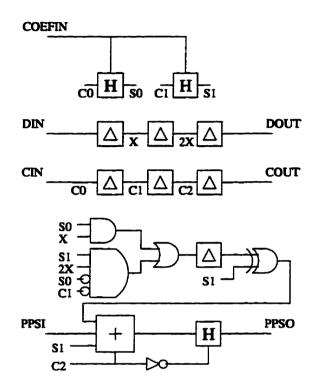

|      | Radix Eight DFIRST Multiplier Section                                  | 79 |

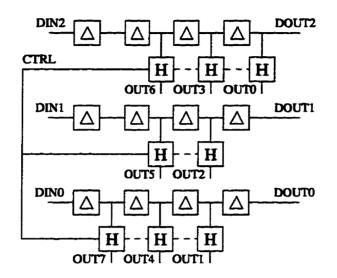

| 3.23 | Digit-Serial (W=2) DFIRST Multiplier Module                            | 83 |

|      | Digit-Serial Multiplier Section                                        | 85 |

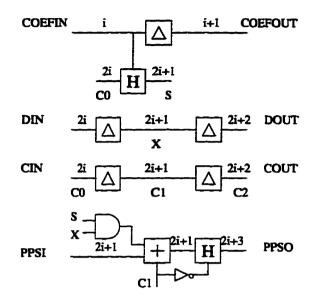

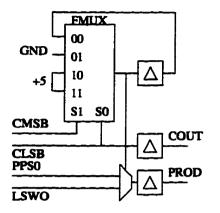

| 3.25 | Parallel Coefficient DFIRST Multiplier Section                         | 87 |

|      | Extended Multiplier Section                                            | 89 |

| 3.27 | Final Product Generation Element for DFIRST Extended Multiply .        | 90 |

| 3.28 | Bit-Serial Constant Multipliers (a) 15/32 (b) 27/64                    | 93 |

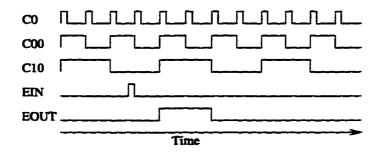

| 3.29 | Control Signals from Sample CONTROLGENERATOR                           | 96 |

|      |                                                                        |    |

| 4.1  | XILINX I/O Block Resources                                        |

|------|-------------------------------------------------------------------|

| 4.2  | Simplified Block Diagram of a 4000 Series XILINX CLB 100          |

| 4.3  | ACTEL S-module                                                    |

| 4.4  | TRANS Hardware Compiler Flow Diagram                              |

| 4.5  | Sample TRANS Technology File                                      |

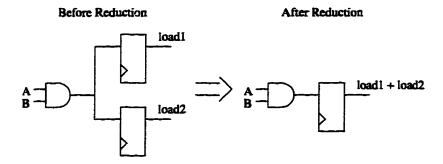

| 4.6  | Redundant Hardware Removal Operation Saving One DFF 107           |

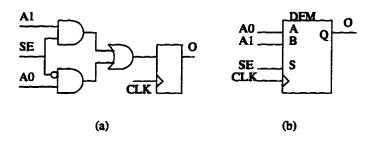

| 4.7  | Mapping Source(a) and Target(b) for DFM ACTEL Cell 108            |

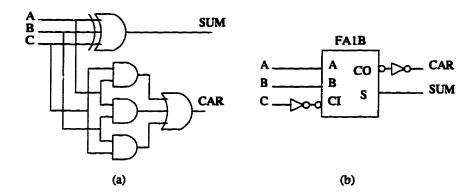

| 4.8  | Source(a) and Target(b) for ACTEL Full Adder Implementation 109   |

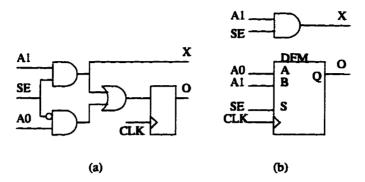

| 4.9  | Source(a) and Target(b) for DFM Cell with Internal Connection 110 |

|      | Two Bit Shift Register Implemented in one XILINX IOB 111          |

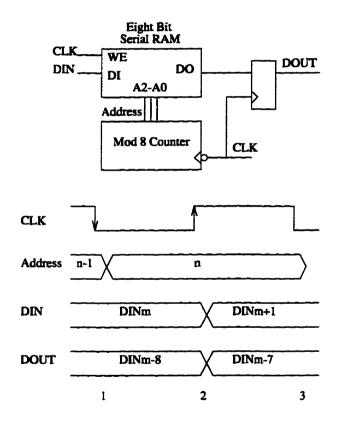

| 4.11 | RAM Implementation of Eight Bit Shift Register with Timing 113    |

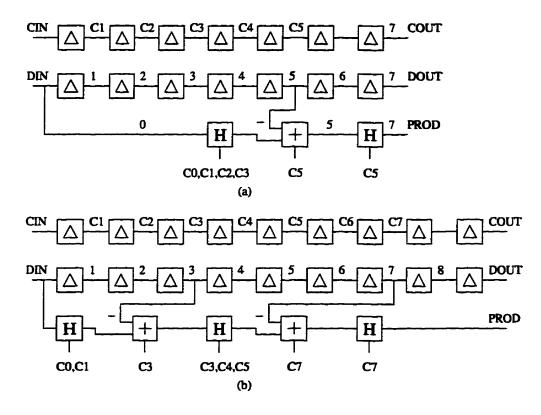

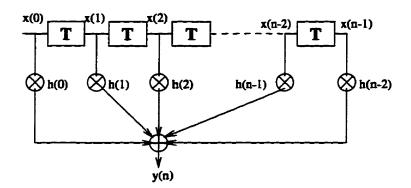

| 5.1  | FIR Filter Structure                                              |

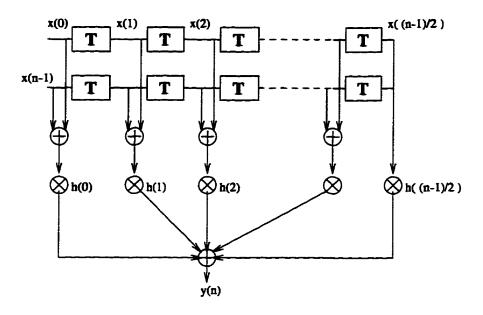

| 5.2  | Linear Phase FIR filter structure (odd order)                     |

| 5.3  | 5th Order Bilinear LDI Filter Structure                           |

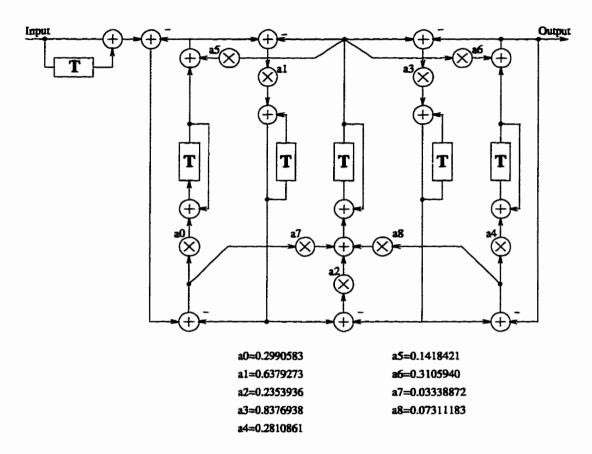

| 5.4  | 7th Order Wave Digital Filter Structure                           |

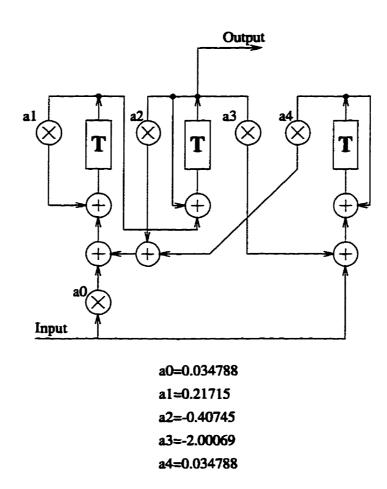

| 5.5  | N2 Filter Structure Generated by Noisegen                         |

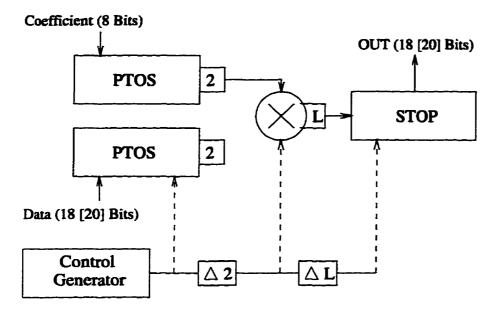

| 5.6  | Multiplier Test Circuit                                           |

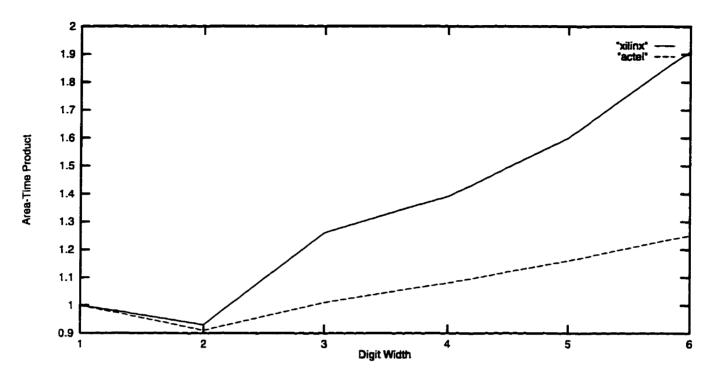

| 5.7  | Digit-Serial Multiplier Area-Time Products                        |

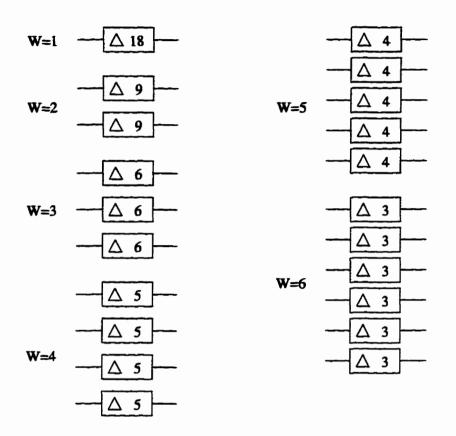

| 5.8  | Word Delay Implementation for Digit Widths 1 to 6                 |

### Chapter 1

### Introduction

The use of Digital Signal Processing (DSP) Integrated Circuits (ICs) has increased dramatically. They are used in everything from cellular phones to microwave ovens to CD players. The operations performed by these devices increases in complexity as IC geometries shrink and the need for faster/smaller processing devices increases. This increased complexity results in larger ICs and longer design times to create working products from specifications. In order to shorten the design cycle and hence reduce the time to market for a new device. designers must rely on more and more sophisticated and capable Computer Aided Design (CAD) tools. This thesis describes a CAD tool. implemented by the author, which can be used to reduce the time required to convert a DSP IC specification to a digital circuit implementation.

### 1.1 Digital Signal Processing

A signal is defined as a physical quantity which conveys information [OS89]. An analog signal is one in which the independent variable such as time, and the dependent variable such as amplitude can take on a continuum of values. In these systems time is going forward and the amplitude contains some information to be processed. In a discrete time system, time can only take a discrete set of values and the amplitude information is continuous in nature. In a digital signal both time and amplitude are discrete in nature. A digital signal can be represented by a sequence of finite precision. or quantized, numbers representing the information in a signal at discrete intervals of time.

The transformation of one signal to another signal is defined as signal processing. During this transformation unwanted portions of the first signal may be removed or information may be added to create a desired output signal. Digital Signal Processing (DSP) is performed using simple computational blocks such as addition. multiplication. conditionals and storage elements. The types and interconnections of these processing elements define the processing algorithm and control the behaviour of the processing system.

#### **1.2 Digital Signal Processor Implementations**

#### 1.2.1 Programmable Devices

General purpose Digital Signal Processing devices such as the TMS320 [Ins88]. the ADSP2100 [Dev89] and the Motorola 56001 [Mot89] have been used extensively to perform DSP operations. Their programmable nature makes them easy to use and re-use in the face of ever changing specifications. Programmable devices generally contain one multiplier, one adder and a bit shifting unit as well as a number of registers and internal memory. These resources make programmable DSPs able to perform most signal processing applications. The wide use of these devices also means that silicon implementation technology will be constantly upgraded. resulting in ever faster and larger versions in the same processor family. The large numbers of devices which are fabricated also reduces the per unit cost. resulting in lower monetary costs for the user. While the programmable nature of these devices makes them easy to use it also results in reduced algorithm security. The processing application must be stored in a memory device of some sort which can be easily copied. Also, because these devices are so flexible they may not be particularly well suited to a specific application. The programmable nature adds some overhead to circuit area and the fixed nature of the resources may not be optimal for many algorithms. This can mean slow performance or larger system cost.

#### **1.2.2** Custom Implementations

Digital Signal Processing applications may also be implemented using custom integrated circuits. There are three different general forms of these devices: full custom. semi-custom gate arrays and Field Programmable Gate Arrays (FPGAs). In full custom the designer has complete control over the placement, sizing and interconnect of every transistor constituting a given design. Full custom devices require the longest design time but yield the most efficient solutions in terms of area. throughput or cost (given sufficient quantities). The complexity of the design process for full custom devices makes re-design and re-fabrication very expensive, forcing the designer(s) to get the product right the first time or face long delays and higher costs. The implementation time from specification to working ICs for these devices can range from several months to a year.

In semi-custom integrated circuits, or Mask Programmable Gate Arrays (MP-GAs). the transistor patterns are fixed. The designer only has control over the interconnection of groups of transistors as logic and the interconnection of these logic elements. This results in a smaller design time but also results in slower. larger

circuits as compared to a full custom implementation. The fabrication time for these devices is shorter than that of full custom devices and can be several weeks to months. The re-design time for these components is much less than that for full custom devices but significant effort is still needed to change the circuit and re-fabricate the final device.

Field programmable gate arrays are similar to MPGAs except that the interconnection wires are programmable in the field instead of requiring a fabrication facility to place the interconnects. These devices can be classified into two basic types. one time programmable such as ACTEL [ACT89] FPGAs and n time programmable such as XILINX [XIL94] FPGAs. These devices lead to implementations which are relatively large and slow and not particularly well suited to high throughput or high volume applications. They are well suited for proto-typing and in situations where the application requirements change over time. The availability of these devices has led to novel applications in which a single FPGA is re-programmed on the fly to perform different portions of a single large application.

#### 1.2.3 Integrated Circuit Efficiency

For any application there may be several possible IC implementations. The efficiency of different implementations is judged in terms of the amount of circuit area required. the time required to compute the algorithm and the power consumption of the circuit. One measure used to evaluate the efficiency of an IC implementation is the Area-Time (AT) product [HC90] which equally weights both area and time.

The area of an implementation is the total area required for processing blocks. routing resources and I/O pads. This measure may be a simple cell count of technology specific elements required for the implementation. The time of an implementation is made up of two parts, the critical path and the number of clock cycles required to complete one computation of the implemented algorithm.

The critical path of a synchronous circuit dictates the maximum clock rate at which the circuit will correctly function. The critical path is the maximum D-type flip-flop (DFF) to D-type flip-flop logic delay time. This logic delay is made up of logic element propagation delays, routing delays and set-up and hold times on the DFFs. The logic element delay for each component is dependent on the output loading for that element. A higher number of loads means that a higher total current is required from the driving point, also each load and wiring element adds capacitance to the output of any element. The combination of this load current requirement and the load capacitance dictates the time required to drive a node to the required state.

The AT product of IC is the area (cell count. mm<sup>2</sup>) multiplied by the critical path length (time) multiplied by the number of clock cycles to process one input sample.

#### **1.3** Architectures

The architecture of any system defines a set of rules or principles which guide the design and functionality of anything created using that architecture. For instance Roman architecture brings to mind columns of stone and archways while. Egyptian architecture brings to mind sand-stone blocks and hieroglyphs. In a similar way the architecture of a digital signal processor can be defined. In the DSP domain the parameters of the architecture include the number format used to store a number. the word format used in data transfers, the number of bits used to represent each word and the number. type and interconnection of computing resources.

#### 1.3.1 Number Formats

The number format refers to the particular digital representation of numbers used by a given DSP architecture. The number format dictates the operations necessary to perform arithmetic operations and causes some arithmetic operations to be simpler at the expense of causing other operations to be more difficult to perform. The number format, together with the number of bits used to represent a value, also controls the range of values which can be represented.

In most number formats the value of a number is broken down into a series of digits. each digit taking on a range of values. having a weighting factor associated with it according to the digit significance. In the decimal representation each digit takes on one of 10 values and the weight for each digit is  $10^n$ , where n is the digit number (starting from zero). In the computer world a digit weighting of 10 is not practical so a binary number system is used. Here each digit takes on one of two values which are commonly referred to as 1 and 0 or high and low. A common number format for the representation of binary number is Two's Complement (TC).

In TC the weighting for each binary digit is  $2^n$  where n is the digit number. with the Most Significant Bit (MSB) having a negative weighting. The decimal value of an N bit TC number is given in equation 1.1. An N bit TC number can represent numbers from  $-2^{n-1}$  to  $2^{n-1} - 1$ .

$$x = -2^{n-1} * j_{n-1} + \sum_{i=0}^{n-2} j_i * 2^i, j_i = 1, 0$$

(1.1)

Another number format is the Canonic Signed Digit Format (CSD) [LEL91]. Each digit of a CSD number can take on one of three different values 1, -1 and 0, so this number format is a ternary system. Since computers are by their nature binary. two binary bits are required to represent each single bit of a CSD number. This results in poor storage properties for CSD numbers but for representing fixed coefficients this number format has some advantages over other systems. Since several redundant forms exist for each number, the designer may choose the most suitable one for a given application, resulting in reduced area or increased speed. The value of a CSD number can be calculated using equation 1.2.

$$x = \sum_{i=0}^{n-1} j_i * 2^i, j_i = 1, -1.0$$

(1.2)

Another number format commonly used in computer systems is floating point numbers. Here each number is broken into an exponent (exp) and a mantissa (man). The value of the floating point number is  $man * 2^{exp}$ . Both the mantissa and the exponent may be positive or negative resulting in a dramatic increase in dynamic range over a fixed point system. The number of bits used to represent the mantissa and the exponent are chosen to obtain the desired accuracy and dynamic range.

Other number systems such as the Residue Number System (RNS) [SJJT86]. Logarithmic Number System (LNS) [Lew93], and the Symmetric Level Index (SLI) [CT88] are used in computing machines. Each of these number systems has unique properties which can be used to combat shortcomings in other number systems such

7

as long carry paths. expensive multiplication and division, or small dynamic ranges. While these number systems are useful, the number systems used in this thesis are TC and CSD. TC and CSD are chosen for their simple integer number representation and their relatively small operator size.

#### 1.3.2 Word Formats

Another architecture parameter of a DSP system is the format in which each word of data is stored or transmitted from one component to another. The most common format. used in most computers and DSP chips. is full parallel. In this format the N bits of a data word are transmitted in parallel on N different wires. during one cycle of the system. The primary advantage of the parallel format is the speed of transmission. one data word per system cycle on each data bus. However the parallel transmission of data leads to several disadvantages.

The N bit result of each operator is also computed in parallel resulting in separate processing elements for each bit of the output data word. For some arithmetic operations information from the generation of one bit of output must be used in the computation of the next bit of output. This carrying or rippling of information from one computation to the next leads to long computation times for the completion of one parallel output word. This computation time or propagation delay can be reduced by using methods such as carry look ahead [Ann86] which shortens time to calculate the full parallel result but also results in larger circuit area for the computational unit. Another method to shorten the propagation delay through an operator is pipelining the operator so that a result is only partially completed on each clock cycle. This results in shorter propagation delays but requires more clock cycles to generate the full result.

The N bits of a parallel data word also lead to large data buses which are difficult to route and consume a large amount of integrated circuit area. This large routing requirement often results in large pin counts for an integrated circuit and low utilizations for semi-custom devices in which the routing resources cannot be tuned to meet the requirements of a particular design.

Bit-serial architectures have been proposed to create high performance. low cost VLSI implementations of DSP applications [DR85. Joh92. NT91. Erc84]. In bit-serial an N bit data word is transmitted on a single wire, one data bit per clock cycle. The word can be transmitted in the Most Significant Bit (MSB) first format [Erc84] or in the Least Significant Bit (LSB) first format [DR85. Par91. PM89]. The MSB first format is most suitable for operations such as division. square-root and sorting since these operations are naturally performed from MSB to LSB. The LSB first format is best suited for addition and multiplication since information is propagated from LSB to MSB in these operations. In most bit-serial systems only one of these formats is used at the periphery of each computational block but may be converted to the appropriate form within each operator.

Another advantage of the bit-serial architecture is the reduced routing requirements. Communication between operators is done using only a single wire, while in a parallel architecture N wires are needed. This results is less area overhead for routing, higher design routability and utilization for semi-custom technologies and reduced pincounts for integrated circuits designed using the bit-serial architecture.

Bit-serial operators are N times smaller in size than the parallel version of the same operator. The penalty for this size advantage is the processing time, bit serial operators are N times slower than a parallel operator (as defined without carry logic). If the two systems were operating at the same clock rate they would be equally efficient in terms of area-time (AT) product. However the propagation delay through a bit-serial component is 1/Nth of that for the parallel component, so the maximum clock rate permitted in a bit-serial system is higher than in a parallel system. Thus when the maximum clock rate is considered bit-serial systems have a better AT product than parallel systems [HC90].

Digit-serial [HC90] is a word format in which each fixed precision data word is transmitted on W (Digit-Width) different wires, the total word being divided into N/W=P separate digits. For many architectures there must be an integer number of digits in each data word, this restriction is not necessary but results in simpler control structures for the overall system. As W approaches full parallel the routing resources, operator size and latency increase, while the number of clock cycles required to complete one full computation decreases.

#### 1.4 Synthesis

Over the last few decades rapid developments in integrated circuit technology have made possible the integration of larger and larger electronic systems. In order to support this growth in complexity new design methodologies and more sophisticated Computer Aided Design (CAD) software tools have been required. Initially this CAD software focused on design verification through simulation, but starting in the late 1970's CAD software began to take over some of the design tasks traditionally done by hand. The various types of automation and the resulting effects on design

Figure 1.1: Time Line

time are shown in figure 1.1 taken from [MLD92].

Over the years design automation advancements such as automatic placement and routing, hierarchy generators and logic level synthesis have reduced design time considerably. At present the next generation of automation software is concerned with high-level or system level synthesis. These CAD tools will automatically convert a high level description of an algorithm or even a specification of an algorithm to a final IC implementation.

The use of high level or system level synthesis results in shorter design cycles and reduced time to market for integrated circuits. This occurs because of increased designer efficiency and fewer design errors since many of the error-prone steps of the design have been replaced by automated tools.

Figure 1.2: Y-chart

#### 1.4.1 Y-Chart

When discussing synthesis issues it is useful to refer to a Y-chart introduced by Gajski and Kuhn in 1983 [GK83] as shown in figure 1.2. In a Y-chart, a design is represented in three different domains, the behavioural, the structural and the physical domains. The behavioural domain is used to describe the behaviour of a system without any notion of how the behaviour is implemented. In the structural domain a circuit is represented by a hierarchy of functional elements and their interconnections. In the physical domain a circuit becomes a layout without any reference to functionality.

The various rings of this chart indicate different levels of abstraction for the circuit with the outermost ring being the most abstract and the innermost ring being the most specific. The innermost level is referred to as the circuit level. at this level of abstraction the structural elements are transistors, resistors and capacitors. The

12

behaviour of these elements becomes a set of differential equations relating currents and voltages for each component. The next level of abstraction is referred to as the logic level, in this level the entire circuit is composed of collections of transistors known as gates. The behavioural representation of this information is a set of boolean equations. The voltages and currents at the circuit level have been abstracted to the logical values true and false or 1 and 0.

At the next level of abstraction the logical values have been grouped into words of data. The structural elements which make up this level are collections of gates such as adders, registers, Arithmetic Logic Units and multiplexers. This level of abstraction is referred to as the Register Transfer Level (RTL).

The next level of abstraction is referred to as the algorithmic level. At this point the behavioural description of a circuit is an algorithm or sequence of operations required to perform a given task. In the structural domain this corresponds to a collection of RTL components to form a processor or subsystem.

The highest level of abstraction is known as the system level. At this point the behaviour of a system is described only in terms of functionality. No notion of implementation is present. This corresponds to the complete system in the structural domain.

In the physical domain the various levels of abstraction correspond to ever larger polygons or blocks finally resulting in complete integrated circuits or connections of integrated circuits as on a Printed Circuit Board (PCB).

Y-charts can be used to define the various information conversions which may be required during a design, as shown in figure 1.3. The transitions on one axis of this chart are defined as refinement, abstraction and optimization. Any transition from

Physical/Geometrical Domain

Figure 1.3: Y-chart Transformations

the periphery of this chart to the interior. on any axis. is the process of refinement. and the reverse transition is abstraction. An arc whose head and tail are at the same level of abstraction describes an optimization. During an optimization the basic functionality remains the same but the design has been improved with respect to some cost factor such as speed or area.

The transition between different axes of this chart are defined as synthesis, analysis, generation and extraction. In synthesis a behavioural description is converted to the structural domain, this defines how a behaviour is to be implemented at any level of abstraction. The reverse process, analysis, converts structural information back to a behaviour. Analysis is generally used for design verification. The process of creating a layout from a structural description is defined as generation and the reverse process is an extraction. Extraction is also used during verification to examine

14

the effects of routing delays and signal loading on the performance of the system.

#### 1.4.2 Silicon Compilation

The ultimate goal of a synthesis system is to convert a system level specification in the behavioural domain to the lowest level representation in the physical domain. Any software tool which can perform this conversion can be called a silicon compiler. In practice this task can not be carried out in a single step but is broken down into several smaller synthesis. optimization and generation steps. There are several different ways to break this design process down into steps, one possible method is described below.

The first step in this process is system level synthesis. This process converts a system level specification to a set of algorithmically defined subprocessing modules. On the Y-chart this operation combines a behavioural refinement and a synthesis operation. Each of these subprocessing modules executes in parallel to perform the desired algorithm. The input specification consists of a function to perform, such as a digital filter transfer function or a computer instruction set and a set of constraints on the solution such as the desired speed, size and power consumption for the final solution.

The next step in the design process is to convert the algorithmic description of the system to an interconnection of realizable processing elements or high level synthesis. On the Y-chart this operation may combine a refinement in either the behavioural domain or the structural domain with some synthesis. The input to this stage is algorithms defined in terms of processing elements such as adders. multipliers. control structures such as branches and loops and storage elements. The output from this stage of synthesis is a structural Register Transfer Level (RTL) design containing adders, multipliers, control structures and registers. This RTL level design may be a shared resource implementation where each operator within the design may perform two or more different operations during the algorithm computations. This synthesis step is often broken down into three major portions which are resource allocation. scheduling and resource assignment.

In resource allocation a set of functional units which will perform the required processing steps is selected. The resource assignment phase assigns each algorithm operation to one functional block made available by the resource allocation operation. The scheduling step assigns time steps to each operation on each functional resource. This synthesis operation has been addressed by several software programs. such as HAL (Force Directed) [PK87]. SPAID [HE89]. MAHA [PPM86]. SE (Simulated Evolution) [LM90], SAVAGE [ND90]. BITSYN [NT91] and SNAFU [Joh92]. Each of these programs searches the design space and attempts to find the most suitable design, given the user constraints and an estimate of area-time characteristics of each function unit available to the synthesis system.

The RTL description must now be converted to a gate level description using RTL synthesis. This process converts the functional units (behavioural/structural) which have been allocated and scheduled to gate level implementations (structural) containing simple gates and storage elements. In doing this, some knowledge of the implementation architecture is required in order to generate the most effective implementation possible.

Finally the logical descriptions are converted to collections of gates and storage elements, representing the cells or primitives available within the final implementation technology. The objective here is to obtain the most appropriate technology specific representation for each logical operation, minimizing area and/or time delay for each block. This step can be carried out early if the RTL description is converted directly to a technology dependent format. After the circuit has been mapped to technology specific cells the design is placed and routed. This operation attempts to find the optimal placement for each cell of the design which will minimize the routing area and delay for each interconnection in the circuit. Finally all the interconnections in the design are routed using the available area or routing resources in the device. The design is now ready for fabrication as required by the implementation technology.

#### 1.4.3 Validation

The design of complex digital circuits is inherently an error prone process. Even with the use of CAD tools the resulting circuits are not guaranteed to be functionally correct. In order to deal with this problem it is important to use validation software which checks the results of a design step to make sure the circuit functions as intended. There are basically two different methods of validation. formal methods and simulation.

In formal methods the transformations applied at each stage are proven to be correct and maintain functionality. If all circuit transformations are proven to be error free then the final circuit will function as specified. In formal methods it is critical to correctly specify the operation of the system and to be certain that the proofs are complete.

In simulation a set of test inputs or test vectors are applied to the input(s)

of a circuit. the outputs are examined against the expected results and if they are consistent then the circuit is functioning correctly. The difficulty here is in identifying the correct set of test vectors which will exercise all circuit components to reveal any flaws. In simulation it is critical to understand input/output signal requirements from a circuit under test, any deviation between this understanding and the real world circuit requirements will render the simulation invalid.

Just as there are several levels of abstraction for a design there are also several levels of simulation and design verification. As each level of synthesis or refinement is applied, the results are checked with an ever more detailed simulator or formal proof. requiring longer and longer run times as the design is refined.

#### 1.5 Research Goals

The objective of this research is to generate a CAD tool which will automatically convert an RTL behavioural description of a DSP application to a structural digital logic circuit containing logic elements. D-type flip-flops and technology specific elements. The target implementation technologies will include gate arrays, FPGAs and full custom implementations. The CAD tool should be flexible enough to support new architectures with a minimum of changes to the CAD tool itself. The target applications for this compiler are low to medium (up to 2 MHz) throughput rate digital filters and other DSP applications which are dominated by additions and multiplications. For the input/output specifications an architecture which utilizes a bit-serial or digit-serial (reduced routing), TC fixed point word traveling in the LSB first format (additions and multiplications) will be used. The compiler will convert a RTL behavioural description, defined in the DFIRST language which is an extension of the bit-serial language FIRST [DR85], into a gate level structural description. This process is performed by synthesizing the behavioural RTL description into a structural gate level description. A series of appropriate optimizations are then applied to obtain a technology specific gate level implementation for the DSP application.

The output of this compiler must be easily retargetable to deal with the ever expanding set of new technologies and new data formats. In addition the circuit generated should be reasonably optimal for the chosen implementation technology to justify the use of the compiler. The final generation stages of the overall design procedure, placement and routing, will be performed by vendor supplied software tools for each implementation technology.

In order to reduce design time for the final implementation several analysis steps should be used to verify the correctness of each refinement or optimization step. A separate simulation program, DSIM (Dfirst SIMulator), will be created in order to perform RTL simulations, presently available logic simulators will be used to perform unit delay gate level simulations. Finally, extraction software supplied by the implementation technology vendor can be used to extract the wiring delays for final timing verification.

#### **1.6 Overview**

In the following chapter the DFIRST architecture specifics as well as language syntax are presented. In addition the DSIM RTL simulator for the DFIRST language is discussed and the input/output format is presented. In chapter 3 the RTL hardware elements which make up the DFIRST language are presented. In particular the architecture for DFIRST adders. multiplers. bit shifters and format conversion operators is given.

In chapter 4 the TRANS gate compiler which can convert DFIRST to technology specific gate level implementations is presented. In particular the set of refinements and optimizations which can be applied to the circuit in order to obtain a smaller. more efficient design is discussed. In chapter 5 several examples which have been generated and tested using DFIRST. DSIM and TRANS are given. Finally in chapter 6 some conclusions on the DFIRST language and TRANS are presented. In addition some possible avenues for future research are explored.

### Chapter 2

## **DFIRST Language and Simulator**

This chapter presents the DFIRST register transfer level digit-serial hardware description language. The DFIRST data word format and control signals are discussed and the DFIRST language syntax is presented, including operator instantiation, hierarchy, signal declarations, chip to chip communication, and constants. In addition the DSIM simulator is discussed including input/output data formatting and simulation error reporting.

#### 2.1 DFIRST Architecture

In a binary data DSP environment, operations are performed on N bit words of digital data. This data can be transmitted in a number of formats. The most common format is bit parallel, in which all N bits of the word are transmitted simultaneously on N different wires. The disadvantages of Parallel architectures are that large amounts of chip area are required for operator implementation and routing and that parallel operators have long propagation paths <sup>1</sup> leading to a reduced maximum operating clock frequency. Alternatives to word parallel data transmission are bitserial or digit-serial formats. In bit-serial the N bits of a data word are transmitted on a single wire in N clock cycles. This leads to operators which are typically N times smaller than parallel versions of the same operator but require N times more

<sup>&</sup>lt;sup>1</sup>Look-ahead-carry techniques lead to reduced propagation delays but require more hardware.

Figure 2.1: Sample DFIRST DataWord

clock cycles to complete the transmission of one data word.

In digit-serial architectures the N bit data word is divided into P separate digits. each W bits wide. For the DFIRST architecture. N must be equal to W<sup>\*</sup>P. That is. there must be an integer number of digits in each data word. This restriction is not required in general. but the control circuitry is much simpler when all data words are divided into an integer number of digits. Since the data for each word takes several clock cycles to propagate along a given data path. a word framing control signal indicating some fixed point in the data word is needed. In the DFIRST architecture a control signal indicating the Least Significant Digit (LSD) time of the data word is used. as shown in figure 2.1. For some operations in DFIRST a Most Significant Digit (MSD) indicating signal may also be required to completely frame a given data word.

Each operator within DFIRST is pipelined at the digit level, resulting in a short

22

propagation delay through any logic elements and a higher potential operating frequency for the overall system. Each operator has a latency(L) which is the number of bit or digit clock cycles required to generate the LSD of the output signal(s), after the arrival of the input signals. The LSD of each input to an operator must arrive and be valid during the same clock cycle in order to assure correct operation.

The iteration time for a serial algorithm is defined as Q, the number of clock cycles required for one complete iteration of the algorithm. Some pipelining latency may occur between the arrival of the first input and the completion of the first output signal but the system can accept a new input every Q clock cycles. The Q of an algorithm is dictated by the minimum number of clock cycles required to update all internal states in a recursive system. If all of the operations within the DSP algorithm are implemented on dedicated resources then the resulting serial circuit will exhibit the minimum Q possible for that system with the given operator set.

In practice a more area efficient implementation can be obtained by sharing physical components between the various operations within an algorithm. This requires the multiplexing of large components such as multipliers and dividers, and results in a larger iteration time (Q) but can result in significant area savings. For some applications the optimal area-time product measure exists within a shared resource environment [NT91, Joh92, Nag91].

A generic DFIRST operator is shown in figure 2.2. Each operator requires several input and output signals which may be bit-serial, digit-serial or parallel depending on the particular operator. As well, several parameters may be required to specify the exact nature of the operator, these parameters may include for example digit width, data wordlength, coefficient wordlength and latency. Each primitive will

Figure 2.2: Generic DFIRST Operator

exhibit a latency which is dependent on the parameter settings for that element. this latency(L) is recorded in the small box before each of the output signals. Each output from a primitive usually has the same L but this may not be the case for all operators.

#### 2.2 Design Example

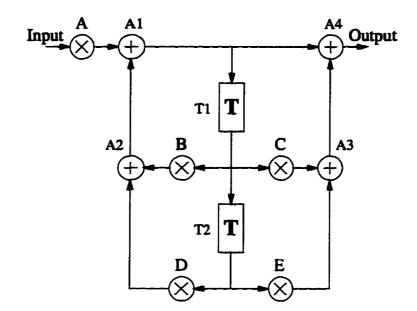

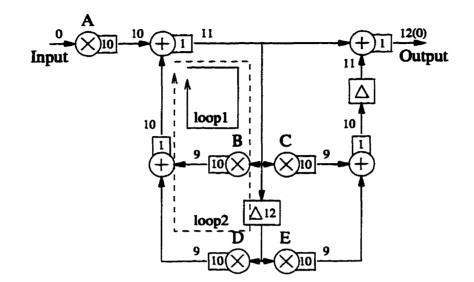

The Signal Flow Graph (SFG) for a biquadratic [Jac89] digital filter is shown in figure 2.3. For this example let W=1 (bit-serial) and assume that the latency of each of the five multipliers is 10 and that the latency of each of the four adders is one. In any serial circuit it is useful to label a single point as reference time zero. which means that the LSD of the signal at that point is valid at time zero. For this filter

Figure 2.3: Biquad Digital Filter Flow Graph

let the input signal be the reference point. The final bit-serial circuit. complete with timing information. is shown in figure 2.4.

From figure 2.4, where the LSB times for each signal are shown, it can be seen that the minimum time required to compute each of the state variables is twelve clock cycles as found in loop1, this time is the Minimum System Wordlength (MSW) of the system. It is interesting to note that the first delay element T1 is not implemented as a separate element but is distributed through multipler B and adders A1 and A2. The second delay is implemented using a one-wordlength long shift register. So for this circuit, using these primitives, we find that Q=12 and that the LSD of the first output is completed at time twelve.

Figure 2.4: Bit-Serial Implementation of Biquad Filter

# 2.3 DFIRST Language Parameters

The DFIRST language is based on the FIRST (Fast Implementation of Real-time Signal Transforms) hardware description language developed by Denyer and Renshaw [DR85]. This language was used as a RTL description language for bit-serial systems. Denyer and Renshaw also developed a simulator (simfirst) for use with the language in order to facilitate rapid design and testing of FIRST descriptions. The language also included a compiler (fcc) which converted the high level FIRST language into a full custom NMOS IC implementation. In order to develop DFIRST several additions were made to this FIRST language.

The DFIRST language fully supports not only bit-serial architectures (W = 1)but also digit-serial architectures (N > W > 1) and parallel architectures (W = N). It is also possible to mix digit widths within a single design. The language supports elements which have a latency of zero clock cycles, such as simple gates. in order to allow greater flexibility when designing serial circuits. Several new primitives such as CSD multipliers, parallel to serial and serial to parallel converters and conditional operators are also included to increase the range of possible applications.

# 2.3.1 Signal Declarations

In any hardware description language, information is transferred from operator to operator with signals or variables. Each signal can have a variety of parameters attached to it. defining the precision or format of the information contained in the variable. In the DFIRST language each signal must have a digit width which defines the W of the signal. Each signal also requires a flag indicating whether the information is serial or parallel in nature. This is required because the timing constraints on the two types of signals are different. Each signal must also be defined as either a control signal containing timing information or a data signal containing processing information.

The SIGNAL command is used to declare each data signal in the system. Several different styles of signal declarations are available, these are shown in table 2.1

From table 2.1 it can be seen that the THROUGH and \* signal modifiers are equivalent in DFIRST and can be used to flag a signal as being parallel. The default digit width is adjusted using the DIGIT command which must be at the top of the DFIRST file. For example, to set the default digit width to two for a whole system. the compiler directive 'DIGIT 2' should be on the first line of the DFIRST file. The signal orientation which indicates whether the most significant bit is the smallest or largest bit number is not presently adjustable. The default setting in this case forces the MSB to be the smallest bit number in both serial and parallel signals.

| Signal Declaration | Meaning                                            |  |  |  |  |

|--------------------|----------------------------------------------------|--|--|--|--|

| sig                | A digit-serial signal of the default width.        |  |  |  |  |

| sig0 THROUGH n     | Define an $n+1$ bit wide parallel signal. The sig0 |  |  |  |  |

|                    | signal is the Most Significant Bit (MSB) of the    |  |  |  |  |

|                    | bus.                                               |  |  |  |  |

| sig[0:n]           | An n+1 bit wide digit-serial signal. The sig0 sig- |  |  |  |  |

|                    | nal is the MSB of the digit.                       |  |  |  |  |

| sig[n:0]           | An n+1 bit wide digit-serial signal. The sign sig- |  |  |  |  |

|                    | nal is the MSB of the digit.                       |  |  |  |  |

| *sig[0:n]          | The * signal modifier may be used to set a sig-    |  |  |  |  |

|                    | nal to be parallel. This is equivalent to the      |  |  |  |  |

|                    | THROUGH signal type from above.                    |  |  |  |  |

| sig[n]             | n bit wide digit serial signal.                    |  |  |  |  |

Table 2.1: Possible DFIRST signal Declarations

This bit order can only be over-ridden by exactly specifying this information using the sig[MSB:LSB] signal declaration.

For the most part DFIRST can accept any alphanumeric strings as signal names. there are no restrictions on the length of names, and numbers can be used in the names but not as the first character. There are however some reserved signal names which must be avoided. These include the 'VDD' and 'GND' signals which are used to tie inputs high or low respectively, and the 'NC' (no-connect) pin which is used as a place holder in situations where a signal is generated but is not used. Also, signal names cannot start with the character 'X' as this is used to specify a hexadecimal fixed value signal.

The control signals can be declared using the CONTROL signal type instead of the SIGNAL construct introduced earlier. There are in general two different sorts of control signals, LSB/MSB indicating signals and word selection signals. The LSB/MSB indicating signals are used to frame serial data words and are high for only one clock cycle per data word. Word selection signals are used for data steering and are high or low for one or more entire data words. There is no difference in the declaration of these two different types of control signals.

# 2.3.2 Hierarchy

One way of reducing the complexity of a system. is to break the overall operation down into a hierarchy of simpler operations. In doing this, the task performed by a system is broken down into convenient sub-modules which do a portion of the overall processing. Each of these sub-modules can be broken down into even smaller portions resulting in further simplification. The use of hierarchy not only reduces design complexity but also increases design re-usability. It is very difficult to re-use a complete system in a new project but a sub-module which performs a generic task can easily be re-used, or modified for re-use, resulting in reduced design times for future projects.

The five hierarchical levels within DFIRST have been retained from the original FIRST language and include the SYSTEM. SUBSYSTEM, CHIP. OPERATOR and PRIMITIVE levels. The SYSTEM level represents the entire system which performs the processing task. a CHIP represents a single integrated circuit and the PRIMI-TIVEs are pre-designed components available within the DFIRST language. Each of these three hierarchy levels cannot make use of components at the same level. so a CHIP cannot contain another CHIP within itself. The other two levels of hierarchy are provided to facilitate partitioning. A SUBSYSTEM is a collection of CHIPS and other SUBSYSTEMs, and an OPERATOR is a collection of PRIMITIVEs and other OPERATORs.

#### 2.3.3 Instantiation

To instantiate an operator of any hierarchical level the following syntax is used:

#### label: name [parmlist] (cntrllist) datalist

The *label* is an optional feature which allows the user to name an individual component for future reference. if no label is present then a unique label is generated by the program reading the DFIRST netlist. The *name* defines the type of operator being instantiated. the *parmlist* contains user defined parameters specific to each operator. The *ctrllist* contains all the control signals for the operator, and the *datalist* contains all the data signals for the operator. For the *cntrlist* and the *datalist* the inputs and outputs are separated by an arrow (- >). For example a serial adder could be instantiated as follows:

ADD [1,0,0,0] (c0) a0,b0,GND -> s0,NC

In this example the label for the adder is not included so one will be generated by the program reading the netlist. Information on what the parameters, and I/Osignals for this operator are discussed in chapter 3.

#### 2.3.4 Encapsulation

In order to encapsulate a set of operators within a hierarchical element the following syntax is used:

```

hierarchy name (ctrllist) datalist

CONTROL ctrlsignals

```

# SIGNAL datasignals instancelist

END

The first line of the hierarchical element, or macro, defines the hierarchy level. the reference name and the input/output signals for the part. The *hierarchy* must be one of the four non-primitive hierarchical types SYSTEM, SUBSYSTEM, CHIP or OPERATOR. The *name* can be any alphanumeric string which does not conflict with a PRIMITIVE name, previously defined element or DFIRST keyword. The *ctrlist* contains a listing of control inputs and control outputs with the inputs and outputs being separated by an arrow. The *datalist* contains a list of all data signal inputs and outputs, again with the I/O signals being separated by the arrow.

The internal portion of the macro defines the behaviour of the element. The *ctrlsignals* list contains a listing of all internally defined control signals separated by commas. The *ctrllist* signals must not be included here and no arrow separator is required to define input and output signals. The *datasignals* list defines the internal data signals. If the signal lists are too long the line can be continued by ending one line with a comma and continuing the signal declarations on the next line. In addition any number of CONTROL and SIGNAL commands may be present but they must occur before the *instancelist* begins.

The *instancelist* is a sequence of components which describe the functionality of the macro. The elements of the *instancelist* are instantiated as shown in section 2.3.3. There are some limitations on the components which can be used within a macro depending on the hierarchy level of the operator. Only PRIMITIVEs and OPERATORs can be used within OPERATORs and CHIPs, and only CHIPs and SUBSYSTEMs can be used within SUBSYSTEMs and SYSTEMs. In all cases a recursive definition is illegal, so no instances of *name* can be contained within the macro description of *name*.

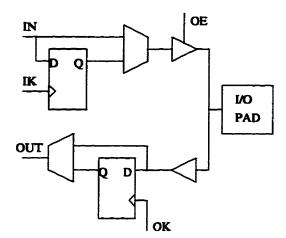

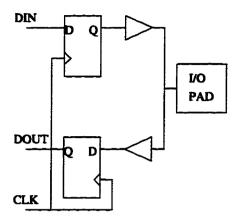

#### 2.3.5 I/O Pads

The input-output pads of an integrated circuit perform the important function of buffering signals from the chip internal environment to the chip external environment. They are used to provide sufficient drive for system level signals and to provide static and overdrive protection for each I/O signal. In a synchronous system simple buffering of I/O signals is not sufficient in a multi-chip environment, due to the phase difference or clock skew between different devices. Clock skew is caused by differing propagation delays for a clock signal arriving at two or more different points. Since clocks are active on edges only, a small skew can cause a circuit to fail. In order to correct for this problem. D type flip-flops are inserted on both the input and output pads, with the input pads being rising edge triggered elements and the outputs being falling edge triggered elements. This configuration allows for a combined clock skew and signal delay of up to one half of the clock period, in either direction [DR85].

The I/O pads within FIRST are only included at the CHIP level of the language and cannot be used at any other level of the DFIRST hierarchy. The I/O pads are instantiated using two DFIRST commands, PADIN for input pads and PADOUT for output pads. The syntax of these commands is as follows:

PADIN (extern\_cntrl->intern\_cntrl) extern\_data->intern\_data PADOUT (intern\_cntrl->extern\_cntrl) intern\_data->extern\_data The *extern* signals represent chip external signals and the *intern* signals are the chip internal versions of the external signals. A buffer of the appropriate type (in-put/output, rising/falling edge triggered DFF) will exist between the external and the internal signal. The PAD commands must be placed between the signal declaration section and the instance list of a CHIP level macro.

#### 2.3.6 Constants

Many of the primitives within DFIRST are parameterized in terms of wordlength. precision and latency. Often one change in system specifications such as the system wordlength or coefficient wordlength results in a drastic change in the parameter settings and the bit level timing for all elements in the system. CONSTANTs can be used to shorten the re-design time when high level system parameters are changed.

A CONSTANT is a string which is given a numerical value made up from other constants and numerical operations such as addition and multiplication. The possible integer arithmetic operations are addition, subtraction, multiplication and division. Brackets are also supported. The evaluation order for CONSTANTs is brackets, followed by multiplication/division and finally addition/subtraction. A CONSTANT is defined using the following syntax and must be defined before it is used within the DFIRST code. A CONSTANT can be used in any parameter location. In the following example the CWL constant is set to eight and the LATENCY constant is set to 13.

CONSTANT CWL=8

#### CONSTANT LATENCY=3\*CWL/2+1

# **2.4 DSIM**

For any high level language it is important to have an effective simulation program to aid in the design process. A register transfer level simulator models the behaviour of the language elements at the RTL which results in fast simulation times as compared to lower level simulations (gate level or transistor level). In order to be effective, a high level simulator should include a comprehensive design rule checker to highlight as many design faults as possible at an early stage so that fewer time consuming runs of a lower level simulator are necessary. A simulator should have an effective data entry system in order to speed up the circuit debugging and finally a simulator should be as fast as possible so that the designer does not spend an undue amount of time waiting for a simulation. The RTL simulator for the DFIRST language is the DFIRST Simulator or DSIM.

DSIM is an event driven simulator which models each data signal as a fixed point N bit integer. with a time value to indicate when that signal became valid (LSD time). The primitive functions are performed on the integer values and the time values are used to verify timing constraints on each signal.

#### 2.4.1 Signal timing

The time steps within the simulator are broken down into two different components. the bit time and the gate time. The bit time represents the clock cycle at which a signal becomes valid. The gate time is a finer scale time which accounts for the delay time through a component which has a zero clock cycle latency. For most DFIRST components the bit time is all that is needed because most primitives have a latency of at least one clock cycle. However some DFIRST components, such as simple gates and zero delay adders and multiplexors, have a latency of zero clock cycles. For these components the gate level timing is needed during simulation. Each clock cycle is broken down into 20 gate ticks, and the latency of any zero delay component is set to one gate tick. Any combination of zero delay elements must generate a final value within this time or the simulation will generate incorrect results. This set of delays does not reflect routing delays or even real component delays but does allow for correct unit delay simulation, which is necessary at early stages in the design process. For more exact simulations, with more realistic logic delays, a gate level timing simulator must be used.

The gate level simulation portion of DSIM uses the transport delay model [Vie93]. which simulates every transition even those which may be only one gate tick wide. An alternative strategy is inertial delay modeling which effectively filters any transition which is shorter than or equal to the delay through a logical element. The transport delay model results in slightly longer settling times for logical blocks but is simpler to implement.

#### 2.4.2 Parallel vs. Serial Signals

Most DFIRST primitives. such as ADD or MULT, have input/output signals which are exclusively serial in nature. Other primitives such as PTOSB and PMULT have inputs which must be in the parallel format. Within the simulator both signal types are treated the same in all respects except with regard to timing violations.

Each serial signal in a system travels in a LSD first format on W wires. The LSDs of all serial signals arriving at any operator must arrive at exactly the same time. If this is not the case a timing fault will be flagged and the user must correct the timing of these signals.

Parallel signals travel on N wires and once a parallel bus is given a value it will hold that value until a new value takes it's place. This holding feature on parallel signals means that the timing of parallel signals is not as critical to proper operation. The correct data on a parallel bus must be present on a parallel bus when the control signal which samples the bus arrives.

#### 2.4.3 Data File Format

In order to simulate a DFIRST netlist with DSIM the user must provide input stimulus information. which output signals are to be examined. the simulation duration and the data wordlength of the DFIRST system. This information is provided in the DSIM data file.

The WORDLENGTH command must be the first command in the DSIM data file. This WORDLENGTH value is used within the simulator to check overflows on all signals within the simulation. The command to set the simulation time frame is the SIMULATION CYCLES command. which indicates the number of data words to be simulated. The number of clock cycles in the simulation will be SIMULATION CYCLES \* WORDLENGTH. The syntax of these two commands is as follows for a data wordlength of 16 bits and a simulation duration of 100 data words (1600 clock cycles).

WORDLENGTH 16 SIMULATION CYCLES 100 The command for inputting data to the simulator is divided into two separate portions. the signal declaration and the signal simulation data. Since the input signals to a simulation may be serial in nature, a LSD time must also be provided with the data for the signal. This timing information is added using the SIGNAL command which uses a signal within the simulation, which has known timing properties. to define the LSD time for input signal(s). In the following example the signals *ain* and *bin* will have the same LSD time as the simulation internal signal *c0*.

#### SIGNAL ain, bin SYN WITH cO

The synchronizing signal may be a control signal or a data signal, chip internal or chip external but generally a system level (chip external) control signal is used for this purpose since the input data signals are usually chip external.

The simulation data is provided using the *inputsignal* command. Where an *inputsignal* is any signal name declared using a SIGNAL command in the data file. Data is provided as a set of ordered pairs of numbers. the first number is the word time and the second number is the data value. The word time is defined in terms of the synchronizing signal for this *inputsignal*. A word time of zero means that at the first occurrance of the sync signal this input signal should take on the value indicated by the data value for word time zero. Each LSD occurrence of the sync signal increments the word time. Any word times which are not present will maintain the previous setting of the data value. The data ordered pair list must be terminated by either a -1 or a -2 value. A negative one value means that this *inputsignal* should maintain the same signal value (the last data value specified) until the end of the simulation. a negative two value means that the pattern of the data should be repeated

from the first value in the order pair list. In addition a separate file which contains the data for the signal can be included by using the FILE construct, the format of the data file is the same as the standard data style. The examples presented here illustrate the data format, the data terminators and the FILE command.

Example 3

# [sigc] FILE sig.in

In Example 1 the value of the signal sign follows the sequence 1, -1. 4. -5, -5, 8, 0. During time 4 the value of the signal remains as in the previous time and at any time after time 5 the value of sign is 0. In example 2 the value of sign has a repeating sequence of '0,1,4.8' for the duration of the simulation. In the final example the file sig.in contains the data for the sigc input signal. The format of the sig.in file is the same as the standard input data.

The WATCH command is used to observe data signals during the simulation. The WATCH command specifies which signals are to be observed during the simulation and the name of the file in which to store the information. Any simulation signal can be WATCHed and the timing granularity for the output information can be set to either GATE, BIT or SAMPLE format.

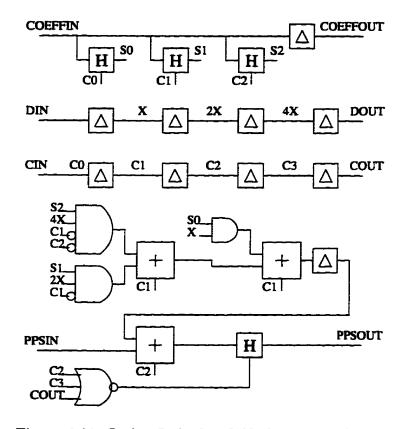

If the BIT level format (default) is used then the timing information for all signals generated within the simulation will be the clock cycle number. If the GATE level format is used then all BIT times will be scaled by the gate ticks parameter. At this timing level the performance of gate level combinational circuits can be observed. The final timing format is the SAMPLE format, here the timing for the output signal is word level information. In the SAMPLE format the timing information starts from zero and is incremented by one for each successive output value.