#### https://prism.ucalgary.ca

The Vault

Open Theses and Dissertations

2012-12-06

# A Computer-Aided Design Assistant Tool for Elementary Linear Circuit Topologies

# Shahhosseini, Delaram

Shahhosseini, D. (2012). A Computer-Aided Design Assistant Tool for Elementary Linear Circuit Topologies (Master's thesis, University of Calgary, Calgary, Canada). Retrieved from https://prism.ucalgary.ca. doi:10.11575/PRISM/24678

http://hdl.handle.net/11023/338

Downloaded from PRISM Repository, University of Calgary

#### UNIVERSITY OF CALGARY

A Computer-Aided Design Assistant Tool for Elementary Linear Circuit Topologies

by

#### Delaram Shahhosseini

#### A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

November, 2012

© Delaram Shahhosseini 2012

# UNIVERSITY OF CALGARY

# FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled "A Computer-Aided Design Assistant Tool for Elementary Linear Circuit Topologies" submitted by Delaram Shahhosseini in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE.

| Supervisor, Dr. Leonid Belostotski<br>Department of Electrical and Computer Engineering |

|-----------------------------------------------------------------------------------------|

| Department of Electrical and Computer Engineering                                       |

|                                                                                         |

| Co-Supervisor, Dr. Laleh Behjat                                                         |

| Department of Electrical and Computer Engineering                                       |

|                                                                                         |

| Dr. Sebastian Magierowski                                                               |

| Department of Electrical and Computer Engineering                                       |

|                                                                                         |

| Dr. Svetlana Yanushkevich                                                               |

| Department of Electrical and Computer Engineering                                       |

|                                                                                         |

| Dr. Xin Wang                                                                            |

| Department of Geomatics Engineering                                                     |

|                                                                                         |

|                                                                                         |

| Data                                                                                    |

| Date                                                                                    |

## Abstract

In this thesis, a CAD tool called analog design assistant (ADA), is developed to help analog circuit designers find new circuit topologies. First, a methodology to automatically generate all analog circuit topologies containing two or three transistors is developed. For each topology, circuit characteristics, such as DC voltage gain, are calculated. The DC voltage gain of each generated circuit is maximized by formulating and solving an optimization problem. After solving the optimization problem, it is shown that over 5,000 out of 56,000 circuits can achieve a DC voltage gain higher than 1. All generated circuit topologies and corresponding characteristics are stored in a database. A GUI is developed to help analog circuit designers search the database and find new topologies. In order to demonstrate the capability of ADA in generating new topologies, a previously unknown high-gain amplifier is selected, and designed in a 0.13-μm standard CMOS technology.

# Table of Contents

| $\mathbf{Abs}$   | ${f stract}$                                        | ii  |  |  |  |  |  |

|------------------|-----------------------------------------------------|-----|--|--|--|--|--|

| Tabl             | le of Contents                                      | iii |  |  |  |  |  |

| List             | st of Tables                                        |     |  |  |  |  |  |

| List             | of Figures                                          | vi  |  |  |  |  |  |

| 1                | Introduction                                        | 1   |  |  |  |  |  |

| 1.1              | Motivation                                          | 1   |  |  |  |  |  |

| 1.2              | P. Thesis Contributions                             |     |  |  |  |  |  |

| 1.3              |                                                     |     |  |  |  |  |  |

| 2                | Analog Circuit Representation and Synthesis         |     |  |  |  |  |  |

| 2.1 Introduction |                                                     |     |  |  |  |  |  |

| 2.2              | Circuit Representations                             | 6   |  |  |  |  |  |

|                  | 2.2.1 Schematic Representation                      | 7   |  |  |  |  |  |

|                  | 2.2.2 Graph Representation                          | 8   |  |  |  |  |  |

|                  | 2.2.3 Netlist Representation                        | 9   |  |  |  |  |  |

|                  | 2.2.4 Matrix Representation                         | 10  |  |  |  |  |  |

| 2.3              | CAD-based Analog Circuit Synthesis and Analysis     | 14  |  |  |  |  |  |

|                  | 2.3.1 Previously known circuit topologies           | 14  |  |  |  |  |  |

|                  | 2.3.2 Generating new circuit topologies             | 17  |  |  |  |  |  |

| 2.4              | Optimization Applications for Circuit Synthesis     | 23  |  |  |  |  |  |

| 2.5              | Summary                                             | 26  |  |  |  |  |  |

| 3                | Proposed Systematic Hierarchical Methodology        | 27  |  |  |  |  |  |

| 3.1              | Introduction                                        | 27  |  |  |  |  |  |

| 3.2              | Circuit Representation                              | 28  |  |  |  |  |  |

|                  | 3.2.1 Connectivity Matrix Construction              | 29  |  |  |  |  |  |

| 3.3              | Circuits Generation Using a Connectivity Matrix     | 30  |  |  |  |  |  |

|                  | 3.3.1 2-transistor Circuits Generation              | 30  |  |  |  |  |  |

|                  | 3.3.2 Multiple Transistors Circuits Generation      | 36  |  |  |  |  |  |

| 3.4              | Theoretical Proof of Circuit Generation Methodology | 38  |  |  |  |  |  |

|                  | 3.4.1 2-transistor Circuits                         | 38  |  |  |  |  |  |

|                  | 3.4.2 3-transistor Circuits                         | 51  |  |  |  |  |  |

| 3.5              | Circuit Generation Results                          | 58  |  |  |  |  |  |

| 3.6              |                                                     | 60  |  |  |  |  |  |

|                  | 3.6.1 Circuit Optimization                          | 61  |  |  |  |  |  |

| 3.7              | Analog Design Assistant Tool                        | 65  |  |  |  |  |  |

| 3.8              | Summary                                             | 70  |  |  |  |  |  |

| 4                | Analysis and Design of Selected Amplifier           | 71  |  |  |  |  |  |

| 4.1              |                                                     |     |  |  |  |  |  |

| 4.2              |                                                     |     |  |  |  |  |  |

| 4.3              | Circuit Design                                      | 73  |  |  |  |  |  |

| -                | 4.3.1 Current Sources                               | 74  |  |  |  |  |  |

|                  | 4.3.2 DC controller                                 | 77  |  |  |  |  |  |

| 4.4  | Circuit Analysis                         |

|------|------------------------------------------|

|      | 4.4.1 Voltage Gain And Input Power Match |

|      | 4.4.2 Noise Analysis                     |

| 4.5  | Simulation Result                        |

| 4.6  | Summary                                  |

| 5    | Conclusions and Further Directions       |

| 5.1  | Conclusions                              |

| 5.2  | Contributions                            |

| 5.3  | Further Directions                       |

| Bibl | iography                                 |

# List of Tables

| 3.1 | The maximum number of configurations of connecting the $I/O$ and $C2T$                                      |    |  |  |

|-----|-------------------------------------------------------------------------------------------------------------|----|--|--|

|     | blocks for $configuration \ a, b \ \dots \dots \dots \dots \dots \dots$                                     | 50 |  |  |

| 3.2 | The maximum number of configurations of connecting $I/O$ and $C2T$ blocks                                   |    |  |  |

|     | for $configuration \ c \dots \dots \dots \dots \dots \dots \dots \dots$                                     | 51 |  |  |

| 3.3 | The number of generated 2-transistor circuits                                                               | 59 |  |  |

| 3.4 | The number of generated 3-transistor circuits                                                               | 59 |  |  |

| 3.5 | The initial points for optimization problem                                                                 | 62 |  |  |

| 3.6 | The number of optimized 2-transistor amplifiers                                                             | 62 |  |  |

| 3.7 | The number of optimized 3-transistor amplifiers                                                             | 62 |  |  |

| 3.8 | The small-signal transistor parameters and the circuit specifications of previ-                             |    |  |  |

|     | ously unknown amplifiers in Fig. 3.17                                                                       | 65 |  |  |

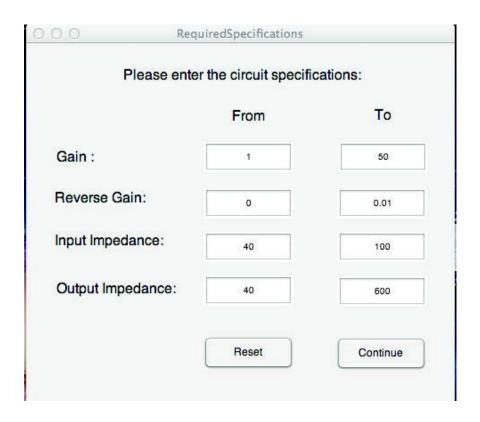

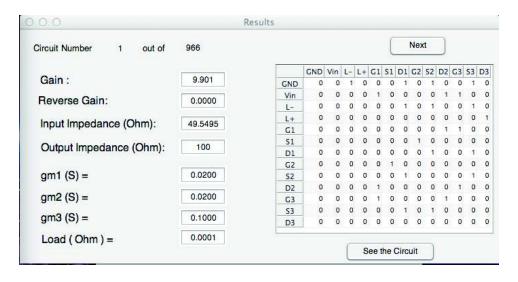

| 3.9 | An example of required small-signal specifications                                                          | 68 |  |  |

| 4.1 | The specifications of selected amplifier                                                                    | 73 |  |  |

| 4.2 | The comparison of ADA and Cadence results                                                                   | 84 |  |  |

| 4.3 | The value of $g_m$ and $g_{ds}$ for $M_1, M_2$ , and $M_3 \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 85 |  |  |

| 4.4 | The size of transistors in final schematic of Amp2                                                          | 85 |  |  |

# List of Figures and Illustrations

| 2.1  | The schematic representation of a circuit                                      | 7   |

|------|--------------------------------------------------------------------------------|-----|

| 2.2  | The circuit graph of circuit illustrated in Fig.2.1                            | 8   |

| 2.3  | The circuit netlist of circuit illustrated in Fig.2.1                          | 9   |

| 2.4  | The adjacency matrix representation for circuit illustrated in Fig.2.1         | 10  |

| 2.5  | The incidence matrix for the circuit illustrated in Fig.2.1                    | 11  |

| 2.6  | A radio receiver decomposed into three blocks                                  | 15  |

| 2.7  | The procedure of analog circuits synthesis described in [6]                    | 16  |

| 2.8  | A two-port network and its ABCD matrix                                         | 18  |

| 2.9  | A transistor is modelled as a VCCS                                             | 19  |

| 2.10 | Representation of two-port network with a MOS transistor by a graph            | 19  |

| 2.11 | The flowchart of circuit generations algorithm                                 | 20  |

| 2.12 | The 2-MOSFET wideband amplifiers generated in [26, 27] (biasing not shown)     | 21  |

| 2.13 | The evolved topology is located between fixed input and output terminals [29]. | 22  |

| 2.14 | The flowchart of simulated annealing algorithm                                 | 25  |

| 0.1  |                                                                                | 20  |

| 3.1  | Building blocks of an analog circuit.                                          | 28  |

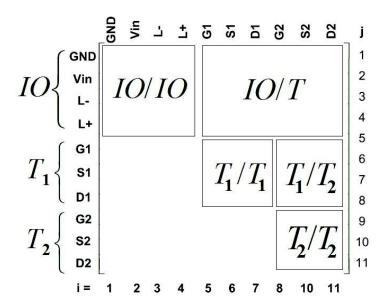

| 3.2  | The connectivity matrix, $CM$ , and the position of its sub-matrices           | 29  |

| 3.3  | An anolog circuit (biasing not shown) and corresponding connectivity matrix    | 30  |

| 3.4  | All possible $I/O$ block configurations                                        | 31  |

| 3.5  | All possible T block configurations                                            | 33  |

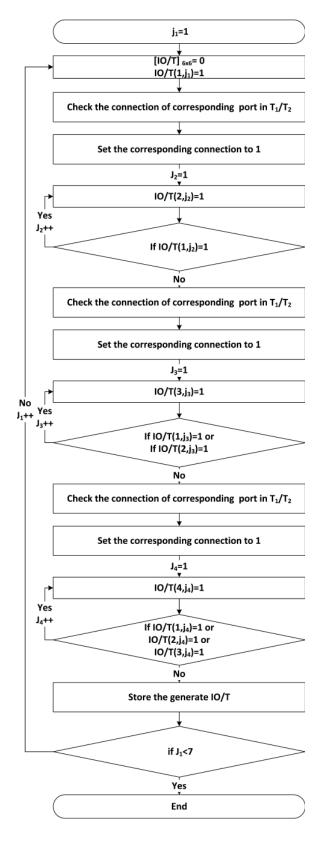

| 3.6  | The algorithm for generation of the $IO/T$ sub-matrix                          | 35  |

| 3.7  | The $CM$ for 3-transistor circuit and its sub-matrices                         | 36  |

| 3.8  | A sample circuit with three transistors (biasing not shown) and its $CM$       | 37  |

| 3.9  | An example of a $C2T$ block and $T_3$ block                                    | 37  |

| 3.10 | Two equivalent circuits with two different $CMs$ , when two transistors are    | 40  |

| 0.11 | swapped                                                                        | 42  |

|      | All possible $T_i/T_j$ sub-matrices                                            | 43  |

|      | The elements of the $T_i/T_j$ sub-matrix                                       | 44  |

| 3.13 | Two equivalent circuits with two different $CMs$ , when two sides of the load  | 4.0 |

| 0.14 | are swapped.                                                                   | 46  |

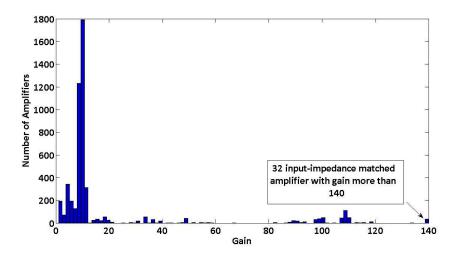

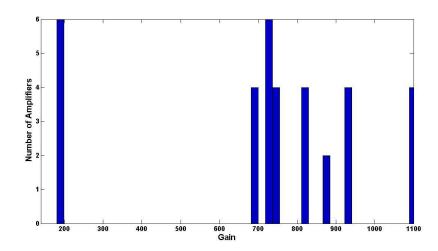

|      | The histogram for amplifiers with gain less than and equal to 140              | 63  |

|      | The histogram for amplifiers with gain higher than 140                         | 63  |

|      | The three generated 3 transistor amplifiers with the highest gain              | 64  |

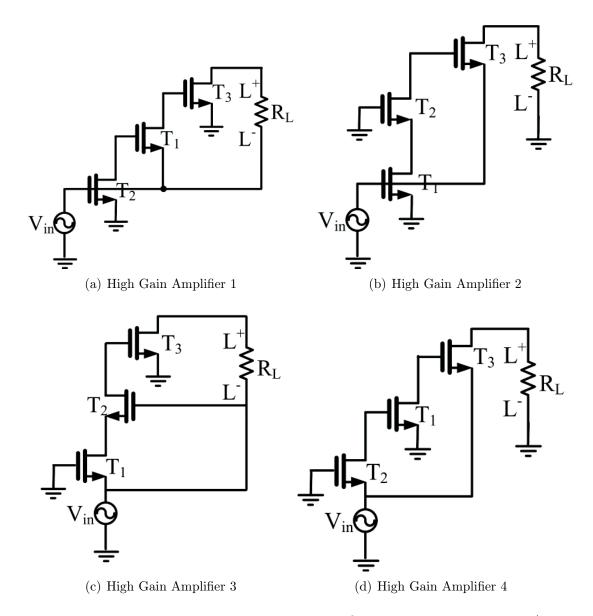

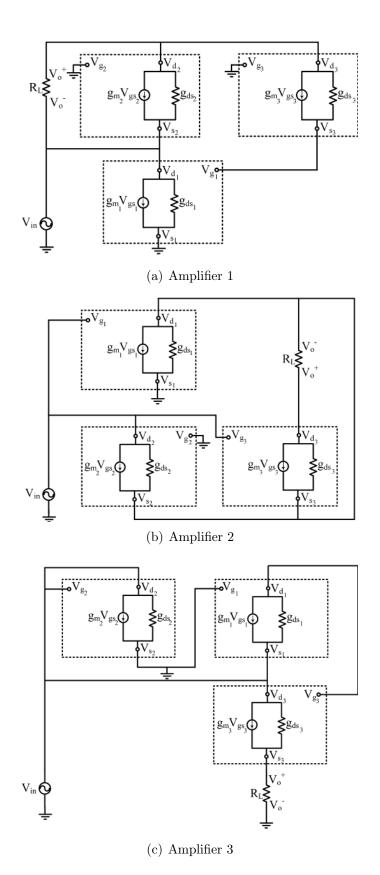

|      | Examples of three previously unknown amplifiers with three transistors         | 66  |

|      | Small-signal model of the three amplifiers in Fig. 3.17                        | 67  |

|      | Specifications are entered in "Required Specifications" window                 | 68  |

|      | The provided topologies with their $CM$ and small-signal specifications        | 69  |

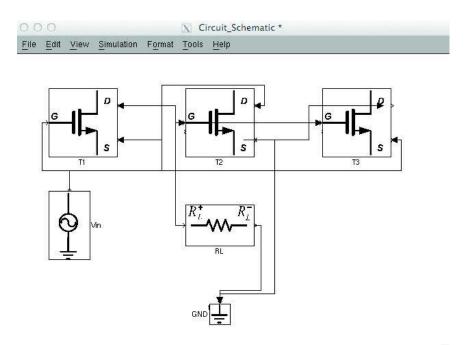

| 3.21 | The small-signal diagram of a circuit generated by ADA                         | 69  |

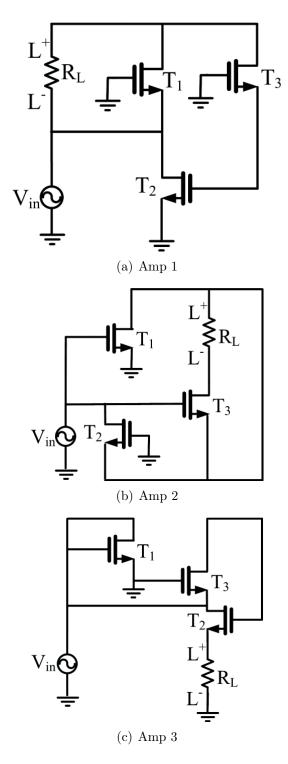

| 4.1  | The topology and its small signal model of selected amplifier, Amp 2           | 72  |

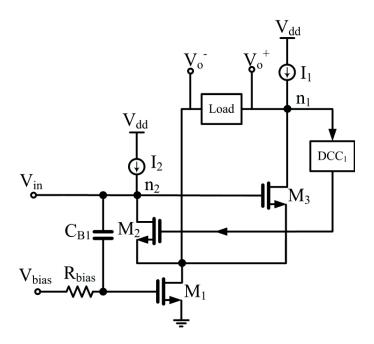

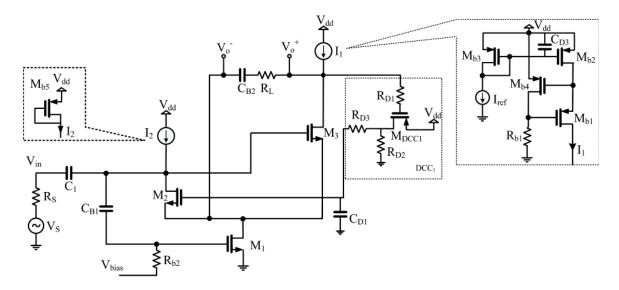

| 4.2  | Schematic of the amplifier with ideal current sources                          | 74  |

|      |                                                                                |     |

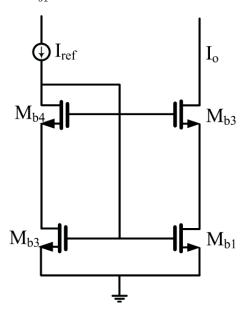

| 4.3 | A low headroom cascode current source                                                        | 76 |

|-----|----------------------------------------------------------------------------------------------|----|

| 4.4 | The final schematic of Amp 2                                                                 | 78 |

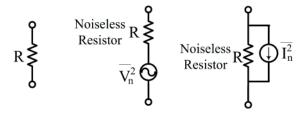

| 4.5 | Thermal noise of a resistor                                                                  | 80 |

| 4.6 | The noise generated by the drain of a transistor                                             | 81 |

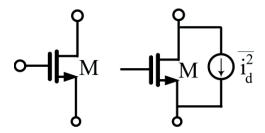

| 4.7 | Voltage gain and NF versus $g_{m_2}$ and $g_{m_3}$ values for $\gamma=1.33$ and $R_{in}=R_s$ | 83 |

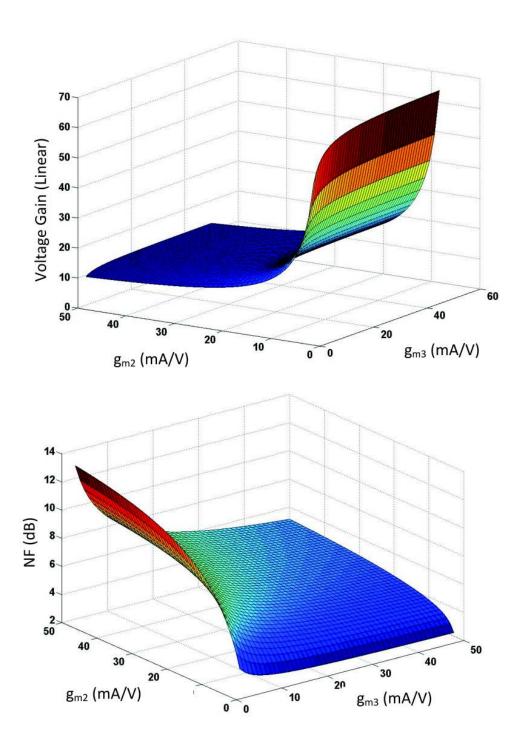

| 4.8 | The voltage gain and the NF of Amp 2                                                         | 86 |

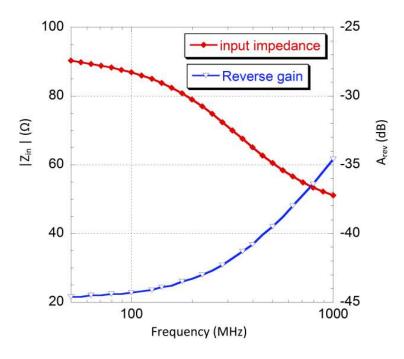

| 4.9 | The input impedance and the reverse gain of the amplifier                                    | 86 |

# List of Terms

### Acronyms:

ADA : Analog Design Assistant

ADC : Analog-to-Digital Converter

BSIM : Berkeley Short-channel IGFET Model

CAD : Computer-Aided Design

CMOS : Complementary Metal-Oxide-Semiconductor

DAC : Digital-to-Analog Converter

C2T: Connected-2-transistor

C3T: Connected-3-transistor

DC : Direct Current

DCC : DC Controller

DCT : Diode-Connected Transistor

DSP : Digital Dignal Processing

EA : Evolutionary Algorithm

GBW : Gain-Bandwidth

GUI : Graphical User Interface

I/O : Input/Output

IC : Integrated Circuit

KCL : Kirchhoff's Current Law

KVL : Kirchhoff's Voltage Law

LNA : Low Noise Amplifier

LP : Low Pass

MNA : Modified Nodal Analysis

MOS : Metal-Oxide-Semiconductor

MOSFET: Metal-Oxide-Semiconductor Field-Effect Transistor

NDCT : Non-Diode-Connected Transistor

SA : Simulated Annealing

SoC : System on Chip

SPICE : Simulation Program with Integrated Circuit Emphasis

$T_i$ : Transistor i

VCCS : Voltage Controlled Current Source

#### Variables:

$\mu$  : Charge-carrier effective mobility

$\lambda$  : Channel-length modulation

$\gamma$  : Gamma factor

$A_f$ : Forward gain

$A_{rev}$ : Reverse gain

ABCD : The two-port transmission parameters

$C_{ox}$ : Gate oxide capacitance per unit area

f : Frequency

F : Noise factor

$F_{M_i}$ : Noise factor of transistor  $i, M_i$

GND : Ground

$g_{ds}$ : Output transconductance of a MOS transistor

$g_m$ : Transconductance of a MOS transistor

$g_{m_u}$ : Upper bound of MOS Transconductance

$g_{m_l}$ : lower bound of MOS Transconductance

K: Process-dependent constant

k : The number of non-attacking rook

L: Gate length of a transistor

N: Total number of components in a circuit

$n_N$ : Total number of nodes in a circuit

$n_s$  : Total number of voltage source

$n_{NDC2_k}$ : The number of unique 2-transistor circuit when all transistors are NDCT

NF : Noise figure

$P_{av}$ : Average noise power of signal x(t) in time domain

$P_i$ :  $i_{th}$  port of C2T

$R_L$  : Load resistor

$R_{L_u}$ : Upper bound of the load resistor

$R_{L_l}$ : Lower bound of the load resistor

$V_{in}$ : Input Voltage

$R_{in}$ : Input resistance

$R_{in_n}$ : Upper bound of the input resistance

$R_{in}$ : lower bound of the input resistance

$R_o$ : Output resistance

$R_{o_n}$ : Upper bound of output resistance

$R_{o_l}$ : lower bound of output resistance

$r_{ds}$ : Output resistance of a MOS transistor

$R_{on_i}$ : Output resistance at node  $i, n_i$

$R_{cs}$ : Output resistance of low-voltage cascode current source

$r_{k_{m,n}}$ : The number of ways to place k non-attacking rook on an  $m \times n$  board

$S_x(f)$ : Average noise power of signal x(t) in frequency domain

SNR: Signal-to-noise ratio

$SNR_{input}$ : Signal-to-noise ratio at input

$SNR_{output}$ : Signal-to-noise ratio at output

$S_{(m,n)_k}$ : The number of symmetric  $m \times n$  board with k rooks

T: Period of signal x(t)

$V_{TH}$ : Threshold voltage of a MOS transistor

W: Gate width of a transistor

$Z_{in}$ : Input impedance

$Z_o$  : Output impedance

## **Scalars:**

$a_{ij}$ : Element of adjacency matrix in row i and column j

$b_{ij}$  : Element of incidence matrix in row i and column j

$CM_{ij}$ : Element of connectivity matrix in row i and column j

#### Vectors:

$I_c$ : Components' Current Vector

#### **Matrices:**

A : Adjacency matrix

B: Incidence matrix

M : MNA matrix

CM : Connectivity matrix

$T_i/T_i$ : Connectivity sub-matrix of connection between  $T_i$  block ports

$T_i/T_j$  : Connectivity sub-matrix of connection between  $T_i$  block ports and  $T_j$

block ports

IO/T : Connectivity sub-matrix of connection between IO block ports and T

block ports

IO/IO : Connectivity sub-matrix of connection between IO block ports

## Functions and Sets:

E : Set of edges

G : A graph

$L_n^{\alpha}(.)$  : Laguerre polynomial of degree n

$R_{m,n}(.)$ : Rooks polynomial for an  $m \times n$  board

V : Set of vertices

# Chapter 1

#### Introduction

#### 1.1 Motivation

With the advancement of technology, the number of transistors on an integrated circuit (IC) has increased substantially and this number doubles every two years as predicted by Moore's Law, which was introduced in 1965 by Gordon E. Moore [1]. As a result, complex systems that previously were implemented on several boards can be integrated on a single chip, which is called system on a chip (SoC). This leads to a significant reduction in the fabrication costs and an increase in the overall performance [2].

Most of the functions in an SoC are implemented using digital circuits and in particular digital signal processing (DSP) circuits. In comparison with analog circuits, DSP circuits are immune to noise and flexible to technology scaling [3]. There are still several analog circuits that cannot be replaced by digital circuits because the real world is analog [4]. These functions include the input/output interfaces, analog-to-digital converters (ADCs), digital-to-analog converters (DACs). Furthermore, some of the high-speed digital circuits are custom designed like analog circuits in order to achieve high performance [4].

Computer-aided design (CAD) tools have been employed by digital circuit designers for several decades to enable them to manage the increased complexity of the today's complex SoCs [5, 6]. Use of CAD tools has resulted in a shorter time-to-market for digital circuits. However, CAD tools that can help analog circuit designers are not as commonly used. This is mainly because of the complexity of the analog circuits, which require many years of design experience for successful implementation. In particular, there are different parameters that should be considered in an analog circuit design such as noise, power consumption, gain,

bandwidth, input and output impedance, area, and fabrication issues.

Although, a fully automated analog CAD tool does not seem to be feasible yet, there is a strong motivation to develop tools to assist analog designers automate certain parts of the design procedure. Analog circuit synthesis is one part that has recently become a topic of interest in both academia and industry. Synthesizing an analog circuit is usually performed in two steps: 1) selecting the appropriate topology. 2) Sizing the components in the selected topology to get the desired performance.

Analog circuit designers usually resort to a handful of well-known elementary circuits to design bigger and more complicated circuits. This approach is based on the experience and knowledge of the analog designer. In order to automate this step, there are two different approaches in the literature. In the first approach, in order to find a topology, all the configurations of complementary metal-oxide-semiconductor (CMOS) transistors, a votlage supply, and a resistor are generated, and the best one is selected [7]. The second approach is to employ well-known elementary circuits, which are commonly used in different circuits [4]. For instance, differential pairs, cascode amplifier, single stage amplifiers such as a common-source amplifier, current mirror circuits such as Wilson current mirror are used to generate new architectures [8].

When a topology is selected, the transistors should be sized for best performance that meets the required specifications. In the past, this step was done by either hand analysis and computer simulations. In the recent years, there have been many efforts to automate this step [9], but they are not well adopted by analog designers as they do not give the analog designers enough degrees of freedom to design their circuits. In other words, analog designers prefer to employ a design assistant tool rather than a fully automated CAD tool, which usually fails to meet all the required specifications.

#### 1.2 Thesis Contributions

In the following, a brief overview of the key contributions of this work is given.

#### • Analog CAD Tool Development

In this thesis, a CAD tool to help analog designers, analog design assistant (ADA), is developed. This tool helps analog designers synthesize and design analog circuits. In order to develop this tool, a methodology is proposed to automatically generate and classify all elementary circuit topologies that can be used in building analog circuits. Rather than storing circuit schematic representations, a sparse binary matrix representation is developed to represent the analog circuits. The proposed matrix representation allows efficient generation and storage of a large number of circuits. The proposed circuit generation algorithm results in over 56,000 circuits with three transistors. In addition, to obtain the maximum gain of each circuit, all generated circuit topologies are optimized. As an example of the potential usage of the developed tool, 5,103 unique circuits are identified as amplifiers with DC voltage gains higher than one.

Once the circuit topologies are generated, and optimized, the optimized circuits with corresponding circuit component values are stored in a database, which is easily accessible through a developed graphical user interface (GUI), where users can select their desired topologies by specifying the required range of circuit specifications. We anticipate that by using ADA many hours of design time can be saved and analog designers will have a bigger palette of designs to choose from.

#### • Circuit Development

In order to verify the capability of the ADA, one of the small-signal amplifiers

generated by ADA is selected and designed in a 0.13- $\mu$ m CMOS technology. To the best knowledge of the author, this amplifier has been never published in the literature and can be considered as a novel architecture. The simulation results show that the proposed amplifier has a noise figure of less than 3.1 dB and a voltage gain of 39 dB with a gain-bandwidth product of 50 GHz while it consumes 6.8 mW from a 1.8-V supply.

#### 1.3 Thesis Structure

The rest of this thesis is organized into the following chapters:

In Chapter 2, different circuit representations are introduced. A brief background of the design and synthesis of analog circuits is presented. Finally, different optimization methods are introduced in this chapter.

In Chapter 3 a new methodology is proposed to generate all functional and unique small-signal circuit topologies. Then, the specifications of generated circuits are calculated and analyzed to optimize their DC voltage gains. Generated circuit topologies with corresponding circuit component specifications are stored in a database. The database is provided with a user friendly graphical user interface (GUI) to help analog designers search through circuits based on their desired specifications. The GUI is called Analog Designer Assistant (ADA), since it is envisioned that it will assist analog designers to find new circuit topologies.

In Chapter 4 the design procedure of one of many 3-transistor amplifiers identified by ADA is presented. This circuit is optimized by ADA to have a high voltage gain and input power match. The selected configuration is then analyzed and designed in a 0.13- $\mu$ m standard CMOS technology. Finally, the agreement between Cadence circuit simulation results and the ADA optimization results is demonstrated in this chapter to show the ability of the proposed ADA to identify and accurately optimized circuits.

In Chapter 5 the summary of major contributions of this thesis is presented. In addition, some suggestions for the future work are briefly discussed.

# Chapter 2

# Analog Circuit Representation and Synthesis

#### 2.1 Introduction

Analog designers usually employ a few known topologies to design circuits such as operational amplifiers, current sources, mixers, low noise amplifiers (LNAs), filters, and frequency synthesizers. In the area of LNA design, for example, common-source and common-gate topologies are well known architectures that have been employed for several decades and are still widely used by the analog designers [10]. Discovering novel architectures with better performance has been one of the challenges in the analog design process. In addition, analog designers often use an often cumbersome combination of hand analysis and circuit simulations to evaluate the performance of their new circuits. Consequently, in order to save time and cost, analog computer-aided design (CAD) tools are needed to reduce the manual design process and offer new topologies. The main purpose of this thesis is to develop a new CAD tool that can be used as a design assistant and can generate and optimize novel circuit topologies.

The rest of this chapter is organized as follows: In Section 2.2 different representations for analog circuits are discussed. In Section 2.3 synthesis of analog circuits is reviewed. Circuit optimization approaches are discussed in Section 2.4. Finally, the chapter is summarized in Section 2.5.

## 2.2 Circuit Representations

One of the essential tasks in the design of analog circuits is to compute different characteristics of circuits and to evaluate circuit behaviour under different operation points. To obtain these circuit characteristics appropriate formats need to be used. Some of these formats are schematics, graphs, netlists, and matrices, which will be discussed in the following section. Based on the criteria that have to be evaluated one of the formats is chosen. The different formats can be converted to each other, for example, most of the electronic design automation (EDA) tools use a netlist representation to simulate a circuit, but the analog designers prefers to draw their circuits in the schematic format. Therefore, the EDA tools convert the schematic representation to the netlist representation to simulate a circuit, and vice versa. These formats are briefly discussed in the following.

#### 2.2.1 Schematic Representation

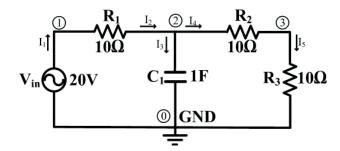

A schematic diagram is an abstract representation for analog circuits, which represents the circuit components as standard simplified symbols and shows the connection between them. In this representation, a node refers to a point where two or more components are connected to each other, and a branch indicates the connection between two nodes. An example of the schematic representation of a circuit is shown in Fig. 2.1. In this circuit nodes are numbered from 0 to 3 and the currents of branches are illustrated by  $I_1, I_2, I_3, I_4, I_5$ . Commonly, the node connected to ground is considered node 0.

Figure 2.1: The schematic representation of a circuit

The schematic representation of a circuit is the most commonly used circuit representation for analog designers, since it is suitable for Kirchhoff's current law (KCL) and Kirchhoff's voltage law (KVL) in hand analyses. Some of the EDA tools, such as Cadence [11] and Agilent ADS [12] accept schematic representations created by the user as input to their program. While a schematic diagram is a user friendly representation, it is not efficient to use when the size of memory to store circuit schematic is important. The memory size needed to store schematics is negligible when designers are dealing with limited number of circuit components, but it should be taken into account when a database of thousands of circuits is generated.

#### 2.2.2 Graph Representation

Another method to represent a circuit is by using a graph representation [13, 14, 15, 16]. A graph, G = (V, E), is defined as a set of vertices  $V = \{v_1, v_2, ...\}$  and a set of edges  $E = \{e_1, e_2, ...\}$ , where, an edge connects exactly two vertices. Graphs are classified based on desired properties. For instance, if directions of edges are important, they are classified in two categories, directed and non-directed, where a directed graph is a graph in which a direction is shown for each edges. The direction of the edges shows the direction of current in the related component. Since, the current in each branch has direction, the directed graph representation is commonly used to analyze circuits.

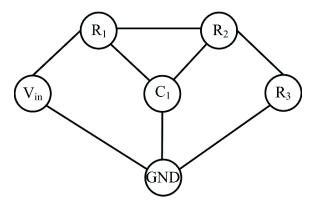

In Fig.2.2, a graph representation of the circuit illustrated in Fig. 2.1 is given. In this example circuit components  $R_1, R_2, R_3, C_1, V_{in}$  and GND are represented by vertices.

Figure 2.2: The circuit graph of circuit illustrated in Fig.2.1

Since the graph representation is an abstract representation and is simple to draw, it has been used to obtain proper values for parameters such as sizes of transistors or transistor biasing [13, 14, 15]. This representation is not commonly used for KCL or KVL analysis the circuit, since it is more abstract than the schematic representation.

#### 2.2.3 Netlist Representation

In a netlist representation, the connection between circuit components are shown in a text format. Each component in the netlist representation is assigned a line. The first column of each line demonstrates the name of component in the circuit. Then, component terminal connections to circuit nodes are indicated in next columns. The last column is the value of the component.

The netlist representation of the example in Fig. 2.1 is shown in Fig. 2.3. For instance, resistor 1,  $R_1$ , is connected to node 1 and 2, and has a value of 10  $\Omega$  as shown in line 2 of the netlist representation.

| $ m V_{in}$    | 1 | 0 | 20 |

|----------------|---|---|----|

| $R_1$          | 1 | 2 | 10 |

| $R_2$          | 2 | 3 | 10 |

| $R_3$          | 3 | 0 | 10 |

| $\mathbf{C}_1$ | 2 | 0 | 1  |

Figure 2.3: The circuit netlist of circuit illustrated in Fig.2.1

Simulator program with integrated circuit emphasis (SPICE) introduced in 1970 [17], and its derivatives PSPICE and HSPICE input circuits in the netlist representation and generate netlist files in the text format.

The netlist representation is efficient when a large number of circuits is considered, due to its low memory requirements. The disadvantage of this representation is that it is too abstract for analog designers.

#### 2.2.4 Matrix Representation

A circuit can be represented by a matrix [18, 19]. Three types of matrix representation are discussed in this section: Adjacency matrix, Modified Nodal Analysis (MNA) matrix and Incidence matrix.

#### Adjacency Matrix

The adjacency matrix, A, shows the connections between the cells of a matrix. Normally, it is an  $N \times N$  matrix, where N is the total number of components in the circuit. The adjacency matrix is constructed using only binary values, 0 and 1, where each column or row of the matrix represents a component in the circuit. If component i is connected to component j, the corresponding elements of A,  $a_{ij}$  and  $a_{ji}$ , are set to 1, otherwise the value is 0. Since  $a_{ij}$  and  $a_{ji}$  are equal, the adjacency matrix is symmetric. The diagonal elements of the matrix are normally set to zero. The adjacency matrix for the example in Fig. 2.1 is shown in Fig. 2.4.

Figure 2.4: The adjacency matrix representation for circuit illustrated in Fig.2.1

In [20], the adjacency matrix representation is employed to represent and synthesize analog and digital circuits. This representation is efficient to store analog and digital circuits, since it requires low memory size. The adjacency representation is too abstract to analyze performance of circuits.

#### **Incidence Matrix**

The incident matrix, B, is an  $n_N \times N$  matrix, where  $n_N$  is the number of nodes and N is the number of components. The elements of the matrix are -1, 0, and 1. If the current of component i leaves node j, the corresponding element in the incident matrix  $(b_{ij})$  is set to 1 and if the current of component i enters node j, the corresponding element in the incident matrix  $(b_{ij})$  is set to -1. Otherwise the value would be set to 0. Hence, the incident matrix shows the direction of current through components. The incidence matrix for the circuit in Fig. 2.1 is shown in Fig. 2.5.

$B = \begin{bmatrix} 0 & 1 & 2 & 3 \\ -1 & -1 & 0 & 0 \\ 0 & 1 & -1 & 0 \\ R_2 & 1 & 0 & 1 & -1 \\ R_3 & 0 & 0 & 0 & 1 \\ C_1 & -1 & 0 & 1 & 0 \\ GND & 1 & 0 & 0 & 0 \end{bmatrix}$

Figure 2.5: The incidence matrix for the circuit illustrated in Fig.2.1

Incident matrices are usually used to perform KCL to find branch currents and analyze the circuit performance. In order to use B matrix to perform KCL, the row and column corresponding to node 0, and ground are removed, since the voltage of node 0 is 0. Using the matrix B leads to obtain KCL equations as follows:

$$B \times I_c = 0, \tag{2.1}$$

where,  $I_c$  is a vector of components' currents. For example, the circuit in Fig. 2.1, can be

analyzed by solving the following equation:

$$\begin{bmatrix} -1 & 1 & 0 & 0 & 0 \\ 0 & -1 & 1 & 1 & 0 \\ 0 & 0 & 0 & -1 & 1 \end{bmatrix} \times \begin{bmatrix} I_{c_1} \\ I_{c_2} \\ I_{c_3} \\ I_{c_4} \\ I_{c_5} \end{bmatrix} = 0$$

(2.2)

#### Modified Nodal Analysis (MNA) Matrix

Modified nodal analysis (MNA) matrix, M, shows the value of the components in the circuit between any two nodes. In this representation, a node refers to a point where two components are connected to each other, and a branch indicates the connection between two components. This resultant matrix is  $(n_S + n_N - 1) \times (n_S + n_N - 1)$ , where  $n_N$  is the number of nodes in the circuit and  $n_S$  is the number of voltage sources. The matrix is developed by using MNA method [21]. This method requires a three step of KCL. In the first step, the KCL is written for each node in the circuit, except the GND node, since the voltage of this node is 0. The voltage-current characteristic equation for each branch is written in the second step. At the end, the obtained equations from the second step are substituted in equations achieved from the first step. The final equations result in a matrix equation as shown in the following:

$$M \times x = z. \tag{2.3}$$

Matrix M, x, and z can also be obtained without writing KCL equations. In this approach, matrix M is developed as the combination of 4 sub-matrices,  $M_G$ ,  $M_B$ ,  $M_C$ , and  $M_D$  as follows:

$$M = \begin{bmatrix} M_G & M_B \\ M_C & M_D \end{bmatrix}. \tag{2.4}$$

$M_G$  matrix is an  $n_N-1\times n_N-1$  matrix with its columns and rows representing the nodes. The diagonal elements of the matrix represent the sum of the components admittances connected to the corresponding node, and the off-diagonal elements indicate the negative of the component admittance of connected between two corresponding nodes.  $M_B$  matrix is an  $n_S \times n_N - 1$  matrix, which shows the voltage source connected to each node. For instance if voltage source 2 is connected to node 3, element  $M_{B_{23}}$  will be set to 1.  $M_C$  matrix is an  $n_N - 1 \times n_S$  matrix, and it is a transpose of matrix  $M_B$ .  $M_D$  matrix is an  $n_S \times n_S$  matrix, and if only independent sources are considered it is zero. When there is a dependent source in a circuit, the voltage of each node or the current of each branch is dependent on some other voltage or current in the circuit. Based on the equation of the dependent source, M matrix has to be modified.

x matrix is an  $(n_N + n_s - 1) \times 1$  matrix. The first  $n_N - 1$  rows in matrix x indicate voltages of the nodes in circuit, except the node connected to ground, and the last  $n_s$  rows in the matrix represent the currents flowing through each voltage source. For instance, for circuit in Fig. 2.1, there are three nodes, where their voltages are  $V_1, V_2$ , and  $V_3$ , and there is one voltage source, and its current is  $I_{V_{in}}$ .

z matrix is an  $(n_N + n_s - 1) \times 1$  matrix. The first  $n_N - 1$  rows in matrix x indicate the sum of currents flowing into nodes in circuit, except the node connected to ground (zero or the sum of independent current sources) and the last  $n_s$  rows in the matrix represent the voltages of the voltage sources. For instance, for circuit in Fig. 2.1, there are three nodes, where the currents flowing in to them are all 0, and there is one voltage source,  $V_{in}$ .

The MNA matrix representation for circuit in Fig. 2.1 is:

$$\begin{bmatrix} G_1 & -G_1 & 0 & 1 \\ -G_1 & G_1 + G_2 + sC_1 & -G_2 & 0 \\ 0 & -G_2 & G_2 + G_3 & 0 \\ \hline 1 & 0 & 0 & 0 \end{bmatrix} \times \begin{bmatrix} V_1 \\ V_2 \\ \hline V_3 \\ \hline I_{V_{in}} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ \hline V_{in} \end{bmatrix},$$

(2.5)

where  $G_i$  is the conductance of component i, and is equal to  $\frac{1}{R_i}$ .

Finally, by solving (2.5), frequency domain transfer functions of analog circuits with multi-input and multi-outputs are obtained and used to analyze circuit performance [22].

It should be mentioned that the matrix representation is used in this thesis, due to their low memory requirements, and the ease of applying KCL.

#### 2.3 CAD-based Analog Circuit Synthesis and Analysis

Analog designers would normally use different tools to analyze and synthesize circuits. In analog circuit analysis, circuit topology and parameters are given, and the performance of a circuit is calculated and analyzed [23]. In circuit synthesis, desired specifications are given. Then blocks and sub-blocks are synthesized or selected, and the parameters for the sub-blocks, such as transistor size and biasing, are determined to obtain the desired specifications [24]. These sub-blocks are selected either by:

- Using previously used circuit topologies, or

- generating new circuit topologies

#### 2.3.1 Previously known circuit topologies

In order to speed up circuit design and development, many of functional analog circuits can be catalogued into libraries. Therefore, analog designers can re-use known circuit topologies and do not need to recalculate their characteristics, which results in saving valuable computation and design time.

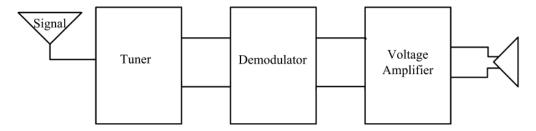

In [6], in order to select appropriate blocks, desired circuits are decomposed into subblocks. For instance, a radio receiver shown in Fig. 2.6, is decomposed into three sub-blocks: a tuner, a demodulator, and a voltage amplifier. To design this radio receiver, each initial sub-block is selected from the available topologies in the library. This selection is based on required specifications for the circuit, which are defined after investigating final product's cost and time.

Figure 2.6: A radio receiver decomposed into three blocks in order to design in approach described in [6]

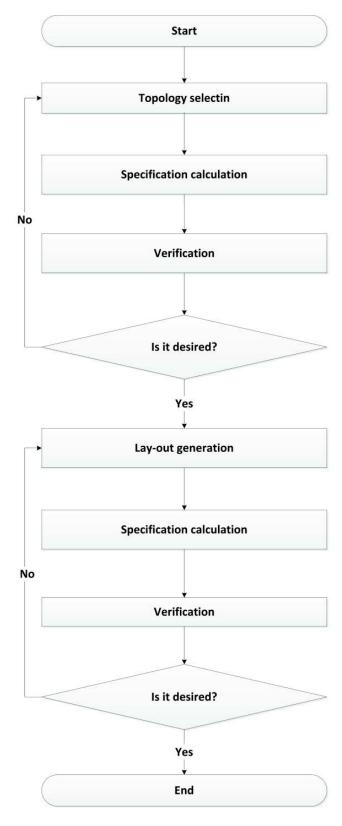

The proposed algorithm in [6] is shown in Fig. 2.7. First, the circuit specifications are defined which leads to the selection of suitable blocks from already known topologies stored in the library. Then, all the sub-blocks are assembled and the circuit specifications are calculated. If the required specifications are met, the algorithm proceeds to the next phase which is the layout generation. Otherwise, it keeps looking for the appropriate topologies for different sub-blocks until the required specifications are met. In the layout generation phase of the algorithm, the same procedure is followed to find the best layout for the selected circuit.

The described algorithm is effective as long as the existing topologies in the library can meet the required specifications. But there might be some new topologies that outperform the existing ones in the library, and the algorithm fails to find these new topologies.

Figure 2.7: The procedure of analog circuits synthesis described in [6].

#### 2.3.2 Generating new circuit topologies

Although, previously used circuit topologies are useful as a starting point for an analog designer, they are not efficient when a designer is looking for new topologies. There have been several attempts in the literature to generate new circuit topologies [7, 25]. In this section, two different approaches to generation of new topologies are discussed.

#### **Manual Topology Generation**

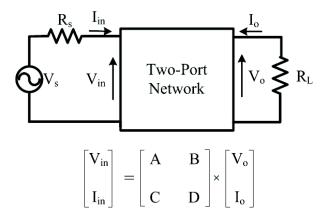

In [7, 25] a technique to generate all possible topologies for circuits with two transistors is proposed. In [7, 25] an analog circuit is represented by a small-signal two-port network with an input port and an output port as shown in Fig. 2.8. The source of the two-port network is represented by a source voltage,  $V_S$ , and a source impedance,  $R_S$ . The output port is modelled by a load impedance,  $R_L$ .

The two-port network is described by a set of ABCD parameters. These parameters relate the output voltage and current to the input voltage and current according to:

$$V_{in} = A \times V_{out} + B \times I_{out} \tag{2.6}$$

$$I_{in} = C \times V_{out} + D \times I_{out} \tag{2.7}$$

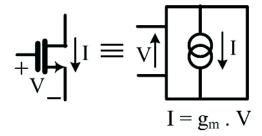

A MOS transistor is considered as a voltage controlled current source (VCCS), as shown in Fig. 2.9. The current of the VCCS is  $I = g_m \cdot V$ , where  $g_m$  is transconductance of the transistor.

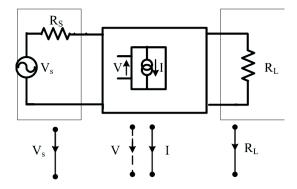

In addition, the two-port network is modelled as a graph, where each circuit component is considered as an edge of the graph. The signal-source voltage and the load of the two-port network are modelled as two graph branches,  $V_{in}$  and  $R_L$ , respectively, and the branches V and I represents the current and the voltage in VCCS. The modelling approach in [7] is illustrated in Fig. 2.10.

Figure 2.8: A two-port network and its ABCD matrix

By following the modelling approach in Fig. 2.10, a signal-source, a load and two VCCSs are modelled with 6 branches and 12 nodes. Different connections between these components result in a large number of different graphs. In order to reduce the number of graphs and find the functional circuits, some constraints need to be defined, which are:

- All branches must be connected in loops: if all branches are not connected in loops, the current will be zero and the circuit will be open circuit.

- No self-loops in the graph is allowed: a self-loop refers to a branch that has current enter and leave the same node. A self-loop results in a short-circuit.

Once an individual transistor graph is determined, all different graphs are generated by hand in [7, 25]. In addition, the ABCD parameters are calculated and analyzed by means of MAPLE to classify the two-ports networks. This results in 145 different graphs with non-zero ABDC parameters.

In [26, 27], all potentially useful 2-VCCS circuits generated are considered to be wide-band LNA. Graphs of wide-band amplifiers are extracted from the 2-VCCS database according

Figure 2.9: A transistor is modelled as a VCCS where  $g_m$  is the small-signal transconductance of the transistor

Figure 2.10: Representation of two-port network with a MOS transistor by a graph, where  $g_m$  is the small-signal transconductance of the transistor

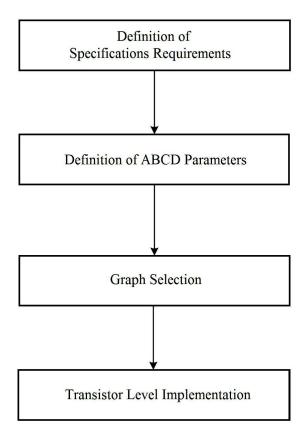

to the previously defined constraints on the ABCD parameters. In Fig. 2.11 the flowchart procedure of selecting graphs as LNA is shown. In this procedure there are four steps, which are discussed as follows:

- Step 1: Source and load impedances requirements and amplifier functional requirements are defined. In the case of a wide-band amplifier, the input power and the output power match are required, and the DC forward gain should be greater than one. In addition, the circuit should be stable at all frequencies.

- Step 2: Based on Step 1 constraints for the ABCD parameters of the amplifiers

Figure 2.11: The flowchart of circuit generations algorithm proposed in [26, 27] are defined.

- Step 3: Graphs that meet the defined constraints are chosen from the database.

- Step 4: MOS transistor circuits of the selected graphs are provided.

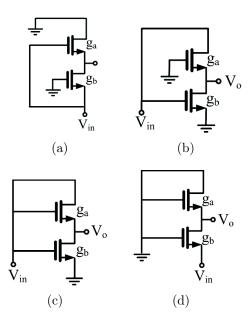

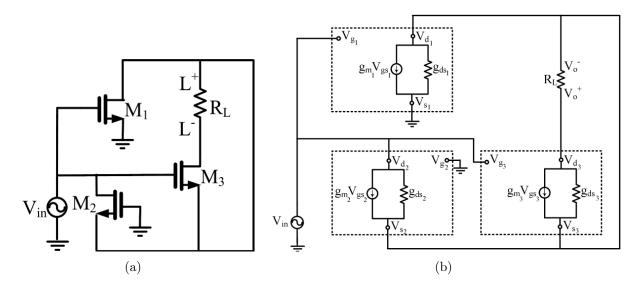

Finally, by following the described procedure, four elementary 2-transistor circuits, shown in Fig. 2.12 are selected and analyzed. Two of the amplifiers were known circuits, (c) and (d), and two of them were unknown, (a) and (b), to the author of [26, 27].

#### **Automated Topology Generation**

In order to avoid missing topologies and saving time when find elementary circuits, there have been attempts to generate new circuit topologies automatically. In [28], the procedure

Figure 2.12: The 2-MOSFET wideband amplifiers generated in [26, 27] (biasing not shown) from [7] was automated by a computer, and all possible circuits containing two and three transistors were generated. This procedure is as follows:

- Generating all circuits with a source, a load, and two or three transistors, which were modelled as VCCSs according to the method described in [7].

- The symbolic modified nodal analysis (MNA) equations are set up by EASY-C to analyze symbolically. By using MAPLE the EASY-C results are calculated numerically.

- The generated circuits were stored with their analyzed parameters in a database.

The generated circuits in [28] are not unique, since no rules were defined to eliminate the identical circuits. From all generated topologies, the numbers of circuits with two and three transistors with specific ABCD parameters in the database are 628 and 88347, respectively, in which all generated circuits are not included. In addition, there is no mathematical proof for the total numbers of the generated circuits.

Another method, which is proposed in [29] generates circuit designs using an evolutionary

algorithm. In this work, circuit designs consist of resistors, capacitors, inductors, and bipolar transistors. These components are placed in a box between the input voltage source and the output load as shown in Fig. 2.13. Each component must have two terminals in order to be connected to other components. Therefore, a set of different architectures for a transistor is pre-defined to have only two floating terminals while the third terminal is connected to a fixed node such as ground, input voltage source, or output load.

In the beginning of the algorithm, the input node is considered as the active node and in each step of the evolutionary algorithm, there should be only one active node in the circuit. In each iteration, a new component is added to the active node in one of the following ways: 1) Between the active node and ground node 2) Between the active node and input node 3) Between the active node and output node 4) Between the active node and the previous node 5) Between the active node and a newly-created node After adding each component, the circuit is analyzed by using SPICE and the results are compared with the required specifications. Finally, the output of the genetic algorithm is the circuit with the best performance. The proposed algorithm is used to design amplifiers as well as filters. The circuit designs in this work do not exhibit the level of performance of their hand-designed predecessors even after thousands of iterations in the algorithm. Another limitation of this work, which is even stated in [29], is the inherit restriction in circuit topologies which is basically because of the way they have to represent a transistor as a two-terminal component.

Figure 2.13: The evolved topology is located between fixed input and output terminals [29].

Although, generation new topologies results in having appropriate circuit topologies, transistor sizing and biasing are also important in a design process. Therefore, there are different ways to optimize analog circuits, which meet the economic constraints such as time, and cost [30, 9].

# 2.4 Optimization Applications for Circuit Synthesis

Analog designers use optimization to synthesize their circuits [30, 32, 34]. There are different techniques to solve an optimization problem. All of these optimization techniques have their own advantages and disadvantages. Based on the size of the problem and accuracy, analog designers can select a proper technique to optimize during a design and synthesis process.

In [30], an algorithm to automate the synthesis of analog circuits was described. The first step is to generate a searchable, and flexible library. In this library, there are various known blocks, which are decomposed to several sub-blocks. A multi-objective optimization problem is used to find proper sizes for the circuit components. The power, area, and performances are considered in this problem. An evolutionary algorithm (EA) is used as an optimization method to solve the defined optimization problem [31]. EA is an algorithm for finding solutions based on the evolutionary process. After each iteration the results are stored in a set. These results are updated by comparison to previous solutions to find optimal results. Once all sub-blocks in the library are optimized, a set of sized topologies is returned.

EA is also used in [32], where the value of the components are optimized to synthesize circuits. In [32], the optimization is done by changing device parameters such as sizes and bias points, while checking the circuit performance. Different parameters are stored with the corresponding circuit performance.

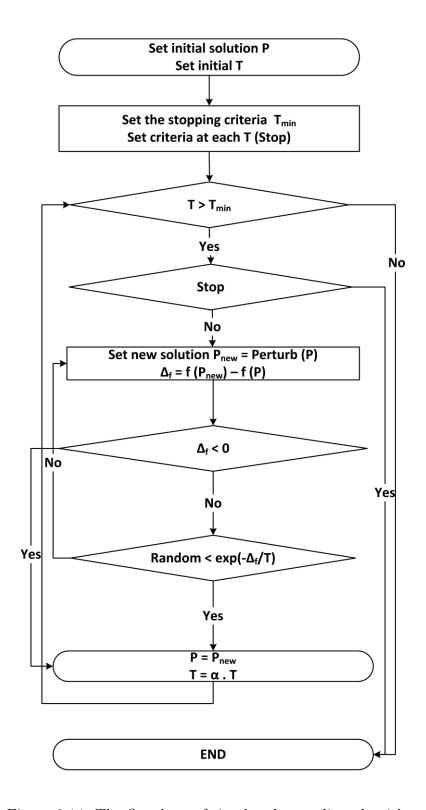

Another technique to solve an optimization problem is called simulated annealing (SA). This technique was introduced by Kirkpatrick in 1983 [33]. This technique was inspired by the process of annealing in metals. In this process, a metal is heated to a certain temperature for a period of time, then cooled down to a certain temperature for a period of time.

This process repeats until the final temperature reaches the room temperature. The SA optimization is analogous to this process by using a global parameter T, analogous to temperature in the process of annealing in metallurgy. The T parameter is decreased gradually. In the each iteration, the algorithm replaces the current solution by a slightly perturbed solution. This new solution is accepted if the new solution is better than current solution, or it is accepted with a probability of  $e^{-\Delta_f/T}$ , where  $\Delta_f$  is the difference between new function value and previous function value. After several iterations, when T is sufficiently reduces, the algorithm starts to look for the local minimum solution for the optimization problem. The higher T is, the higher the acceptance probability of a new solution is, which prevents from being trapped in the local minimum.

The flowchart of SA algorithm is shown in Fig. 2.14. In this algorithm, first the initial solution and temperature are set. Then, the stopping criteria for the algorithm is set that is a minimum temperature (similar to the room temperature in metal annealing). Also, the time that algorithm spends at each temperature is chosen for each step. At each temperature, new solutions are examined. If the cost of this new solution is less than the cost of the initial solution, the new solution is accepted. In [34], SA algorithm is employed to optimize the circuit parameters such as MOS transistors' width and length to achieve the desired circuit specifications. It can also choose the best topology among the known topologies based on the application requirements. But it is not able to generate new topologies.

The disadvantage of using EA and SA approaches for the synthesis of a large number of circuits is the long runtime. In this thesis, a constrained non-linear optimization problem is employed. The problem can be defined as:

Figure 2.14: The flowchart of simulated annealing algorithm

$$\min_{x_1,...x_n} f_0(x_1,...x_n)

\text{s.t.} f_i(x_1,...x_n) \le 0, i = 1,..., I$$

$$g_j(x_1,...x_n) = 0, j = 1,..., J,$$

where  $f_0$  is the objective,  $f_i(x)i = 1, ..., I$  is the inequality-constraint and  $g_j(x)$ , j = 1, ..., J is equality-constraint.  $x_1, ...x_n$  are variables. There are several approaches to solve the constrained non-linear optimization problem, such as interior-point methods. Interior point method has got a linear time complexity [36].

# 2.5 Summary

In this chapter, different representations of analog circuit have been discussed. From these representations, matrix representation is selected to model analog circuits in this work. In addition, in this chapter the different methods to design and synthesize analog circuits have been discussed. Finally, the different optimization methods have been discussed in order to maximize the performance of the circuits. Also, circuit optimizations were discussed that could be used to achieve the best performance from analog circuits.

# Chapter 3

# Proposed Systematic Hierarchical Methodology

### 3.1 Introduction

In this chapter, an Analog Design Assistant, ADA, that can be used to generate new circuit topologies is represented. ADA automatically generates all analog circuit topologies containing two or three MOSFET transistors. Using ADA over 56,000 elementary functional circuits are found. ADA is designed to solve small-signal models of the generated circuits and, as an example, the voltage gain, the input and output impedances and the reverse gain are obtained for each of over 56,000 circuits. In addition to demonstrate optimization capabilities of ADA, a constrained optimization problem is solved for each topology to find the transistors' small-signal parameters. In this thesis, the optimization problem is set such that the maximum possible DC voltage gain of each circuit is found. The results of the optimization problem show that over 5,000 of the topologies act as input power matched amplifiers with gains higher than 1. The obtained characteristics and transistors' small-signal parameters are stored in an efficient database to be used as an assistance tool by analog designers for choosing the best circuit topology or for searching for new topologies. The pre-generated, pre-designed circuit topologies are accessible through a developed GUI, which allows a designer to select topologies by specifying the required range of circuit specifications.

This chapter is organized as follows: In Section 3.2, the analog circuit representation developed for ADA is introduced. In Section 3.3, the proposed systematic methodologies for circuit generation with two and three transistors are explained. In Section 3.4, the proof that the proposed technique covers all circuit topologies is given. The results of the proposed

methodology are given in 3.5. In Section 3.6, the small-signal characteristics of the generated circuits and their optimized versions are discussed. In Section 3.7, the GUI development of ADA tool is presented. Finally, concluding remarks are given in Section 3.8.

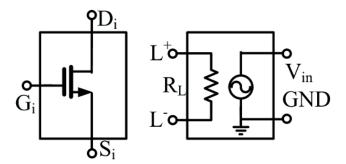

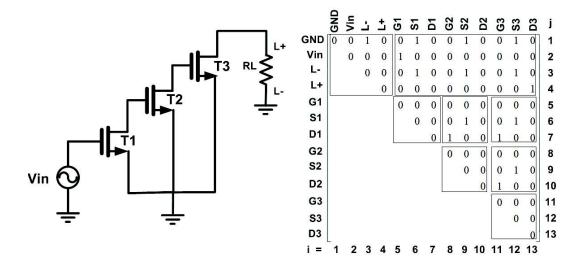

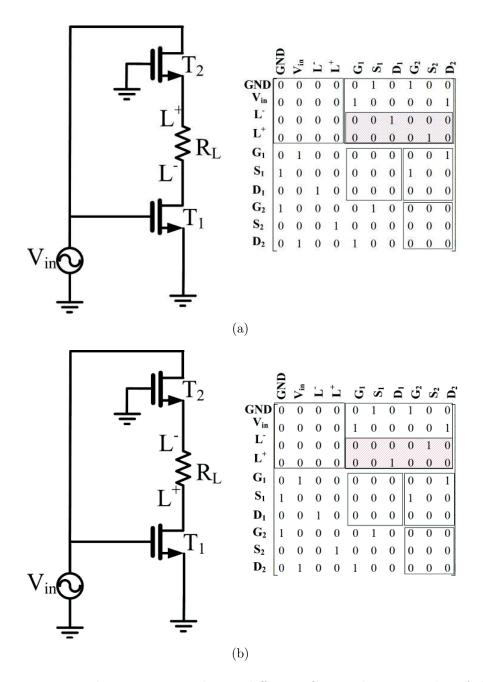

### 3.2 Circuit Representation

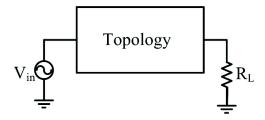

The first step in developing ADA was to divide circuit elements into building blocks based on their functionality. Two basic blocks were defined: an Input/Output block, I/O, and a Transistor block, T. The I/O block is made of the following 4 ports: ground (GND), input voltage  $(V_{in})$ , positive side of the load  $(L^+)$ , and negative side of the load  $(L^-)$ . A Transistor block,  $T_i$ , has three ports: gate  $(G_i)$ , source  $(S_i)$ , drain  $(D_i)$ . Examples of an I/O block and a Transistor block are shown in Fig. 3.1.

Figure 3.1: Building blocks of an analog circuit. The block on the right is the I/O block and the block on the left is the Transistor block.

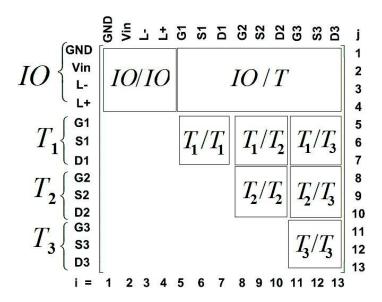

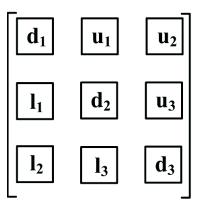

Once the building blocks are defined, all possible topologies are generated by changing the internal block connections and the connections between blocks. A special connectivity matrix, CM, is designed to assist with generation of all non-duplicate topologies. The rows and columns of the connectivity matrix are organized with the ports of Input/Output block, and followed by the ports of Transistor blocks as shown in Fig. 3.2. In this figure, the matrix representation of an analog circuit containing two transistors,  $T_1$  and  $T_2$ , is shown. The connection between the ports of the I/O block to each other and the ports of the Transistor

Figure 3.2: The connectivity matrix, CM, and the position of sub-matrices representing the connectivity between elements

block to each other are represented by IO/IO and  $T_i/T_i$  sub-matrices, respectively. These sub-matrices are located along the diagonal of CM. The connection between the ports of the I/O block and the ports of the transistor block are represented by IO/T sub-matrix. Finally, the connection between the ports of two different Transistor blocks,  $T_i$ , and  $T_j$ , are shown by  $T_i/T_j$  sub-matrix. As the connections between  $T_i$  and  $T_j$  and  $T_j$  and  $T_i$  are the same, CM is symmetric, and to save memory the elements below the diagonal are not stored.

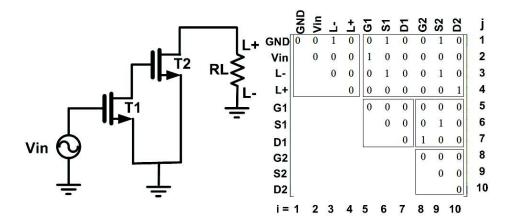

#### 3.2.1 Connectivity Matrix Construction

To construct CM, when two ports, i and j, are connected, the value of the corresponding elements,  $CM_{ij}$  and  $CM_{ji}$ , is set to 1, otherwise the value of  $CM_{ij}$ , and  $CM_{ji}$  is 0. All diagonal elements of CM are 0, since the ports cannot be connected to themselves. In Fig. 3.3 an example of circuit with two transistors, and the corresponding connectivity matrix is illustrated. In the connectivity matrix the source (i = 6) of  $(T_1)$  is connected to ground (j = 1). Therefore  $CM_{16}$  and  $CM_{61}$  are equal to 1.

Figure 3.3: An anolog circuit (biasing not shown) and corresponding connectivity matrix

# 3.3 Circuits Generation Using a Connectivity Matrix

In this section, a technique to generate all 2-transistor circuits by generating their corresponding CMs is presented. It is followed by discussions on generation of circuits with more transistors.

#### 3.3.1 2-transistor Circuits Generation

To generate all possible CMs, all internal connections of the blocks, and then the interconnections between them need to be made. The main steps of the algorithm to generate CMs of all circuits with two transistors are as follows:

#### 1. Generate internal connections

- (a) Generate IO/IO sub-matrix

- (b) Generate  $T_1/T_1$  and  $T_2/T_2$  sub-matrices

### 2. Generate Blocks Interconnections

- (a) Generate  $T_1/T_2$  sub-matrix

- (b) Generate IO/T sub-matrix

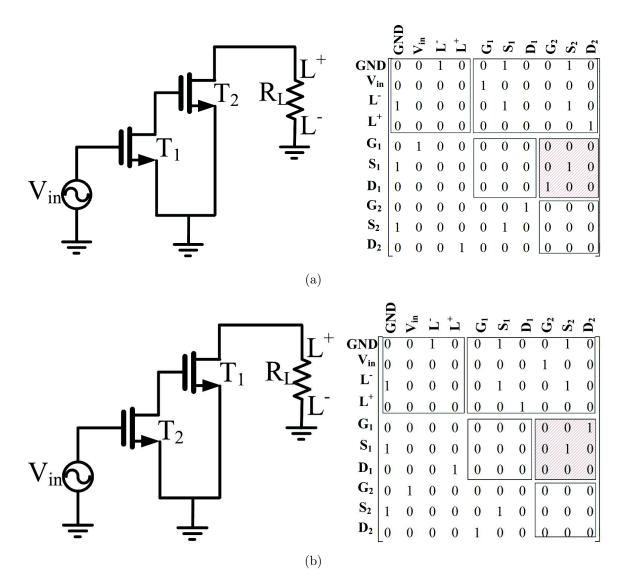

Figure 3.4: All possible I/O block configurations:(a) When one side of the load is connected to input voltage, (b) When one side of the load is connected to ground, and (c) When the ports are not connected to each other

Each step is described in detail in the following.

#### **Internal Connections Sub-matrices**

The rules to generate the internal blocks and the possible configurations for them are described in the following.

**IO/IO sub-matrix generation:** The sub-matrix representation of the I/O block's connectivities is a  $4 \times 4$  symmetric matrix. The following circuit rules are set for this block to ensure functionality:

- The GND port cannot connect to  $V_{in}$ .

- Either of the load ports cannot connect to GND and  $V_{in}$  simultaneously.

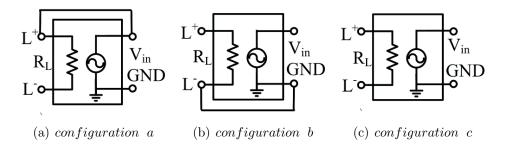

Using the preceding rules, the IO/IO sub-matrix of CM can have three possible configurations as shown in Fig. 3.4. These configurations are referred to as  $configuration\ a$ ,  $configuration\ b$ , and  $configuration\ c$  in this work and are as follows:

- I/O configuration a: In this configuration, one side of the load is connected to  $V_{in}$ , and the block has 3 ports to connect to other blocks' ports.

- I/O configuration b: In this configuration, one side of the load is connected to GND, and the block has 3 ports to connect to other blocks' ports.

• I/O configuration c: In this configuration, none of the IO/IO block's ports are connected to each other, and the block has 4 ports to connect to other blocks' ports.

Note that  $L^+$  and  $L^-$  are interchangeable.

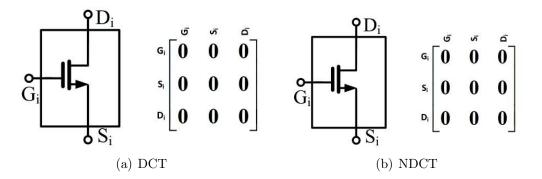

$T_i/T_i$  sub-matrix Generation: Since a transistor has three ports,  $T_i/T_i$  sub-matrix is a  $3 \times 3$  symmetric matrix. In order to have functional internal connections, the connections are made based on the following rules:

- When the gate of a transistor is connected to its source, the transistor is turned off. Therefore, the gate of a transistor is not allowed to connect to its source.

- When the drain of a transistor is connected to its source, the transistor is short circuited. Therefore, the drain of a transistor cannot be connected to its source.

Based on the above rules, the  $T_i/T_i$  sub-matrix has only two possible configurations: gate and drain are connected, or none of the ports are connected to each other.

In Fig. 3.5, the two configurations and the corresponding matrices are shown. The functionality of the two internal Transistor block configurations are described in the following:

- $T_i/T_i$  Configuration DCT: In this configuration, there is a connection between drain and gate terminals of a transistor. When the drain of a transistor is connected to its gate, the transistor is called a diode-connected transistor (DCT) and acts as a non-linear resistor. In this work we are looking for amplifier circuits, and therefore circuits where all transistors are DCTs are not considered as their voltage gain is less than 1.

- $T_i/T_i$  Configuration NDCT: In this configuration, the transistor's ports are not connected to each other and are denoted as non-diode-connected transistors (NDCT).

Figure 3.5: All possible T block configurations: (a) when the drain is connected to the gate (DCT) and (b) when the ports are not connected to each other (NDCT).

#### Generation of Blocks Interconnections

Once the I/O and Transistor block configurations have been generated, the interconnections between them needs to be determined. Circuit rules governing these interconnections and possible configurations are explained in the following.

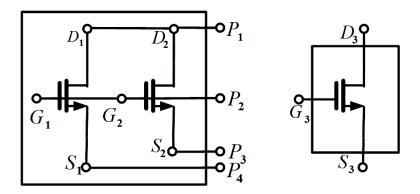

# $T_i/T_j$ sub-matrix generation

First, the possible configurations of connections between the two transistors, i.e.,  $T_i/T_j$  ( $i \neq j$ ) sub-matrix, called Connected 2 Transistors, C2T, are generated. Each C2T block is stored in a database for future use in connection to other circuit components. The advantage of generating C2T blocks and storing them is that the number of ports considered at each stage is reduced, limiting the number of possible connections that can be made when connecting to other circuit blocks. In addition, each C2T will have a small set of rules to avoid duplicate circuits, and ensure the uniqueness of larger circuits.

### IO/T sub-matrix generation

At this stage, we have connected the transistors to each other and the I/O block elements to each other. But the connections between the I/O block and the transistors needs to be constructed. To build the IO/T sub-matrix, all possible interconnections between the ports of the I/O block,  $GND, V_{in}, L^+$  and  $L^-$ , and the ports of the transistors block,

$G_1, S_1, D_1, G_2, S_2$  and  $D_2$ , need to be constructed. For this, all internal connections of the blocks have to be respected. For example, if GND and  $L^-$  are connected, and if  $G_1$  become connected to GND,  $IO/T_{11} = 1$ , then  $L^-$  and  $G_1$  have to be connected as well, i.e.  $IO/T_{31} = 1$ . The same argument applies to any open circuit inside a block. For example, if  $G_1$  become connected to GND,  $IO/T_{11} = 1$ , then there should be no connection between  $V_{in}$  and  $G_1$ ,  $IO/T_{21} = 0$  as GND and  $V_{in}$  cannot be connected.

In the following the algorithm of connecting C2T and I/O blocks is described. This algorithm is later implemented in MATLAB as part of ADA. The first connection is made between the first element in the I/O block, GND and the first element of the transistors,  $G_1$ , by setting  $IO/T_{11}$  to either 1 or 0. The corresponding values of all other corresponding rows are also set to either 0 or 1 based on the internal block connections. The values of the elements of the next rows are dependent on the configuration of the I/O block and are explained as follows:

- configuration a: In this configuration, the second and the third row are identical,  $V_{in}$  is connected to  $L^-$ , and the values of the elements of only one row can be decided. The elements of the other two rows can be permuted depending on the internal transistor blocks configurations.

- configuration b: In this configuration, the first row and the third row are identical, GND is connected to  $L^-$ , and the values of the elements of only one of the rows can be decided. The elements of the other two rows can be permuted depending on the internal transistor blocks configurations.

- configuration c: In this configuration, all rows are independent and the permutations of the elements depend on the internal transistor blocks configuration.

The algorithm for generating the IO/T block is shown in Fig. 3.6.

Figure 3.6: The algorithm for generation of the IO/T sub-matrix

Figure 3.7: The CM for 3-transistor circuit and its sub-matrices

### 3.3.2 Multiple Transistors Circuits Generation

In this section, the proposed method to generate all possible circuit configurations with two transistors is expanded to the generation of circuits with a larger number of transistors. To illustrated this, circuits with three transistors are considered to show the process of extending the method to larger circuits. For circuits with three transistors, the size of the CM is increased to  $13 \times 13$ , as shown in Fig. 3.7, where, the  $T_1/T_2$ ,  $T_1/T_3$ ,  $T_2/T_3$ , and  $T_3/T_3$  represent the connections between the three Transistor blocks, and  $T_3/T_3$  sub-matrix shows the internal connections Transistor 3  $(T_3)$  block. In Fig. 3.8, a sample circuit with three transistors and its CM are illustrated.

In order to generate circuits with three transistors, first internal configurations of the I/O block, and each transistor are generated as before: three possible configurations for the I/O block and two configurations for each T block. Then, the connectivity between the transistors needs to be determined. First, in order to generate  $T_i/T_j$  sub-matrices, two transistors are connected to each other to obtain the corresponding C2T blocks as has been discussed in Section 3.3.1. After generating the C2T block, it is connected to the third

Figure 3.8: A sample circuit with three transistors (biasing not shown) and its CM.

Figure 3.9: An example of a C2T block and  $T_3$  block.

transistor,  $T_3$ . During this step, the number of ports in the C2T block is related to the configuration of the transistors inside the block. Since the minimum number of connections between two transistors is 1 and the maximum is 3, the number of ports in a C2T block varies between 3 to 5. In addition,  $T_3$  has two configurations: DCT and NDCT. Note, in this thesis transistor  $T_1$  is not allowed to be DCT to make sure that at least one of the transistors can have gain.

In Fig. 3.9, an example of a C2T block and  $T_3$  block are shown. When connected, a C2T and  $T_3$  form a block called C3T block.

After generation all C3Ts, the final step in the proposed algorithm is to connect the I/O

block to the transistors in the similar fashion as was discussed earlier in Section 3.3.

In order to generate circuits with four transistors, the procedure is as same as generating circuits with three transistors, where all generated 3-transistor blocks (C3T) are connected to the fourth transistor. However, the process of generating other sub-matrices is as same as generating them for circuits with three transistors.

## 3.4 Theoretical Proof of Circuit Generation Methodology

In this section, the number of possible circuit topologies with two transistors is calculated. Also the maximum number of all possible C3T configurations is found.

#### 3.4.1 2-transistor Circuits

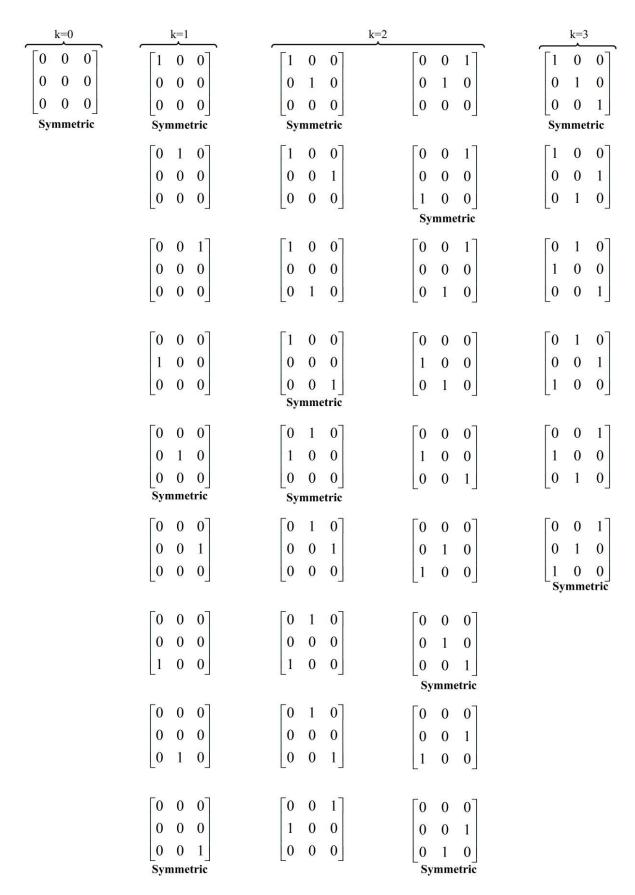

To show that all possible topologies with two transistors are found by the circuit generation method above, we first prove that the generation of the C2T matrices can be reduced to non-attacking Rooks problems, and then derive the maximum number of C2T blocks that can be generated.

Next, we calculate the total number of circuits that can be made using the generated C2T blocks and different I/O block configurations. This number is the maximum number of circuit topologies that can be generated. Finally, we define a set of rules that differentiates the functional and non-functional circuits and calculate the number of functional circuits. The mentioned rules and procedures are described in detail in the following sections.

### Generation of All C2T Blocks:

Based on non-attacking Rooks problems the number of ways to place 0 to k rooks on an  $m \times n$ ,  $n \le m$  board, where  $k = \min\{n, m\} = n$ , can be calculated. There should be no more than one rook in same row or column. A Rook polynomial is a generating polynomial that the coefficients encode information about the number of ways to place k rooks on a board and powers encode information about the number of rooks [35]. A Rook polynomial

of a  $m \times n$  board is:

$$R_{m,n} = \sum_{k=0}^{\min(m,n)} r_k(m,n)(x)^k,$$

(3.1)

where x does not represent a variable, and its coefficients,  $r_k(m, n)$ , represent the number of ways to place k rooks, which is x's power. The rook polynomial is obtained by solving:

$$R_{m,n}(x) = n! x^n L_n^{m-n}(-x^{-1}), (3.2)$$

where,  $L_n^{m-n}(.)$  is the Laguerre polynomial of degree n:

$$L_n^{\alpha}(x) = \sum_{i=0}^n (-1)^i \binom{n+\alpha}{n-i} \left(\frac{x^i}{i!}\right). \tag{3.3}$$

In order to calculate the total number of C2T blocks by using Rook polynomial, a small set of rules are defined as follows:

Lemma 1: A C2T block for two non-diode connected transistors is a matrix in which each row or column has at most one non-zero element: In the C2T matrix, if there are two or more non-zero elements in a row, then the ports of the transistor represented by the non-zero columns are connected, which is unacceptable.

Lemma 2: A C2T block with one DCT results in a sub-matrix in which each row or column has at most one non-zero element: If one of the transistors is diode-connected, then its gate and drain are connected. In this case the drain column of the DC transistor can be eliminated and the resultant sub-matrix representing the gate, source and drain of the NDCT makes up the rows of the new sub-matrix and the gate and the source of the DCT make the columns. Hence, this new sub-matrix is a  $3 \times 2$  sub-matrix that, based on lemma 1, has at most one non-zero element in each row or column.

Lemma 3: Construction of the C2T block is equivalent to the non-attacking Rook's problem with a 3 × 3 board, when there is no DCTs in the circuits, and 3 × 2 board, when one transistor is DCT. Based on Lemmas 1 and 2, each C2T matrix, i.e.  $T_i/T_j$  sub-matrix, is a matrix, which has in each row or column only one non-zero element. When there is no DCT in a circuit, C2T matrix is a  $3 \times 3$  non-attacking rooks problem. The number of rooks, k, for the C2T blocks can vary from 0 to 3, where 0 means no connections between the two transistors and 3 means that the three ports of the transistors are connected to each other. When one of the transistors is diode connected (in  $T_i/T_j$ , j > i only  $T_j$  can be diode-connected to have only one DCT in C2T block), the column representing  $D_j$ , drain of the DCT, is not considered in the C2T block, hence the C2T matrix is a  $3 \times 2$  non-attacking rooks problem, where the number of rooks, k, can vary from 0 to 2 and where 0 means no connections between the two transistors and 2 means that the two ports of the DCT, the gate and the source, are connected to the 2 ports of the NDCT.

Theorem 1: The number of all possible C2Ts is 13 when there is one DCT in the circuits and is 34 when there is no DCT in the circuits.

Based on Lemma 3, the C2T construction problem is equivalent to the non-attacking Rooks' problem. When one transistor is diode connected, m = 3, n = 2. Hence the Rook polynomial will be:

$$R_{3,2}(x) = 6x^2 + 6x^1 + 1x^0, (3.4)$$

which means that 1 configuration for zero connections between two transistors, and 6 configurations for one and two connections between two transistors each. It should be mentioned that there are no symmetric C2T blocks when one of the transistors is diode connected, hence all the C2T blocks are unique. The total number of configurations in this case is: 6+6+1=13.

When there is no DCT in the circuits, m = n = k = 3, and the Rook polynomial equation will be:

$$R_{3,3}(x) = 6x^3 + 18x^2 + 9x + 1x^0. (3.5)$$

Based on (3.5), there is only one way to arrange the two transistors when they have no connected ports. When there is only one connection, there can be at most 9 arrangements,

and when there are 2 and 3 connections, then there are 18 and 6 arrangements, respectively. Hence, when there is no DCT, we have at most  $R_{3,3}(x) = 6 + 18 + 9 + 1 = 34$  configurations.

$R_{3,3}(x)$  represents the maximum number of possible C2T. However, some configurations can be equivalent, where one  $T_i/T_j$  sub-matrix is transpose of the other. Therefore, to check for uniqueness of a circuit,  $Lemma\ 4$  is proposed.

Lemma 4: Two C2T blocks, C2T<sub>1</sub> and C2T<sub>2</sub>, result in the equivalent circuit, when the corresponding matrices,  $T_i/T_{j_1}$  and  $T_i/T_{j_2}$ , are  $T_i/T_{j_1}^T = T_i/T_{j_2}$  and  $T_i/T_{j_1} = T_i/T_{j_2}^T$ .

Swapping two transistors leads to generating two different C2T; however, the corresponding generated circuits are the same. When two transistors are swapped, the row and column of the  $T_i/T_j$  sub-matrices are transposed. For instance, as shown in Fig. 3.10, the  $T_i/T_j$  sub-matrix of Fig. 3.10.(a) is transpose of the  $T_i/T_j$  sub-matrix of Fig. 3.10.(b).

Theorem 2: The number of unique C2Ts is 13 when there is only one DCT and the number of unique C2T is 23, when there is no DCT.

The total number of unique configurations when there is no DCT for circuits with 2 transistors,  $n_{NDC2_k}$ , is calculated as follows: