The Vault

Open Theses and Dissertations

2012-09-26

# Modeling and Calibration of Multi-Port Based Receiver Systems Mitigating System Imperfections and Hardware Impairments

Hasan, Abul

Hasan, A. (2012). Modeling and Calibration of Multi-Port Based Receiver Systems Mitigating System Imperfections and Hardware Impairments (Master's thesis, University of Calgary, Calgary, Canada). Retrieved from https://prism.ucalgary.ca.doi:10.11575/PRISM/26935 http://hdl.handle.net/11023/229

Downloaded from PRISM Repository, University of Calgary

### UNIVERSITY OF CALGARY

Modeling and Calibration of Multi-Port Based Receiver Systems Mitigating System

Imperfections and Hardware Impairments

by

### Abul Hasan

### A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

SEPTEMBER, 2012

© Abul Hasan 2012

### Abstract

Six-port based homodyne receiver architecture is a low power and low cost alternative to the conventional homodyne receiver using diode based mixers. The problems of dcoffset, I/Q cross-talk, high conversion loss and nonlinearities due to diode mixers are some of the issues that make the conventional homodyne receiver architecture not very useful for practical low power communication systems employing envelope varying modulation scheme signals. The radio frequency (RF) front-end in a typical six-port based receiver (SPR) consists of a linear and passive six-port junction circuit that can be easily designed to cover a very large bandwidth. This makes the SPR concept an attractive candidate for software defined radio (SDR) receiver applications. The six-port based RF front-end provides low loss and doesn't pose any nonlinearity issues. Sources of errors due to circuit and system components impairments can be easily calibrated and compensated in a SPR system as shown in this thesis.

### Acknowledgements

In the name of Allah, the Most Gracious, the Most Merciful

All praises and thanks be to Allah, the Lord of the worlds, who sent His last messenger (peace and blessings be upon him) who taught the humanity 'whoever doesn't thank people, doesn't thank Allah'.

First of all, I would like to thank my research supervisor, Dr. Mohamed Helaoui and Prof. Fadhel M. Ghannouchi, Director, iRadio Laboratory, for giving me this opportunity to carry out the research in their laboratory. I am truly indebted to them for their time, encouragement, and support. Most of the research ideas contained in this thesis are a direct result of the fruitful discussions I had with them at numerous occasions.

I would also like to take this opportunity to thank the iRadio lab members for their help and intellectually stimulating discussions.

Last but not the least; I would like to thank my parents, siblings, and my wife for their immense love, support, and prayers.

In the loving memory of my Grandfather...

# **Table of Contents**

| Abstract                                                             | ii   |

|----------------------------------------------------------------------|------|

| Acknowledgements                                                     | iii  |

| Dedication                                                           | iv   |

| Table of Contents                                                    | v    |

| List of Tables                                                       |      |

| List of Figures and Illustrations                                    | viii |

| List of Symbols, Abbreviations and Nomenclature                      | xi   |

| CHAPTER ONE: INTRODUCTION                                            | 1    |

| 1.1 Signal Representations                                           |      |

| 1.2 Modern Receiver Architectures                                    |      |

| 1.2.1 Super-heterodyne Receiver Architecture                         |      |

| 1.2.2 Homodyne or Direct Conversion or Zero-IF Receiver Architecture |      |

| 1.2.3 Low-IF Receiver Architecture                                   | 8    |

| 1.3 Architecture Comparison and Trade-off                            |      |

| 1.4 Six-Port Based Receiver System                                   |      |

| 1.4.1 Theory of a Six-Port Based Receiver                            |      |

| 1.5 Limitations of the Six-Port Based Receiver Systems               |      |

| 1.6 Building Blocks of an SPR System                                 | 15   |

| 1.7 Thesis Outline                                                   | 16   |

| 1.8 Thesis Contributions                                             | 16   |

| 1.9 Conclusions                                                      | 18   |

|                                                                      | 20   |

| CHAPTER TWO: DIODE DETECTOR MODELING AND LINEARIZATION               |      |

| 2.1 CW Linearization Techniques                                      |      |

| 2.1.1 Look-up-table (LUT) Based Linearization Technique [16]         |      |

| 2.1.2 'Hoer-Roe-Allred (HRA)' Model [17]                             |      |

| 2.1.3 'Zhaowu-Binchun (ZB)' Model [18]                               |      |

| 2.1.4 'Polynomial (P)' Model [19]                                    |      |

| 2.2 Diode Detectors for Peak Power Detection Applications            |      |

| 2.2.1 Measurement Test Setup                                         |      |

| 2.2.2 Measurement Results                                            |      |

| 2.3 Diode Detector Linearizer for Wideband Signals                   |      |

| 2.3.1 Diode Detector Linearizer for Modulated Signals                |      |

| 2.4 Conclusion                                                       | 38   |

| CHAPTER THREE: NONLINEAR MODELING AND CALIBRATION OF SIX-            |      |

| PORT RECEIVER                                                        |      |

| 3.1 Nonlinear Modeling of SPR systems                                |      |

| 3.2 Nonlinear Calibration of SPR systems                             |      |

| 3.2.1 Receiver Calibration Step (P <sub>k</sub> to T reduction)      |      |

| 3.2.2 Phase Alignment Step (T to R estimation)                       |      |

| 3.3 Implementation of SPR System                                     |      |

| 3.4 Nonlinear Auto-Calibration Procedure                             |      |

| 3.4.1 Receiver Calibration                                           | 48   |

| 3.4.2 Phase Alignment Box Calibration                              | 49 |

|--------------------------------------------------------------------|----|

| 3.4.3 Power Detectors Linearization                                |    |

| 3.5 Measurement Results                                            | 50 |

| 3.6 Linear vs. Nonlinear Modeling of Six-Port Receiver system      | 53 |

| 3.6.1 Nonlinear Modeling of Six-Port Junction                      |    |

| 3.6.2 Linear Modeling of Six-Port Junction                         |    |

| 3.7 Conclusions                                                    |    |

| CHAPTER FOUR: LINEAR MODELING AND CALIBRATION OF SIX-PORT          |    |

| RECEIVER                                                           | 57 |

| 4.1 Linear Modeling and Calibration of Six-Port Receiver           |    |

| 4.2 Single Step Linearization and Calibration of Six-Port Receiver |    |

| 4.3 Practical Limitations of a Real Six-Port Based Receiver        |    |

| 4.4 Black Box Modeling of Six-Port Receiver                        |    |

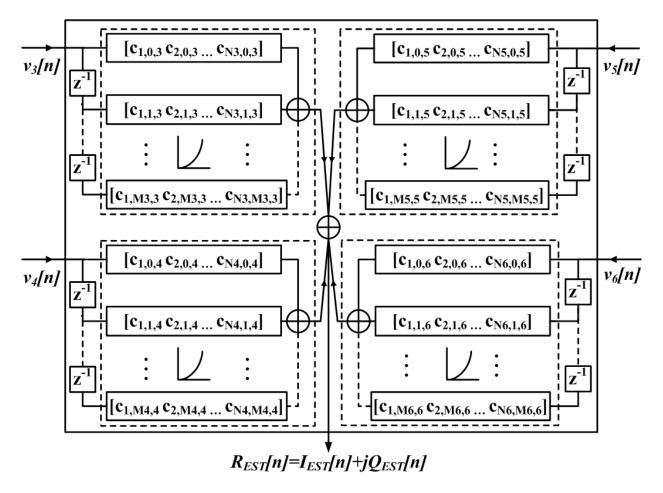

| 4.4.1 Modeling Diode Detector Nonlinearity and Memory Effect       |    |

| 4.4.2 Modeling Frequency Response of Six-Port Junction             |    |

| 4.4.3 Black-Box Model for Complete SPR System                      |    |

| 4.5 Calibration Procedure                                          |    |

| 4.6 Implementation of SPR system                                   |    |

| 4.7 Measurement Results                                            |    |

| 4.7.1 Measurement Limitations                                      | 81 |

| 4.8 Conclusions                                                    | 81 |

| CHAPTER FIVE: CONCLUSIONS AND FUTURE WORKS                         | 83 |

| 5.1 Future Works                                                   |    |

| DEEDENCES                                                          | 87 |

# **List of Tables**

| Table 2.1: Comparison of CW and proposed peak power detector linearizer                                                      | 29 |

|------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2: Performance summary of the proposed model of the power detector linearizer                                        | 35 |

| Table 4.1: Comparison of conventional and proposed calibration approach                                                      | 73 |

| Table 4.2: SPR system performance summary                                                                                    | 80 |

| Table 4.3: Comparison with recent reported works                                                                             | 80 |

| Table 5.1: Summary of the conventional linear, and the proposed linear and the nonlinear modeling and calibration approaches | 84 |

# **List of Figures and Illustrations**

| Figure 1.1: Block diagram of an ideal software defined radio receiver system                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: A practical implementation of the software defined radio receiver system 3                                                                             |

| Figure 1.3: Complex signal representation and frequency up-conversion in a typical modern transmitter                                                              |

| Figure 1.4: Block diagram of a typical super-heterodyne receiver                                                                                                   |

| Figure 1.5: Block diagram of a typical direct conversion receiver                                                                                                  |

| Figure 1.6: Block diagram of a typical low-IF receiver                                                                                                             |

| Figure 1.7: Block diagram of a generic six-port based receiver                                                                                                     |

| Figure 2.1: Block diagram of a diode based power detector cascaded with its linearizer.                                                                            |

| Figure 2.2: Diode based peak/rms power detector in cellular handset power control application                                                                      |

| Figure 2.3: Test setup for the peak power detector characterization and linearization 25                                                                           |

| Figure 2.4: Peak power detector characteristics for different excitation waveforms at a carrier frequency of 2.5GHz                                                |

| Figure 2.5: Linearized peak power versus the actual input peak powers for different types of excitation signals                                                    |

| Figure 2.6: Proposed peak power linearizer using calibration constant                                                                                              |

| Figure 2.7: Input envelope power waveform and the linearized envelope power waveforms using CW linearizers for a diode power detector                              |

| Figure 2.8: Behaviour of a diode power detector excited by a 64QAM modulated signal having 1MHz bandwidth and by a CW excitation at a carrier frequency of 2.5GHz. |

| Figure 2.9: NMSE performance of a memory polynomial based linearizer for Shottky diode power detector                                                              |

| Figure 2.10: Measured and modeled behaviour of a diode power detector excited by a 64QAM modulated signal having 1MHz bandwidth at a carrier frequency of 2.5GHz.  |

| Figure 2.11: Actual input power waveform and the linearized output power                                                                       |      |

|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| waveforms for a 64QAM modulated signal having 1MHz bandwidth at a carrier frequency of 2.5GHz.                                                 | . 37 |

| Figure 2.12: Plots of linearized output envelope powers versus actual input envelope power for different diode detector linearizers            | . 38 |

| Figure 3.1: Evaluation of T from equation (3.4) in the 'Receiver Calibration' step                                                             | 43   |

| Figure 3.2: Receiver calibration and phase alignment steps for nonlinear calibration of a SPR system                                           |      |

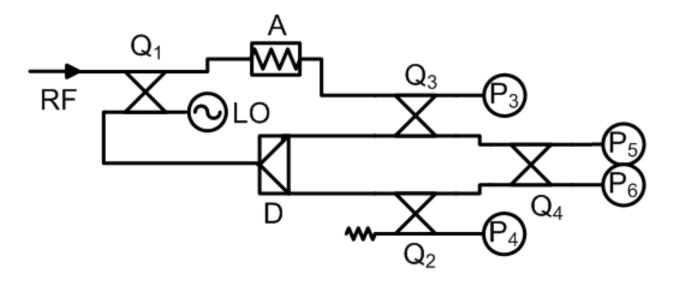

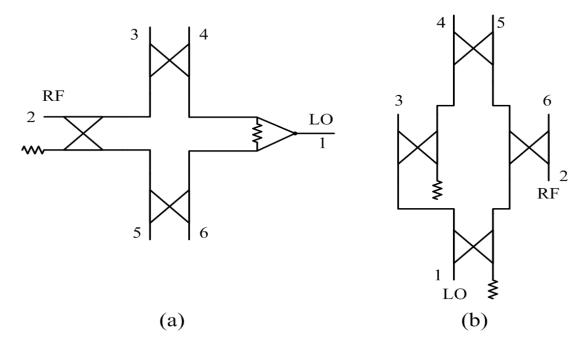

| Figure 3.3: Structure of six-port junction for receiver architecture.                                                                          | 45   |

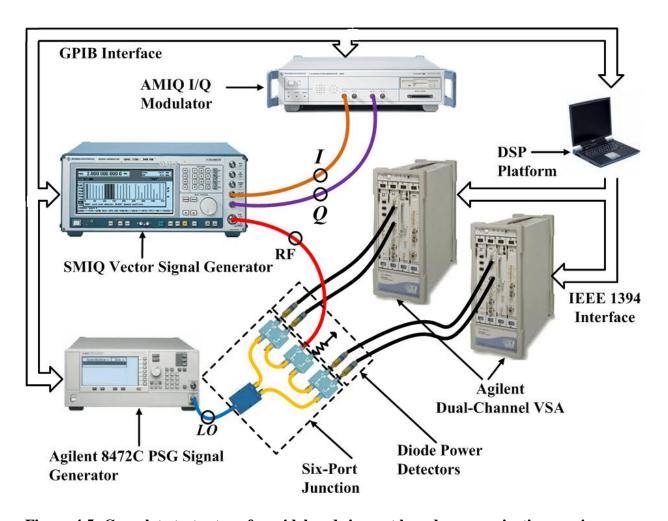

| Figure 3.4: Test set up for the six-port based receiver system                                                                                 | 46   |

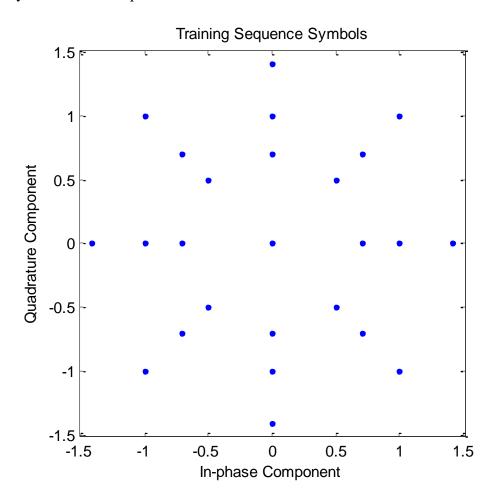

| Figure 3.5: Constellation points of training sequence symbols.                                                                                 | 47   |

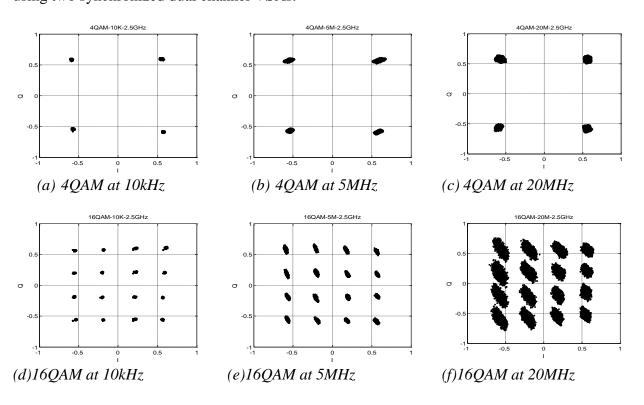

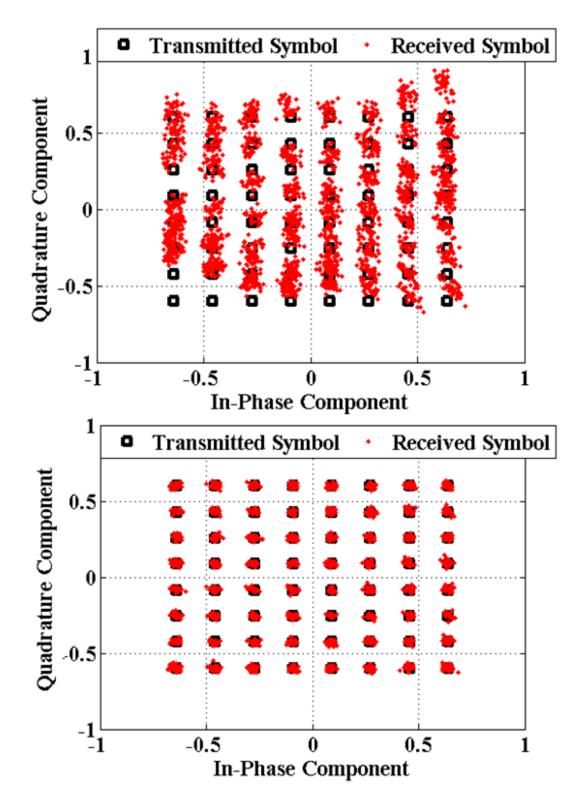

| Figure 3.6: Constellation points of transmitted and received symbols of 4QAM and 16QAM symbols at different symbol rates.                      | 50   |

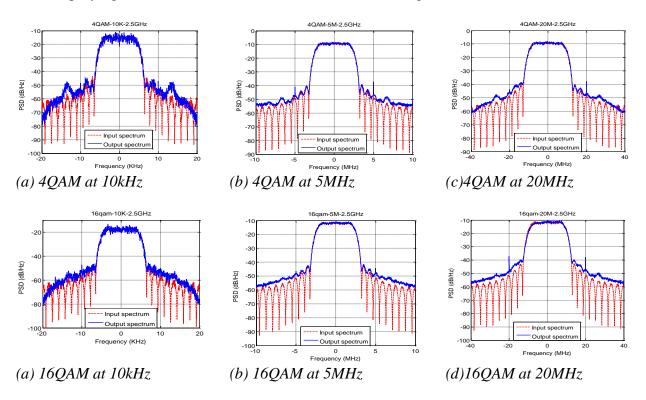

| Figure 3.7: Frequency spectrum of the transmitted and the received symbols for 4QAM and 16QAM symbols at different symbol rates                | 51   |

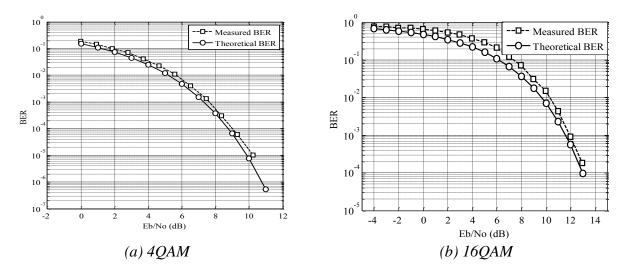

| Figure 3.8: Theoretical and measured BER plot for (a) 4QAM, and (b) 16QAM symbols at 10kHz symbol rate.                                        | . 52 |

| Figure 3.9: Implementation of the six-port junction suitable for (a) linear modeling and calibration (b) nonlinear modeling and calibration.   | 54   |

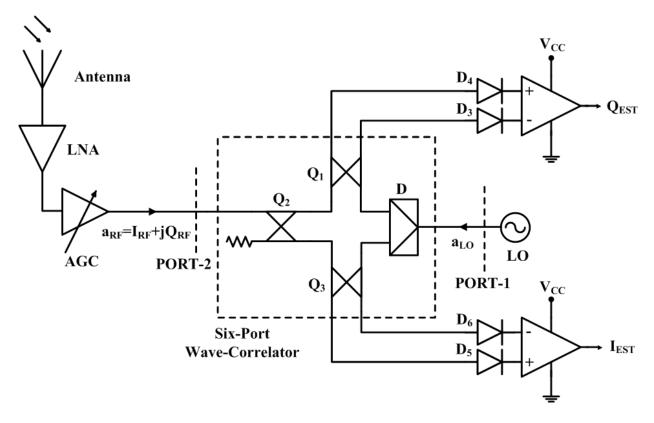

| Figure 4.1: A typical six-port based receiver system architecture suitable for linear modeling and calibration                                 | 60   |

| Figure 4.2: A typical six-port based receiver system architecture employing quasi-ideal system components.                                     | 62   |

| Figure 4.3: Modeling the frequency response of the six-port junction                                                                           | 66   |

| Figure 4.4: Proposed model for a SPR system taking into account all the identified system impairments.                                         | 69   |

| Figure 4.5: Complete test set-up for wideband six-port based communication receiver                                                            | 72   |

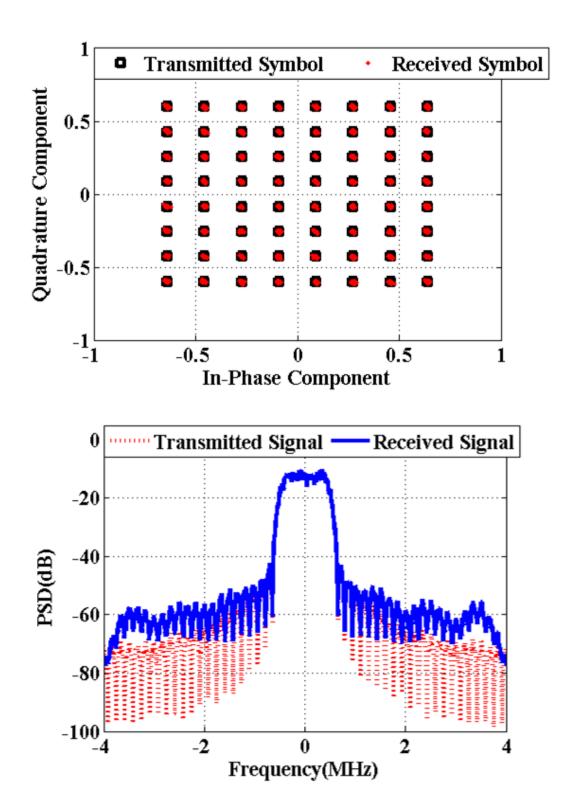

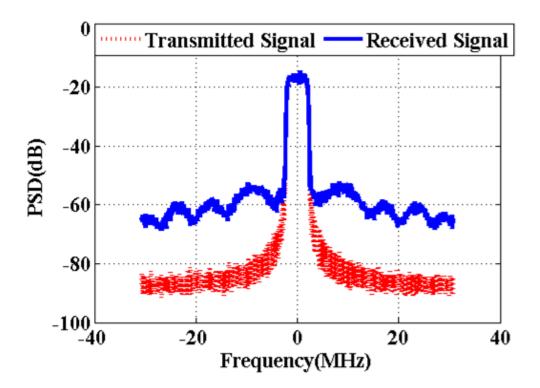

| Figure 4.6: Constellations (Top) and spectrums (Bottom) of received and transmitted symbols for 64-QAM signals having 1MHz bandwidths [6Mb/s]  | . 74 |

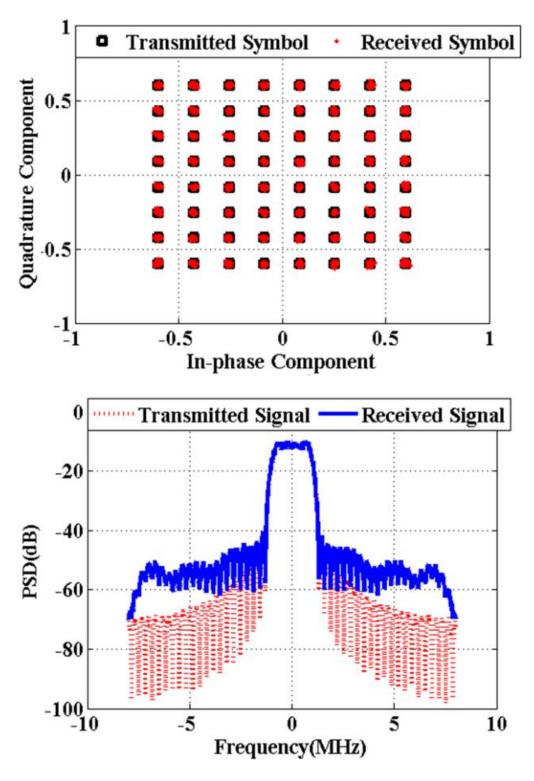

| Figure 4.7: Constellations (Top) and spectrums (Bottom) of received and transmitted symbols for 64-QAM signals having 2MHz bandwidths [12Mb/s] | . 75 |

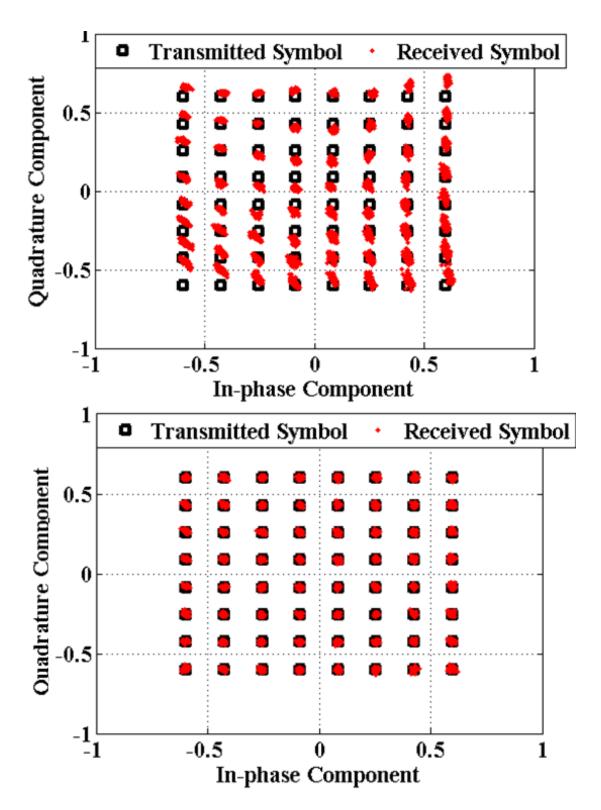

| having 2MHz bandwidths; Conventional Approach (Top), Proposed Approach (Bottom).                                                                                 | . 76 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4.9: Constellations of 64-QAM modulated transmitted and received symbols having 4MHz bandwidths; Conventional Approach (Top), Proposed Approach (Bottom). | . 77 |

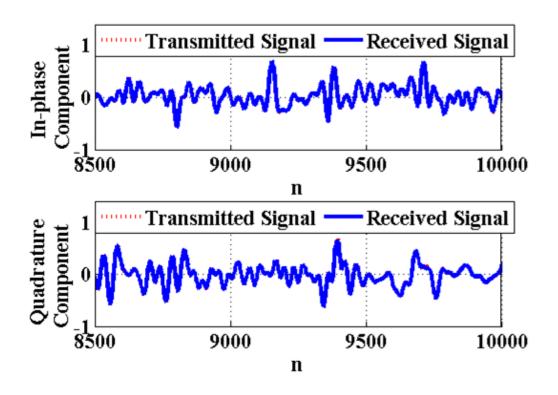

| Figure 4.10: Transmitted and received I/Q components (Top) and frequency spectrums (Bottom) of WCDMA signal.                                                     | . 78 |

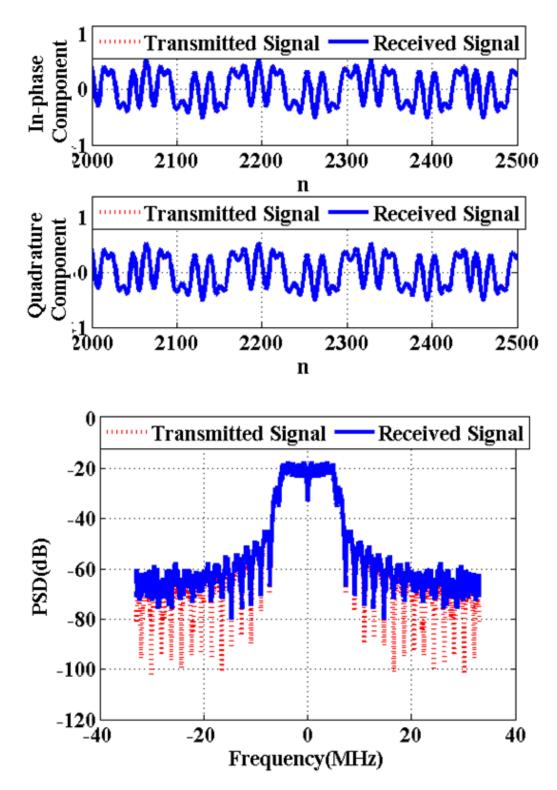

| Figure 4.11: Transmitted and received I/Q components (Top) and frequency spectrums (Bottom) of WLAN signal.                                                      | . 79 |

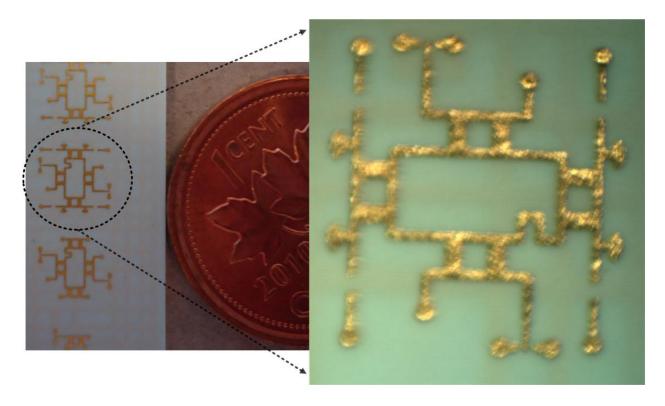

| Figure 5.1: Six-port based receiver RF front-end circuit designed in LTCC technology for 60 GHz applications.                                                    |      |

### List of Symbols, Abbreviations and Nomenclature

Symbol Definition

ADC Analog-to-Digital Converter AGC Automatic Gain Controller

BER Bit Error Rate

BPF Band Pass Filter

BW Bandwidth

CW Continuous Wave DC Direct Current

EVMError Vector Magnitude $f_c$ Carrier Frequency $f_{im}$ Image FrequencyGHzGiga Hertz

DSP Digital Signal Processor/Processing

GMSK Gaussian Minimum Shift Keying

GSM Global System for Mobile Communication ICT Information and Communication Technology

IF Intermediate Frequency

kHz Kilo Hertz

LNA Low Noise Amplifier

LO Local Oscillator

LPF Low Pass Filter

LUT Look-Up-Table

LTCC Low Temperature Co-fired Ceramic NCO Numerically Controlled Oscillator

MHz Mega Hertz

NMSE Normalized Mean Square Error

PA Power Amplifier PC Personal Computer

PAPR Peak-to-Average-Power-Ratio

QAM Quadrature Amplitude Modulation

RF Radio Frequency

RMS/rms Root Mean Square

Rx Receiver

SDR Software Defined Radio

SPR Six-port Based Direct Conversion Receiver

Tx Transmitter

UMTS Universal Mobile Telecommunications

System

VNA Vector Network Analyzer

VSA Vector Signal Analyzer

WCDMA Wideband Code Division Multiple Access

WLAN Wireless Local Area Network

### Chapter One: Introduction

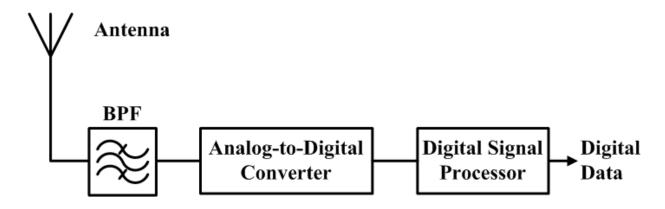

Continuous evolution of communication standards in today's information and communication technology (ICT) sphere demands frequent changes in the communication hardware and the supporting software. Also, a single communication device supporting multiple communication standards might require multiple transceiver units to cater for each standard requirement. The global research community is looking for a generic architecture for communication transceiver units, which can accommodate multiple communication standards or changes in the communication standards and protocols without requiring multiple transceiver units or replacing the existing hardware systems. Software defined radio (SDR) architecture promises to fulfill this requirement by virtue of its flexibility and adaptability to the new communication standard and protocol by changing the accompanying software running on its platform [1]. An SDR transceiver system would include both the transmitter and the receiver subsystems, but the focus of the work carried out in this thesis is on the architectures and performances of wireless receivers suitable for SDR applications with special consideration to multi-port based receiver systems. An ideal SDR receiver system will sample the communication signal directly at the receiving antenna [1]. Such a system will require a very broadband (frequency band over which the SDR system is expected to function) antenna and an analog-to-digital converter (ADC) operating at a sampling frequency of at least twice that of the maximum frequency supported by the receiver system. A comparably faster digital signal processor will be required to process the digitized information. The requirement on the sampling speed of the ADC system and thus the signal processor speed can be relaxed by employing another receiver architecture based on subsampling or bandpass sampling technique [2], [3]. The subsampling receiver architecture provides relaxation in the sampling speed at the cost of performance degradation due to inherent

Figure 1.1: Block diagram of an ideal software defined radio receiver system.

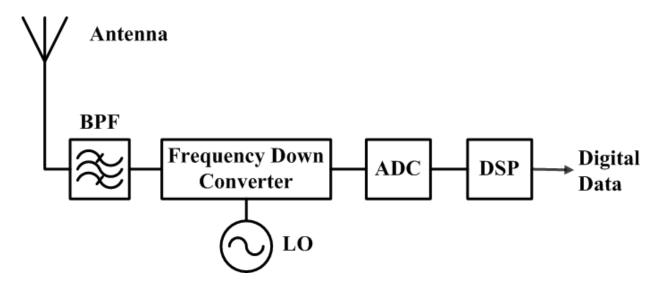

issues of sampling jitter and folded noise problem [3]. The block diagram of an ideal SDR receiver system is shown in Figure 1.1. The requirements from the ADC system for a truly SDR system can't be met with the existing state-of-art technology nor are foreseeable in near future [1]. Another interesting option to implement the SDR concept using physically realizable components is to bring down the required information-bearing signal present in a frequency band around a carrier frequency to a lower frequency band where it can be processed more efficiently. This implementation of the SDR system concept necessitates the use of a local oscillator (LO) signal to select a particular band of frequency. The block diagram of this implementation of the SDR receiver concept is shown in Figure 1.2. There are a number of implementations for the frequency down conversion circuitry; the most common of which are a) Super-heterodyne architecture b) Homodyne or Direct down conversion or Zero-IF architecture, and c) Low IF architecture. The details and the pros and cons of these architectures for SDR applications are discussed in Sections 1.2 and 1.3. In most cases, the frequency down-conversion receiver architectures use diode based mixer circuitry to perform the frequency down conversion operation. Traditional diode based mixers require high LO power and are very power inefficient [4], [5]. The LO signal must switch the diodes on and off, and drive them deep into the saturation.

Figure 1.2: A practical implementation of the software defined radio receiver system.

This requires high LO signal power and generates harmonics and distortion at the output port of the mixer. They introduce nonlinearities and thus undesired frequency harmonics in the RF chain of the receiver system [6]. In this thesis, we have explored an alternative for the conventional mixers that is low power and cost effective and it can be designed for a very broad frequency band using passive RF and microwave circuit components. The investigated receiver architecture is known as six-port based direct down conversion receiver (SPR) architecture [7]-[11]. The SPR system consists of a passive, linear, six-port based microwave circuit, the four ports of which are terminated with microwave power detectors. The other two ports are used to supply the received communication signal and the LO signal. The details of a generic SPR system and the principles behind its working are explained in Section 1.4. Before delving into the details of the modern receiver architectures, we will briefly describe the mathematical model for modern communication signals and their representations in the frequency domain for system analysis purposes.

### 1.1 Signal Representations

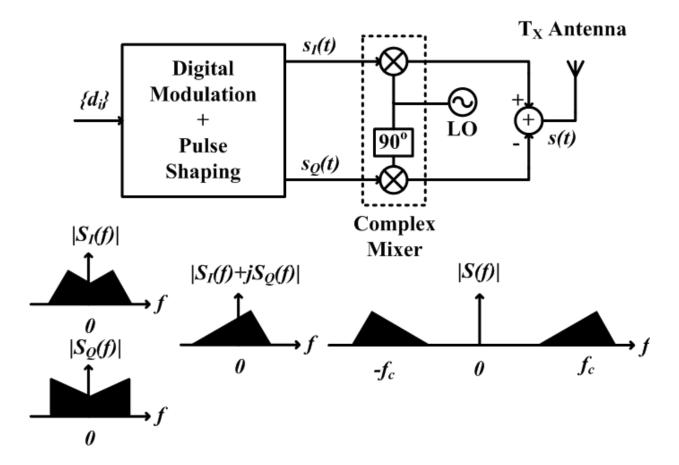

Modern communication systems use complex signal representation for the baseband signals. A real world message is digitized and coded in terms of a bit sequence  $\{d_i\}$  which is further modulated digitally and mapped to a stream of message symbols with the help of two orthogonal signals, namely, the in-phase component signal and the quadrature component signal. If  $s_I(t)$  and  $s_Q(t)$  represent the in-phase and the quadrature components, respectively, of a digitally modulated baseband signal, then the complex baseband signal s(t) is written as

$$\widetilde{s(t)} = s_I(t) + js_O(t); j = \sqrt{-1}$$

(1.1)

The Fourier transforms of the real signals  $s_I(t)$  and  $s_Q(t)$  will be complex conjugate symmetric in the frequency domain which is not the case for the complex baseband signal s(t) [12]. The complex baseband signal s(t) is frequency up-converted to a desired carrier frequency  $f_c$  in the transmitter using a complex mixer. The passband or bandpass representation of the communication signal transmitted by the transmitter is denoted as s(t).

$$s(t) = Re\{\widetilde{s(t)}e^{j2\pi f_c t}\} = s_I(t)\cos(2\pi f_c t) - s_Q(t)\sin(2\pi f_c t)$$

(1.2)

The model for the complex baseband signals, the complex mixer and the bandpass signal used in this thesis is shown pictorially in Figure 1.3. The fundamental task of a communication receiver is to faithfully recover the complex baseband signal  $\widetilde{s(t)} = s_I(t) + js_Q(t)$ , that will in turn provide the originally transmitted information bits  $\{d_i\}$ .

### 1.2 Modern Receiver Architectures

To prepare ground for the introduction of the six-port based receiver system, we will first discuss about some of the modern receiver architectures being researched and prevalent in most of the today's commercially successful products. We will also discuss their advantages, disadvantages

Figure 1.3: Complex signal representation and frequency up-conversion in a typical modern transmitter.

and suitability for the software defined radio (SDR) applications.

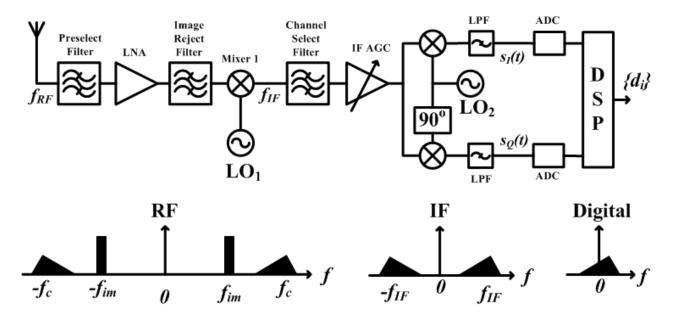

### 1.2.1 Super-heterodyne Receiver Architecture

The overwhelming majority of the contemporary radio receivers employ super-heterodyne architecture, which is also called the heterodyne architecture, [13], [14] to bring down the desired passband signal to the original baseband in two (or more) steps. In the first step of the frequency down conversion process, the desired passband signal is brought down to a fixed intermediate frequency (IF) band. In the last stage of the down conversion process, the IF band signal is brought down to the baseband frequency with the help of a complex mixer for further

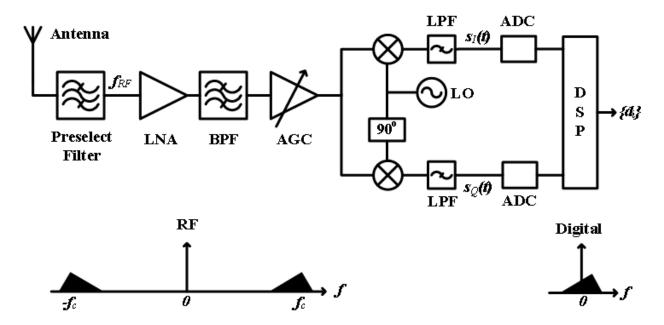

Figure 1.4: Block diagram of a typical super-heterodyne receiver.

processing and data extraction. The block diagram of a typical super-heterodyne receiver is shown in Figure 1.4. The fundamental problem with this architecture is the issue of image frequency. To eliminate this problem a bunch of filters are employed in this architecture that increases the overall size and the cost of the receiver system. The implementation of image reject filters limit the usefulness of this architecture for SDR applications. Modification in this basic super-heterodyne architecture (Weaver architecture, Hartley architecture) [15] is also used to solve the image frequency problem. Another problem with this architecture is the tedious frequency planning and the limitations on the frequency bands for different sections of the receiver in which the system or the subsystem could operate. This architecture is not ideally well suited for SDR applications covering a wide band of frequency in the receiver band supporting multiple communication standards.

### 1.2.2 Homodyne or Direct Conversion or Zero-IF Receiver Architecture

Homodyne or Direct Conversion or Zero-IF receiver architecture reduces the complexities and limitations of super-heterodyne receiver by eliminating the need of an IF stage [13], [14]. This architecture brings down the passband signal directly to the baseband in a single step. Homodyne architecture greatly simplifies the design of a receiver system. It takes much less space, it is more suitable for integration and the overall system cost is significantly reduced compared to the super-heterodyne architecture. The savings in terms of space and cost comes primarily due to removal of the image reject and other bulky and costly off-chip filter components. In homodyne architecture, the LO frequency is set exactly equal to the carrier frequency of the desired signal band and its phase is locked with the carrier signal phase. Though this architecture appears to be a natural one for frequency down conversion, it comes with some practical problems. The most severe of these problems are; DC offset, I/Q mismatch, selfmixing, LO leakage, 1/f noise and the second order distortions. If these problems are resolved, the homodyne architecture will make an ideal candidate for SDR applications. The six-port based direct down conversion receiver architecture solves these issues by using linear circuits and by avoiding the use of conventional diode based mixers. Sources of errors are calibrated and accounted for in the digital signal-processing block of the six-port based receiver system. It has been reported in [13] that the direct conversion architecture has not been used in any commercially successful product where the communication protocol employs a non-constant envelope signal. This is because the inherent errors in the conventional direct conversion receivers are corrected based on the signal profiles using DSP algorithms. The six-port based direct down-conversion architecture, investigated in this thesis, shows the usefulness of direct conversion receivers for non-constant envelops signals too. Block diagram of a typical direct

Figure 1.5: Block diagram of a typical direct conversion receiver.

conversion receiver is shown in Figure 1.5.

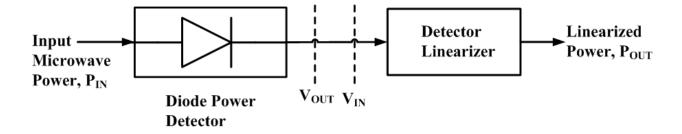

### 1.2.3 Low-IF Receiver Architecture

To harness the advantages of both the super-heterodyne and the homodyne architectures a new architecture for the receiver systems is used, which is called the low-IF receiver architecture [13], [14]. This architecture attempts to take advantage of super-heterodyne architecture by eliminating the DC-offset problem of homodyne architecture. In this architecture, the intermediate frequency (IF) is selected at a frequency from half of the signal bandwidth to some small multiple of it. Low-IF architecture brings the image band much closer to the desired band compared to super-heterodyne architecture. This image problem in low-IF architecture is solved using a complex bandpass filter known as polyphase filter, that removes the image frequency signal. The signal at the IF band is digitized and passed to the DSP block of the receiver system. In the DSP block, this digitized signal is brought down to the baseband using a numerically controlled oscillator (NCO) and processed further to extract the original transmitted data. This

Figure 1.6: Block diagram of a typical low-IF receiver.

architecture can achieve very high image rejection by using efficient signal processing algorithms in the DSP block of the system. Block diagram of a typical low-IF receiver system is shown in Figure 1.6.

### 1.3 Architecture Comparison and Trade-off

The most robust and superior performance architecture, employed in almost all the modern receiver systems, is the super-heterodyne architecture. This architecture offers superior sensitivity, selectivity, higher dynamic range but suffers from the image frequency problem and requires a tedious frequency planning. Image problem of this architecture necessitates the use of multiple bulky and costly filter components at different stages in the receiver line-up which put

limitations on the frequency bands over which the receiver system could operate. Ideally this architecture will not be suited for SDR applications that demand a very broad coverage in the frequency band.

Direct conversion receiver is well suited for SDR applications but it suffers from major disadvantages such as DC offset problem, self-mixing, LO leakage, 1/f noise and nonlinear distortions. Effect of some of the issues in this architecture is minimized if constant envelop modulation scheme signals are used in the communication. The signal statistics and the receiver calibration are used to minimize the error caused by some of these architectural problems. If nonconstant envelop signals are employed in the communication, the direct conversion receiver performance deteriorates and is not suitable for major communication applications.

Most of the problems of the direct conversion receiver architecture arise around the zero frequency or DC component of the signal in a narrow bandwidth. This problem is greatly simplified in the low-IF receiver architecture. One disadvantage of low-IF receiver architecture is the requirement of high levels of matching accuracy between components. The suppression of the image must be higher. In some cases, the image signal can be higher than the desired signal. Though the DC offset problem is resolved but image frequency is still a greater problem in this architecture. Selection of the IF is also very important as it plays a crucial role in terms of achievable suppression of the image signal. This architecture is also not quite well suited for SDR applications. If we can solve the existing issues in the direct conversion receiver architecture and make the ancillary circuitry broadband, this architecture is close to the ideal requirements of an SDR receiver system.

### 1.4 Six-Port Based Receiver System

In the previous section, we have briefly described the existing fundamental receiver architectures for modern communication systems. There are numerous improvements on these basic architectures to enhance the overall system performance, e.g. Weaver and Hartley architectures for improving the image rejection of the super-heterodyne receivers, dual digital quadrature down conversion in the low-IF architecture receivers for higher image rejection. Superheterodyne and low-IF architectures are not quite well suited for SDR applications as they require tedious frequency planning, put restrictions on the uses of frequency bands, require bulky off-chip high-Q filter components, take more physical space, introduce nonlinear distortions because of the use of nonlinear mixers, consume more power, and are relatively architecturally complex and costly. If we could remove the DC-offset problem, I/Q mismatch and nonlinear distortions in the homodyne receiver architecture, this architecture would prove to be more suitable for SDR applications. I/Q mismatch and nonlinear distortions can be calibrated and accounted for in the homodyne architecture but DC-offset is an issue, which must be precisely resolved especially when the signals involved in the communication have very high peak-toaverage power ratio (PAPR).

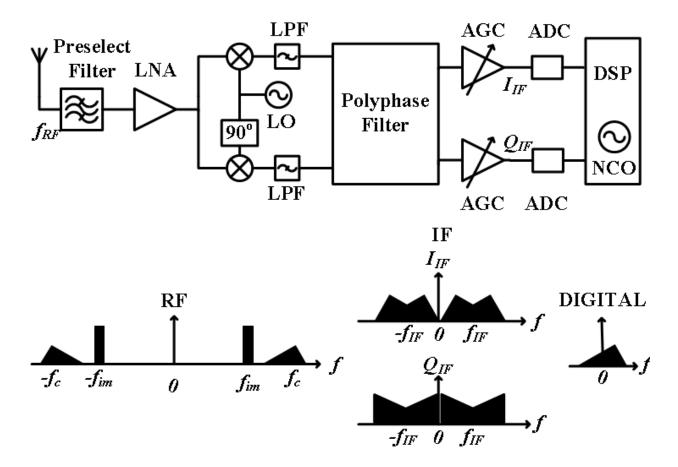

An alternative direct conversion receiver architecture based on six-port technology has been proposed in [8]-[9]. Six-port technique has been used successfully in a variety of applications such as; in microwave metrology as a reflectometer and as a low cost vector network analyzer (VNA), in other applications such as; device characterization, material characterization, load-pull and source-pull measurements, time domain voltage and current measurement systems, phased array system, antenna measurement systems, and radar systems [11]. In the six-port based architecture of homodyne receiver, the DC-offset, I/O mismatch and other sources of error can

Figure 1.7: Block diagram of a generic six-port based receiver.

be precisely calibrated and accounted for as shown in this thesis. The six-port based homodyne receiver doesn't require nonlinear mixers and hence removes the nonlinearity errors in the RF chain of the receiver system. The block diagram of a typical six-port based receiver system is shown in Figure 1.7. At the core of a six-port based receiver (SPR) system, there resides a passive, linear, six-port circuit, which can be designed to cover a very large bandwidth, which is an ideal requirement for the SDR systems. The six-port junction circuitry is also known as wave-correlator or wave-interferer. The received communication signal from the antenna is fed to one of the ports of the six-port junction. Another port is supplied with a phase stable local oscillator (LO) signal. The remaining four ports of the six-port junction are terminated with microwave power detectors. The output voltages from the four power detectors are sampled and digitized, and sent to a digital signal processor (DSP) for further processing. The DSP block processes the digitized information and finds an estimate of the originally transmitted symbol. The beauty of

the SPR is in its capability to decode a complex (vector) signal ( $a_{RF}$ ) by measuring four scalar signals (output voltages from the four power detectors). The construction of a vector signal from four scalar voltages measurements requires a calibration algorithm running on the DSP platform of the SPR system.

### 1.4.1 Theory of a Six-Port Based Receiver

In Equation (1.2) the signal represented in the form  $a_{RF}(t) = Re\{a_{RF}(t)e^{j2\pi f_c t}\}$ , where  $\widetilde{a_{RF}(t)} = I_{RF}(t) + jQ_{RF}(t)$ , is a generic representation of a passband or bandpass signal centred at a carrier signal of frequency  $f_c$ . Here  $\widetilde{a_{RF}(t)} = I_{RF}(t) + jQ_{RF}(t)$  is the phasor representation of the signal  $a_{RF}(t)$  in the Cartesian coordinate system. In the polar coordinate system, the same phasor  $\widetilde{a_{RF}(t)}$  can be represented as

$$\widetilde{a_{RF}(t)} = r(t)e^{j\varphi(t)}$$

; where  $r(t) = \sqrt{\{I_{RF}(t)\}^2 + \{Q_{RF}(t)\}^2}$ , and

$$\varphi(t) = \tan^{-1}\{Q_{RF}(t)/I_{RF}(t)\}$$

(1.3)

Here r(t) is the magnitude and  $\varphi(t)$  is the phase of the phasor  $\widetilde{a_{RF}(t)}$ . Any bandpass signal can be represented in terms of its phasor if we know the frequency of the carrier signal.

If  $a_{RF} = I_{RF} + jQ_{RF} = A_{RF}e^{j\varphi_{RF}}$ ;  $A_{RF} = \sqrt{I_{RF}^2 + Q_{RF}^2}$ ,  $\varphi(t) = \tan^{-1}(Q_{RF}/I_{RF})$ , is the phasor representation of the original bandpass transmitted signal then the real transmitted passband signal at the receiver antenna path reference plane (PORT-2) can be written as

$$s_{RF} = Re\{a_{RF}e^{j2\pi f_c t}\} = I_{RF}\cos(2\pi f_c t) - Q_{RF}\sin(2\pi f_c t)$$

(1.4)

Similarly the phasor for local oscillator (LO) signal at a reference plane in LO port (PORT-1) can be written as  $a_{LO} = A_{LO}e^{j\varphi_{LO}}$ , where  $A_{LO}$  and  $\varphi_{LO}$  are the magnitude and the phase of the LO signal phasor, respectively. An important point to be noted here is that the magnitude and the phase of the RF signal phasor are time dependent and varying while those of the LO signal

phasor are constant and fixed. The phase noise in the LO signal will cause error in the phase of the LO signal phasor.

If  $S_{ij}$ ; i, j = 1, 2, ..., 6 are the S-parameters of the six-port junction, then the phasors of the signals at PORT – 3, 4, ..., 6 can be written as

$$a_k = S_{k2}a_{RF} + S_{k1}a_{L0}; k = 3,4,...,6$$

(1.5)

The signal powers reaching to the four power detectors can be written as in equation (1.6).

$$P_k = |S_{k2} \mathbf{a}_{RF} + S_{k1} \mathbf{a}_{LO}|^2; k = 3,4,...,6$$

(1.6)

Here  $P_k$  is the power detected by the  $k^{th}$  power detector. Equation (1.6) can be simplified further and solved for  $a_{RF}$  in primarily two different ways, resulting in two different modeling and calibration approaches; namely the linear and the nonlinear modeling and calibration approaches for the six-port based receiver systems. Each way of modeling and calibration comprises of certain model parameters which must be determined before making an estimate of the received signal  $a_{RF}$ . In chapter three of this thesis the nonlinear modeling and calibration approach for an SPR system is described in detail. The linear modeling and calibration approach for the SPR system is dealt with in detail in chapter four.

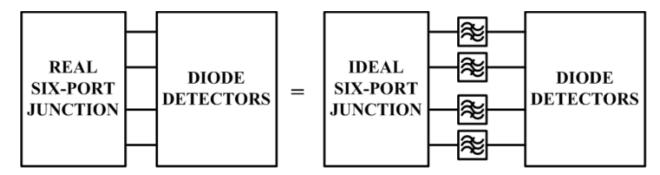

### 1.5 Limitations of the Six-Port Based Receiver Systems

The core of a six-port based receiver system consists of a passive six-port junction and four power detectors. In most cases, the six-port junction circuit comprises of the quadrature hybrids and power dividers. The performance of these microwave components are best guaranteed at the design frequency but it deviates from the ideal performance when the frequency of operation is changed. The deviation in the performance of a six-port junction from its ideal behavior results in degraded performance of the whole receiver system. The diode based power detectors are used most frequently in the SPR systems because of their low power requirements and smaller sizes.

These power detectors generate voltages in response to the microwave power at their input ports. The input power range, in which the voltage generated by a power detector is proportional to its input power, is called the linear range of the power detector. The diode based power detectors are notorious for their limited linear dynamic range. When these detectors are used in a SPR system, they limit the dynamic range of the whole receiver system. The diode detectors characteristics are linearized to open up this limitation on the dynamic range. Another problem with the diode detectors is their different dynamic behaviour as compared to static behaviour. The input power-output voltage characteristic of a diode power detector is dependent on the frequency of the input excitation signal. All these issues in a typical SPR system results in heavily degraded receiver performance when real wideband modulated signals are used in the communication. An accurate modeling of the six-port junction and linearization of the power detectors is required to solve the limitations/problems of the SPR system including the dynamic range limitations of the power detectors and the trade-off between dynamic range and linearity of the power detectors for good quality reception.

### 1.6 Building Blocks of an SPR System

The basic components required for integrating an SPR system for SDR applications are:

- 1) Wideband Antenna

- 2) Broadband Low noise amplifier (LNA)

- 3) Broadband Automatic gain controller (AGC)

- 4) Broadband Six-port junction

- 5) High dynamic range wideband diode power detectors

- 6) Analog-to-digital converters (ADC)

- 7) Digital signal processor (DSP)

The antenna, LNA, AGC, and the six-port junction circuitry should be broadband that cover the whole frequency band over which the SDR system is expected to operate. ADCs should be fast enough to sample a signal having the highest possible frequency bandwidth expected from the SDR system. DSP should be operating at a speed fast enough to process the sampled data and run the SPR calibration algorithm. Diode power detectors should have high dynamic range to cover the dynamic range requirement of the SDR receiver system. Detectors should be broadband and also fast enough to accommodate the detection of signal with the highest possible bandwidth.

### 1.7 Thesis Outline

The outline of this thesis is as follows. The first chapter of this thesis discusses the usefulness and limitations of the modern receiver architectures for software defined radio (SDR) applications. A linear homodyne receiver architecture based on the six-port technique is introduced in this chapter and its suitability for SDR applications is discussed in detail. This chapter also highlights the limitations of the existing six-port based receiver (SPR) systems and the contributions of this thesis. Characteristics of the diode power detectors used in a typical SPR system are studied in chapter two. A survey of existing detector linearization is provided in this chapter and a new linearization technique, suitable for linear calibration of the SPR systems, is proposed. The nonlinear and the linear modeling and calibration techniques for the SPR systems are discussed in detail in chapter three and chapter four, respectively. Chapter five concludes the thesis and gives pointers to the future research works.

### 1.8 Thesis Contributions

The fundamental contributions of the works, carried out for this thesis, to the RF and the microwave community can be summarized in the following three points:

- 1) A nonlinear calibration approach based on the use of training sequence inserted at the beginning of an actual test data burst is proposed in chapter three of this thesis. The proposed nonlinear calibration approach avoids the frequent connection/disconnection of the standard loads at the RF port of the six-port junction as was the practice in six-port based microwave metrology applications. The proposed calibration algorithm is useful for six-port based receiver applications where removal of the antenna for connection/disconnection of the standard loads for calibration purpose is not feasible and practical.

- 2) After a survey of the existing linearization techniques for the diode power detectors, it was found out that the existing linearization techniques for the diode detectors are based on a continuous wave (CW) measurement that ignores the dynamic effects of the time varying real communication signals. A new diode power detector linearization technique suitable for wideband signals having high peak-to-average power ratios (PAPR) is proposed in chapter two of this thesis. The new proposed detector linearizer takes into account the nonlinearity and the memory effect displayed by the real diode power detectors.

- 3) In chapter four of this thesis, an integrated calibration approach for the whole SPR system is proposed, that combines the existing two steps process of diode detector linearization and six-port junction calibration. The proposed SPR system calibration approach is a single step approach that takes into account all the identified system imperfections in a real SPR system, such as; the non-flat frequency responses (S-parameters magnitude response) of six-port junction and components, deviation of phase responses from the ideal behaviour (S-parameters phase response), and nonlinearity and

memory effect displayed by the diode power detectors. All these identified system and component imperfections become part of the SPR model developed in chapter four of this thesis and are taken care of during the proposed calibration procedure.

The work carried out for this thesis resulted in the following peer-reviewed publications:

- 1. A. Hasan and M. Helaoui, "Non-Linear Auto-Calibration Method for Six-Port Based Direct Conversion Receivers," *IET Microwaves, Antennas and Propagation* (under preparation).

- 2. A. Hasan and M. Helaoui, "Novel Modeling and Calibration Approach for Multi-Port Receivers Mitigating System Imperfections and Hardware Impairments," *IEEE Transaction on Microwave Theory and Techniques*, vol. 60, no. 8, pp. 2644-2653, Aug. 2012.

- 3. A. Hasan, M. Helaoui and F. M. Ghannouchi, "Dynamic Linearization of Diodes for High Speed and Peak Power Detection Applications," in 2012 IEEE MTT-S International Microwave Symposium Digest (IMS'2012), Montreal, QUE, Canada, pp. 1-3, Jun. 2012.

### 1.9 Conclusions

The importance of multi (six)-port based receiver architecture for software defined radio (SDR) applications is highlighted in this chapter. Architectural comparison of the six-port based receiver system with the modern receiver architectures is provided to illustrate the advantages and drawbacks of different receiver architectures. The six-port based receiver architecture is a homodyne type receiver architecture which has some practical problems, such as; DC-offset, I/Q mismatch, I/Q cross-talk, and nonlinear distortions. Because of these inherent problems in the homodyne receivers, this architecture has not been used successfully in any commercial products using non-constant envelope modulation scheme signals. For constant envelope modulation scheme signals, the signal statistics are used to minimize the effect of some of the problems of this architecture. These sources of errors can be precisely modeled and calibrated in a six-port

based receiver system as proposed in this thesis. The proposed model and the calibration approach for six-port based homodyne receiver shows its usefulness for the non-constant envelope modulation scheme signals too. The outline and the contributions of the thesis are highlighted in this chapter.

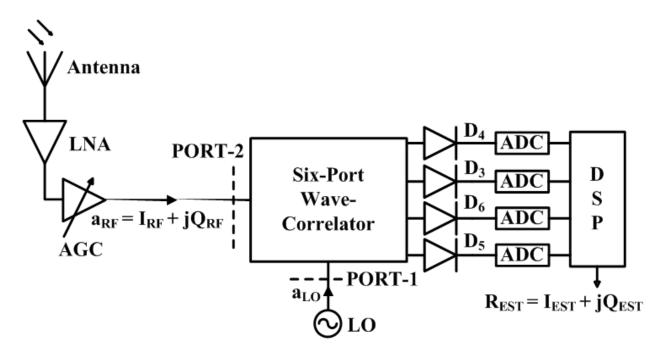

### Chapter Two: Diode Detector Modeling and Linearization

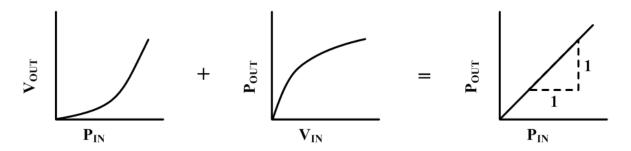

Historically bolometer, thermistor, diode, and transistor based power detectors have been used in a variety of microwave power measurement applications, such as: multi-port based measurement systems, radar applications, and power measurement and control applications in modern cellular communication systems. Diode based power detectors are widely used nowadays because of their low power and simplified support circuitry requirement. The dynamic range of the diode power detectors, where the output voltage from the detector is proportional to the input microwave power, is quite limited [11]. This limits the useful range of operations of the diode power detectors for many applications. For example, when the diode power detectors are used in a six-port based receiver system, the dynamic ranges of the diode power detectors limit the dynamic range of the whole receiver system. To extend this dynamic range, the power detector can be operated close to its saturation region, where it exhibits nonlinear characteristic. Linearization of the diode power detectors characteristics is performed to open up this limitation and to extend their dynamic range without affecting the received signal quality. The output voltage of the diode power detector is used to predict its characteristic and compensate for its nonlinear behaviour. The concept of linearization for the diode power detectors is shown in Figure 2.1. The detector output voltage is input to the linearizer block that outputs the linearized power. Ideally, the linearized power should be equal to the actual input microwave power to the diode power detector. To linearize the characteristics and extend the dynamic ranges of the real diode power detectors, a number of linearization techniques have been proposed in open literature [16]-[19]. All the existing linearization techniques for the diode power detectors use a continuous wave (CW) excitation signal for detector modeling and characterization. In this chapter we show that the characteristic of a diode based power detector is not static. It is dependent

Detector Output Voltage,  $V_{OUT}$  Linearizer Input Voltage,  $V_{IN} = V_{OUT}$

Figure 2.1: Block diagram of a diode based power detector cascaded with its linearizer.

on the type of input excitation signal. This power-voltage characteristic of a diode detector deviates from its usual CW characteristic, when real wideband modulated signals are used to characterize and linearize the diode power detector.

### 2.1 CW Linearization Techniques

Four different techniques found in open literature to linearize the diode power detectors characteristics are briefly described in the following subsections.

### 2.1.1 Look-up-table (LUT) Based Linearization Technique [16]

This technique is a crude and direct measurement based method to linearize the diode detector characteristic. In this technique a look-up-table consisting of detector output voltage against the input microwave power at the carrier frequency is constructed and stored. A simple interpolation (e.g. interp1 function of MATLAB) is applied on the detector output voltage  $V_{OUT}$  to linearize the detector characteristic and to obtain the linearized power  $P_{OUT}$ .

### 2.1.2 'Hoer-Roe-Allred (HRA)' Model [17]

In this model the relationship governing the linearized power and the detector output voltage is given by equation (2.1).

$$P_{OUT} = Kv^{(1+b_1v+b_2v^2+b_3v^3+\cdots+b_Nv^N)}$$

(2.1)

Here  $v = q(V_{IN} - V_O)$ , where  $V_O$  is the diode power detector output voltage when  $P_{IN} = 0$ , and q is a scale factor. The linearizer parameters K, q, and  $b_i$  are obtained during the detector characterization step. These parameters are stored in the linearizer block and are used to linearize the detector characteristic according to equation (2.1).

### 2.1.3 'Zhaowu-Binchun (ZB)' Model [18]

When the output voltage is reduced to zero for zero-bias Schottky diodes, the deviation from the square law according to the model in equation (2.1) tends to infinity. To solve this problem, a new model to linearize the Schottky diode detectors was proposed in [18]. The linearized power according to this model is given by equation (2.2).

$$P_{OUT} = KV_{IN} \times 10^{(a_1x + a_2x^2 + a_3x^3 + \dots + a_Nx^N)}$$

(2.2)

Here x is a function of  $V_{IN}$ , defined as  $x = \ln(V_{IN}/q + 1)$ ; where q is a scalar factor chosen so that x is positive and has a maximum value of 0.5.

### 2.1.4 'Polynomial (P)' Model [19]

The linearizer characteristic in this model is approximated by a polynomial of the form given in equation (2.3).

$$P_{OUT} = c_0 + c_1 V_{IN} + c_2 V_{IN}^2 + c_3 V_{IN}^3 + \dots + c_N V_{IN}^N$$

(2.3)

All the four models described here are static and do not consider any dynamic behaviour of the diode power detectors or in other words the frequency response or the memory effect of the diode power detectors. When the input excitation signal has a wide bandwidth, the frequency

response and hence the memory effect of the diode power detectors comes into picture. Any linearization technique which ignores this effect will cause error in the linearized output power. The three latter models (HRA, ZB, and P models) fit the model equations' parameters to the measured data and therefore may include fitting residual errors. The look-up-table is therefore more accurate and will be used in the following analyses.

### 2.2 Diode Detectors for Peak Power Detection Applications

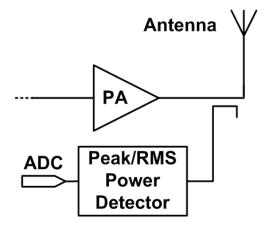

In power control applications, the diode power detectors are used in a variety of applications such as; peak power detection, root-mean-square (rms) power detection, and envelope detection. In power control applications of the cellular mobile communication, diode based power detectors are used for measuring the transmitted power levels. Peak power detector is a good choice for RF power detection application for the communication standards employing constant envelope modulation scheme such as the GMSK (Gaussian Minimum Shift Keying) for GSM. However, for communication systems with high crest factors or PAPR like UMTS, the rms power detection is used. The use of diode power detector in cellular handsets power control application is shown in Figure 2.2.

Figure 2.2: Diode based peak/rms power detector in cellular handset power control application.

In six-port based receiver applications, the diode power detectors are used as envelop power detectors. Linearization of diode power detectors for envelop power detection application will be discussed in Section 2.3. Here we describe a linearization technique for diode power detectors for peak power detection applications. When the usual CW linearization techniques are used for peak power detection applications, the linearized peak powers result in error as compared to the actual input peak powers. This deviation is much pronounced when the input excitation signal has a very high value of peak-to-average-power-ratio (PAPR). A test bench is setup to measure the peak power detector characteristic for different excitation signals. A linearizer based on CW measurement and characterization data is designed to linearize the diode based peak power detector characteristic as explained in Section 2.1.

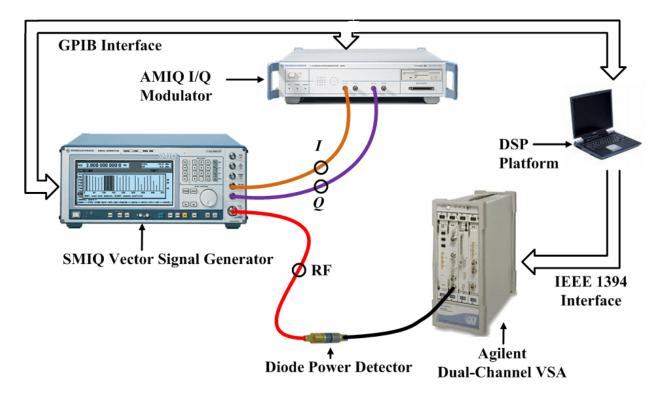

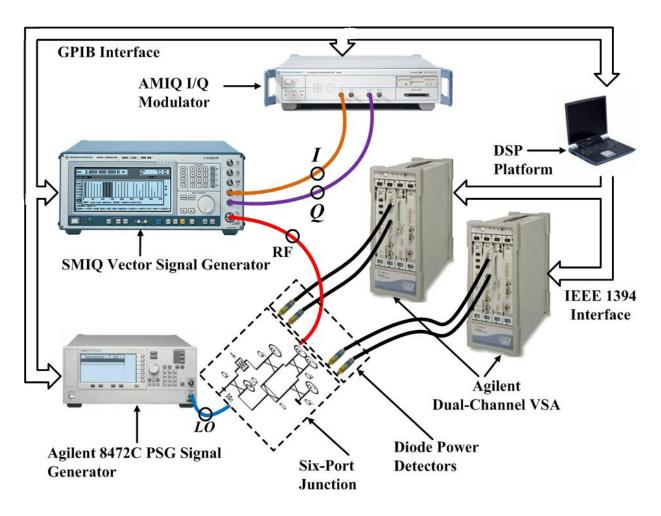

### 2.2.1 Measurement Test Setup

The test setup to characterize and linearize a diode based peak power detector is shown in Figure 2.3. The baseband quadrature amplitude modulation (QAM) modulated symbols are generated on a desktop PC in MATLAB. The baseband symbols are passed through a raised-cosine filter with a roll-off factor 0.3 (up-sampled by 8) and a delay of 3 taps. These pulse shaped symbols are further passed to an I/Q modulation generator (AMIQ from Rhode & Schwarz GmbH & Co.) to generate an I/Q modulated signal. This pulse shaped and I/Q modulated signal is frequency up-converted to a desired carrier frequency (2.5GHz) using a SMIQ03B vector signal generator from Rhode & Schwarz. The power level for the input excitation is set in the SMIQ and this passband signal is then fed to the diode power detector (8472B from Agilent Technologies, Inc.). Voltage generated by the Schottky detector in response to a particular excitation signal is captured using a synchronized dual-channel VSA (89600 series VSA from Agilent Technologies). The captured voltage waveform is used to linearize the diode detector

Figure 2.3: Test setup for the peak power detector characterization and linearization.

characteristic as discussed in the next subsection.

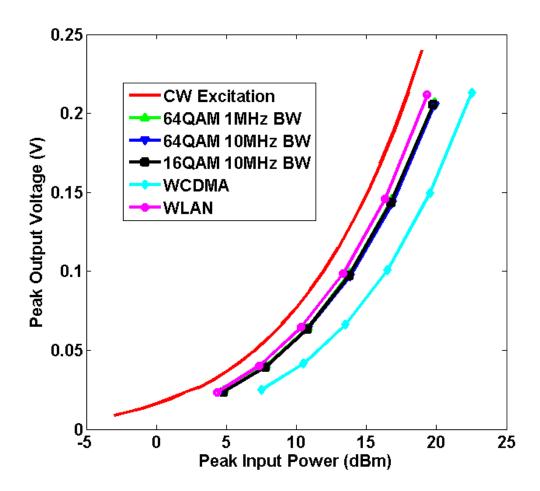

#### 2.2.2 Measurement Results

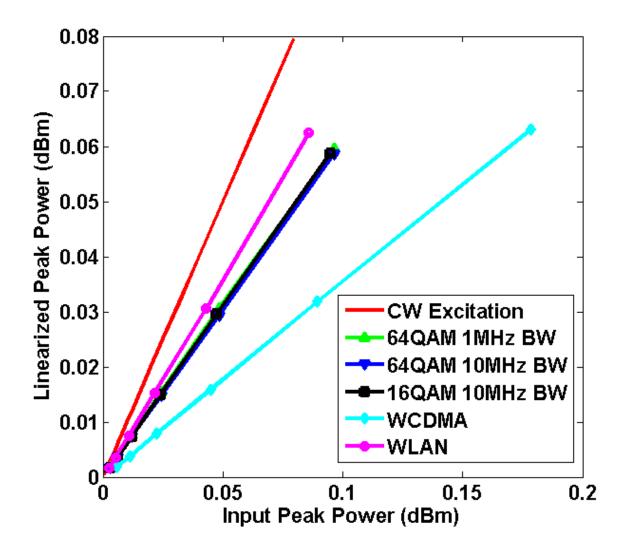

The actual input peak power and the corresponding output peak voltage characteristics for the diode power detector in response to different excitation signals are shown in Figure 2.4. From the plots in Figure 2.4, it is obvious that the peak power detector behaves differently for different input excitation signals. The deviation from the CW response is much more pronounced as the PAPR of the excitation signal increases. Peak power detector characteristic for the Wideband Code Division Multiple Access (WCDMA) signal having the highest PAPR value ( $\approx 9.5 \, \mathrm{dB}$ ) has the highest deviation from the CW characteristic. Deviation of the peak power detector characteristics for QAM modulated signals (PAPR  $\approx 6.8 \, \mathrm{dB}$ ) is intermediate of the WCDMA (PAPR  $\approx 9.5 \, \mathrm{dB}$ ) waveform excitation and the Wireless Local Area Network (WLAN) excitation

Figure 2.4: Peak power detector characteristics for different excitation waveforms at a carrier frequency of 2.5GHz.

(PAPR  $\approx$  6.3dB) as shown in Figure 2.4. The carrier frequency for all the excitation waveforms is kept same at 2.5GHz.

In order to show the error in the CW linearized output peak power for the peak power detector, we pass the output voltage waveforms from the diode detector to a CW linearizer. The linearized peak power for different test excitation signals is plotted against the actual input peak power of the excitation signal in Figure 2.5.

Figure 2.5: Linearized peak power versus the actual input peak powers for different types of excitation signals.

The ideal slope for such plots should be equal to unity, if the linearizer block is linearizing perfectly as expected from the theoretical analysis. In practice, the linearizer providing the slope closest to the unity offers the best performance. According to the plots as shown in Figure 2.5, we observe that the signal having the highest PAPR (WCDMA) deviates the maximum from the unity slope of the linearized peak power versus the actual input peak power line plot. The slope of the CW excitation when linearized with the CW characterization data is unity. Slopes for all

other excitation signals are constant for each of the signals but are other than unity. Based on these observations, it is concluded that the behaviour of the power detector changes depending on the type of excitation. Therefore, dynamic characterization and linearization are required for accurate peak power detection. Two different linearization techniques are proposed in [20] to linearize the diode peak power detector characteristic for excitation signals other than the CW.

- 1) The diode based peak power detector must be linearized for the specific excitation signal type using the similar approach as is done in case of a CW excitation signal. The peak input powers and peak output voltages are recorded for a particular excitation signal and a linearizer of the form discussed in Section 2.1 is obtained. All the future linearization for the peak power detector will be done according to these stored linearizer parameters using the output voltage from the peak power detector for the specific excitation signal.

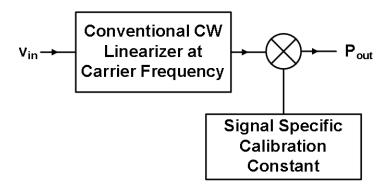

- 2) We observed from the plots in Figure 2.5, that, even though the slope of the CW linearized peak power versus the actual input peak power plot is not unity, it is constant for a specific excitation type. This slope for a specific excitation signal type can be stored along with the CW linearizer parameters. The detector output voltage will be passed to a CW linearizer and the corresponding output peak linearized power will be multiplied further by a constant factor accounting for the difference between the CW slope and the slope for that specific excitation. This second linearization technique for peak power detector is more efficient in terms of memory as it requires only one parameter corresponding to the excitation signal type apart from the fixed CW linearization parameters (usually 6). For the approach described in 1), individual linearization parameters (usually 6 for each) are stored for each excitation signal type. Figure 2.6 shows the block diagram of the proposed peak power linearizer 2) using the signal specific calibration constant.

Figure 2.6: Proposed peak power linearizer using calibration constant.

Table 2.1 summarizes the actual linearization errors in terms of normalized mean square error (NMSE), as defined in equation (2.5), when a CW linearizer and the proposed linearizer 2) is used to linearize the peak power detector for different excitation signals.

Table 2.1: Comparison of CW and proposed peak power detector linearizer

| Excitation Waveform | PAPR (dB) | NMSE (dB)     |                       |

|---------------------|-----------|---------------|-----------------------|

|                     |           | CW Linearizer | Proposed Linearizer 2 |

| WLAN                | 6.3       | -7.98         | -32.94                |

| 64QAM 1MHz BW       | 6.8       | -5.29         | -35.61                |

| 64QAM 10MHz BW      | 6.8       | -5.29         | -44.29                |

| 16QAM 10MHz BW      | 6.8       | -5.30         | -41.61                |

| WCDMA               | 9.5       | -0.65         | -41.95                |

# 2.3 Diode Detector Linearizer for Wideband Signals

In the previous section we showed that the characteristic of the diode power detector was dependent on the input excitation signal type. The diode power detectors used in multi-port based receiver systems are expected to accurately detect the instantaneous envelope power of the continuous time microwave signals at the input port of the detector. Errors in the linearized

detected powers for the power detectors have a direct bearing on the performance of the multiport based receiver system. Figure 2.7 shows the input power waveform and the linearized power

Figure 2.7: Input envelope power waveform and the linearized envelope power waveforms using CW linearizers for a diode power detector.

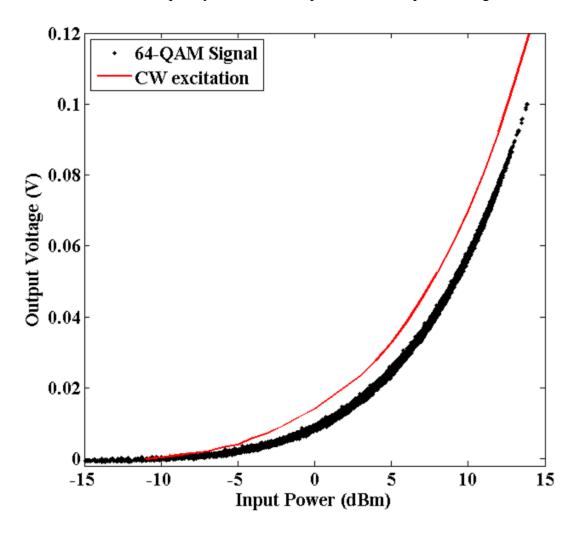

waveforms for a diode power detector using CW linearizers for a 64QAM modulated signal having 1MHz bandwidth. The CW linearizer corrects for the nonlinearity of the diode power detector but fails to account for the frequency response of the detector. To highlight the frequency response of the diode power detectors, the measured characteristic of a diode power

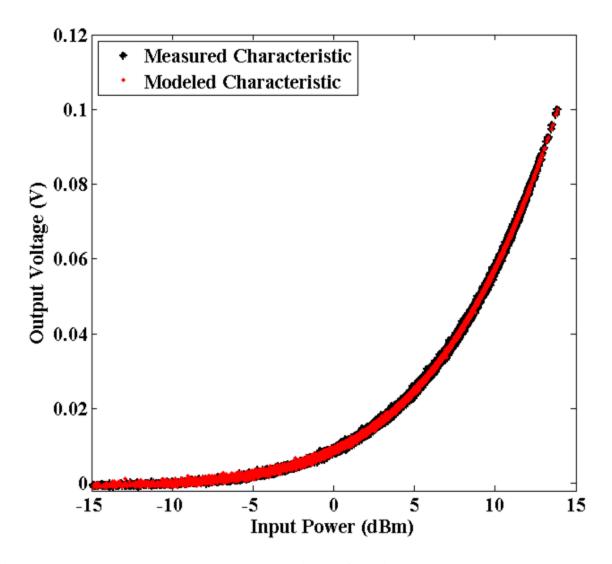

detector when excited by a 64QAM modulated signal having 1MHz bandwidth and that with a CW excitation at a carrier frequency of 2.5GHz are plotted and compared in Figure 2.8.

Figure 2.8: Behaviour of a diode power detector excited by a 64QAM modulated signal having 1MHz bandwidth and by a CW excitation at a carrier frequency of 2.5GHz.

In order to increase the dynamic range of the whole six-port based receiver system, the diode power detectors must be operated beyond their square law regions. It is obvious from Figure 2.8 that even in their square law regions, the linear relationship of output voltage and input power is not valid when the detector is excited by a modulated wireless signal. It shows that the nonlinearity and the memory effect displayed by the diode detectors must be modeled and

calibrated to reduce the error in the detections of the received symbols and to increase the dynamic range of the receiver system. CW linearizer models described in Section 2.1 fail to capture both the dynamic behaviour and the memory effect displayed by the diode detector under a wideband modulated wireless signal operation. A new method to model and linearize the diode power detectors is proposed in this section.

## 2.3.1 Diode Detector Linearizer for Modulated Signals

Memory polynomial [21] has been used effectively to linearize the power amplifier (PA) and transmitter characteristics. The diode power detector characteristic in this thesis is linearized using a modified memory polynomial [22]. The output voltage  $v_k$  corresponding to the input microwave power  $P_{in,k}$  for the diode detector  $D_k$  is used to linearize its characteristic. The relationship between the linearized output power,  $P_{out,k}$  from the proposed linearizer and the output voltage from the diode detector,  $v_k[n]$  at any instant of time is modeled by equation (2.4). We call this diode detector linearizer model as memory polynomial (MP) model.

$$P_{out,k}[n] = \sum_{q=0}^{M_k} \sum_{p=1}^{N_k} c_{pqk} v_k^p [n-q]$$

(2.4)

Here  $c_{pqk}$  are the coefficients of the above memory polynomial, and  $N_k$  and  $M_k$  are the non-linearity order and the memory depth for the diode detector  $D_k$ , respectively, where k = 3,4,...,6 is the number of the diode detector.

The metric normalized mean square error (NMSE) between the actual input power  $P_{in,k}$  and the linearized output power  $P_{out,k}$  is used to assess the performance of the proposed linearizer. NMSE calculated over N samples of the actual input power and the linearized output power is defined as in equation (2.5).

$$NMSE = 10 \log_{10} \left( \frac{\sum_{n=1}^{N} \left| P_{out,k}[n] - P_{in,k}[n] \right|^2}{\sum_{n=1}^{N} \left| P_{in,k}[n] \right|^2} \right)$$

(2.5)

The same test setup as described in subsection 2.2.1 is used to evaluate the performance of the proposed linearizer. First 100 symbols from the 2500 randomly generated test symbols are used as a training sequence to extract the model coefficients for the diode detector linearizer. Equation (2.4) is written in a matrix form as in equation (2.6).

$$P_{out,k}[n] = \mathbf{V}^{T}[n]\mathbf{C} \tag{2.6}$$

where

$$C^T = [c_{10k} \cdots c_{N_k0k} \ c_{11k} \cdots c_{N_k1k} \cdots c_{1M_kk} \cdots c_{N_kM_kk}]$$

and  $V^T[n] = [v_k[n] \cdots v_k^{N_k}[n] \ v_k[n-1] \cdots v_k^{N_k}[n-1] \cdots v_k[n-M_k] \cdots v_k^{N_k}[n-M_k]]$

Solution to the equation (2.6) can be obtained from the normal equation given in equation (2.7) using the method of least squares [23].

$$\Phi \mathbf{C} = \mathbf{z} \tag{2.7}$$

where  $\Phi$  is the correlation matrix of the input data V[n], and z is the cross-correlation vector between the inputs V[n] and some desired response d[n].

The correlation matrix  $\Phi$  can be written in terms of a data matrix A, whose Hermitian transpose is defined by  $A^H = [V[M] \quad V[M+1]$

$$= \begin{bmatrix} V(M) & V(M+1) & \cdots & V(N) \\ V(M-1) & V(M) & \cdots & V(N-1) \\ \vdots & \vdots & \vdots & \vdots \\ V(1) & V(2) & \cdots & V(N-M+1) \end{bmatrix}$$

(2.8)

Here M is related to the size of the coefficient matrix C and N is related to the size of the input data. Using the definition in equation (2.8), the correlation matrix  $\Phi$  can be written in a compact from as in equation (2.9).

$$\Phi = \mathbf{A}^H \mathbf{A} \tag{2.9}$$

Similarly, if we introduce a desired data vector  $\mathbf{d}$ , consisting of the desired response d(i), depending on the input power  $P_{in,k}[i]$  for the values of i in the interval [M,N] then

$$\mathbf{d}^{H} = [d(M) \quad d(M+1) \quad \cdots \quad d(N)] \tag{2.10}$$

and the cross-correlation vector  $\mathbf{z}$  can be written as in equation (2.11).

$$\mathbf{z} = \mathbf{A}^H \mathbf{d} \tag{2.11}$$

Equation (2.7) can be rewritten to get the coefficient vector  $\boldsymbol{c}$  directly in terms of data matrices.

$$\mathbf{C} = (\mathbf{A}^H \mathbf{A})^{-1} \mathbf{A}^H \mathbf{d} \tag{2.12}$$

Here A is the data matrix representing the time evolution of the input vectors V[n], and d is the desired data vector representing the time evolution of the desired response.

If we define a matrix

$$A^{+} = (A^{H}A)^{-1}A^{H} \tag{2.13}$$

then we may rewrite the equation (2.12) simply as

$$\mathbf{C} = \mathbf{A}^{+} \mathbf{d} \tag{2.14}$$

The matrix  $A^+$  is called the pseudoinverse or the Moore-Penrose generalized inverse of the matrix A [23]. Using equation (2.14), the coefficient matrix C for the diode detector linearizer can be obtained, given the input data matrix A and the desired response vector C.

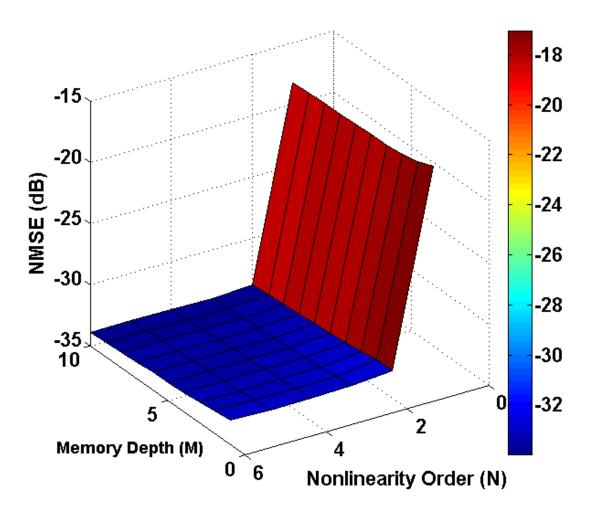

In order to determine the optimal model coefficients, the memory depth  $M_k$  and the non-linearity order  $N_k$  are varied and the corresponding NMSEs are recorded. The  $(M_k, N_k)$  pair having the least acceptable NMSE is fixed for the diode detector  $D_k$ . The corresponding linearizer model coefficients vector  $\mathbf{C}$  for the particular test waveform is used to linearize the power detector using equation (2.6). The NMSE performance a typical Shottky diode detector is shown in

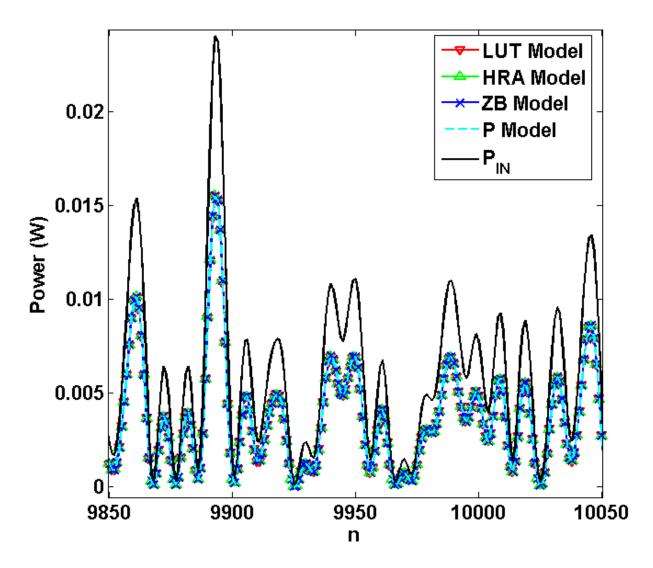

Figure 2.9. The measured and the modeled behavior of a diode power detector using the modeling approach developed here are shown in the Figure 2.10.

Figure 2.9: NMSE performance of a memory polynomial based linearizer for Shottky diode power detector.

Table 2.2 summarizes the performance of the proposed linearizer model for the detector in terms of NMSE.

Table 2.2: Performance summary of the proposed model of the power detector linearizer

| Signal Type   | $N_k$ | $M_k$ | Normalized Mean Square Error (NMSE) |

|---------------|-------|-------|-------------------------------------|

| 64QAM 1MHz BW | 4     | 9     | -36.8 dB                            |

Figure 2.10: Measured and modeled behaviour of a diode power detector excited by a 64QAM modulated signal having 1MHz bandwidth at a carrier frequency of 2.5GHz.

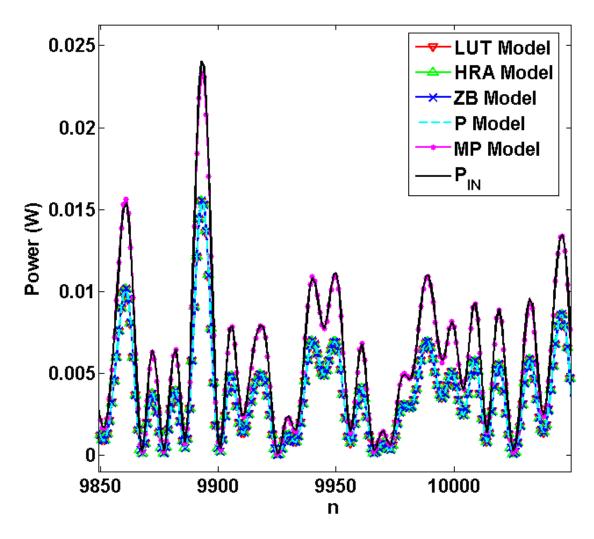

Figure 2.11 shows the comparison of the linearized output envelope power waveforms with the actual input envelope power waveform from the different diode detector linearizer studied in this chapter. All the CW detector linearizers have similar performance but the proposed memory polynomial based detector linearizer model (MP model) outperforms all of the CW linearizers as expected. In chapter four of this thesis, we use this proposed diode detector linearizer model for accurate modeling and calibration of a six-port based receiver system.

Figure 2.11: Actual input power waveform and the linearized output power waveforms for a 64QAM modulated signal having 1MHz bandwidth at a carrier frequency of 2.5GHz.

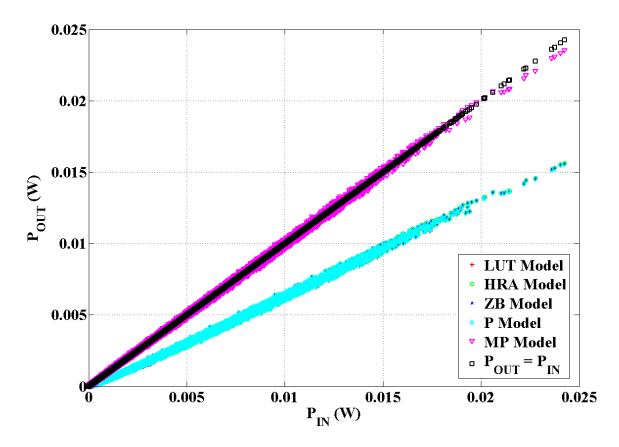

The ideal slope of the linearized output power versus actual input power plots should be unity. Figure 2.12 shows the comparison of the proposed linearizer performance with the existing CW linearizers. The CW linearizers deviate from the usual unity slope characteristic while the proposed memory polynomial based linearizer attempts to account for the nonlinearity and the memory effect of the diode detector and follows the ideal unit slope characteristic.

Figure 2.12: Plots of linearized output envelope powers versus actual input envelope power for different diode detector linearizers.

## 2.4 Conclusion

In this chapter we saw that the behaviour of the diode power detector is different for different excitation signals. This behaviour is remarkably altered from the continuous wave (CW) characteristic of the diode power detector. The CW linearizers based on CW characterization of the diode power detectors result in error when the voltages generated in response to the real modulated signals are given as input to the CW linearizers for linearization. Based on the observations in this chapter, we have proposed a peak power detector linearizer for peak power detection applications. We also proposed a new memory polynomial based linearizer for the diode power detectors that corrects for the nonlinearity and the memory effect displayed by the

detectors. The memory polynomial based linearizer is a wideband signal detector linearizer which accounts for the frequency response of the diode power detectors. The linearizer model for the diode power detector developed in this chapter will be used in modeling the six-port based receiver system. It will be shown in chapter four of this thesis that the memory polynomial based detector linearizer improves the performance of the overall six-port based receiver system employing diode power detectors.

## Chapter Three: Nonlinear Modeling and Calibration of Six-Port Receiver

We mentioned briefly in chapter one that the modeling and calibration approaches for a six-port based receiver (SPR) system can be broadly categorized into two approaches; namely the linear and the nonlinear modeling and calibration approaches. In this chapter we describe and propose a nonlinear modeling and calibration approach for the SPR systems. We know from equation (1.6) that the microwave power detected by the  $k^{th}$  diode power detector in an SPR system is given by

$$P_k = |S_{k2} \mathbf{a}_{RF} + S_{k1} \mathbf{a}_{LO}|^2; k = 3,4,...,6$$

(3.1)

If  $q_k = -\frac{S_{k1}}{S_{k2}}$ , then the equation (3.1) can be written as in equation (3.2) [11].

$$P_k = |c_k|^2 |R - q_k|^2; k = 3,4,...,6$$

(3.2)

Here  $|c_k|^2 = |S_{R2}|^2 |a_{LO}|^2$  is a real parameter depending on the S-parameters of the six-port junction and the LO power.  $R = \frac{a_{RF}}{a_{LO}}$  represents the phasor of the received RF signal with respect to the LO signal phasor. R and  $q_k$  are complex parameters depending on the RF and the LO signals, and the six-port junction S-parameters, respectively. The four equations in (3.2) represent circles in a complex R-plane whose centres and radii are given by  $q_k$  and  $r_k = \frac{\sqrt{P_k}}{|c_k|}$ , respectively. The centres of these circles are fixed for a given SPR system as they are functions of the S-parameters of the six-port junction. The set of equations in (3.2) is an over determined system of equations as the complex received signal R corresponds to the point of intersection of the four circles in the complex R-plane. Theoretically only three circles are enough to describe a point in a complex Cartesian coordinate system plane. From equation (3.2), we find that a total of 12 real parameters (four complex parameters  $q_k$  and four real parameters  $r_k$ ) are required to describe the SPR system fully. These parameters must be determined before calculating any received signal R. Number of the calibration parameters can be reduced if some forms of

transformations are used on the over determined system of equations. We next describe a twostep nonlinear modeling and calibration approach using a bilinear transformation for the SPR systems.

### 3.1 Nonlinear Modeling of SPR systems

Microwave powers measured from the detectors 4, 5, and 6 in equation (3.2) can be normalized with respect to a reference port power  $P_3$  to eliminate the influence of LO power ( $|a_{LO}|^2$ ) on the calibration procedure. This normalization process produces three normalized powers

$$p_k = \frac{P_k}{P_3} = h_k^2 \frac{|R - q_k|^2}{|R - q_3|^2}, k = 4,5,6.$$

(3.3)

Here  $h_k^2 = \frac{|S_{k2}|^2}{|S_{32}|^2}$ . Equation (3.3) represents three circles in a complex *R*-plane, the centers and radii of which are independent of the LO power, and are determined solely by the system parameters and the readings of the four power detectors. Equation (3.3) can be simplified further and made more tractable by introducing an intermediate complex signal *T* [11] such that

$$p_4 = |T|^2 (3.4a)$$

$$p_5 = \frac{1}{4^2} \left| T - |m| \right|^2 \tag{3.4b}$$

$$p_6 = \frac{1}{B^2} |T - n|^2 \tag{3.4c}$$

Here n is a complex constant, and A, B, and |m| are real constants functions only of the system parameters. Once the intermediate complex signal T is known, it can be used to get R and hence the received signal  $R' = a_{RF} = I_{RF} + jQ_{RF}$  through a bilinear transformation given in equation (3.5).

$$T = \frac{d'R + e'}{c'R + 1} = \frac{dR' + e}{cR' + 1}$$

(3.5)

Here c, d, and e are three complex constants, functions only of the system parameters and the LO

signal  $a_{LO}$ . Equations (3.3), (3.4), and (3.5) represent the nonlinear model of an SPR system. Nonlinear calibration of the SPR system involves determining the model parameters embedded in these three equations. The nonlinear model for the SPR system developed here involves 11 real constants (4 complex parameters c, d, e, and n, and 3 real parameters A, B, and |m|). We next describe the nonlinear calibration approach for an SPR system.

## 3.2 Nonlinear Calibration of SPR systems

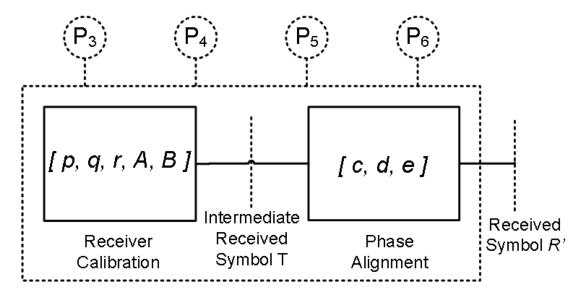

The nonlinear calibration procedure for an SPR system can be divided into two steps: the 'receiver calibration' step ( $P_k$  to T reduction) and the 'phase alignment' step (T to R' estimation) to simplify the calibration procedure.

## 3.2.1 Receiver Calibration Step ( $P_k$ to T reduction)

From equation (3.4), the intermediate complex signal T can be eliminated [24] to get equation (3.6) which is independent of both the LO power as well as the RF signal. This equation depends only on the receiver system parameters and we will call this step as 'Receiver Calibration' Step or ' $P_k$  to T reduction' step.

$$pp_4^2 + qA^4p_5^2 + rB^4p_6^2 + (r - p - q)A^2p_4p_5 + (p - q - r)A^2B^2p_5p_6 + (q - p - r)B^2p_6p_4 + p(p - q - r)p_4 + q(q - r - p)A^2p_5 + r(r - p - q)B^2p_6 + pqr = 0$$

(3.6)

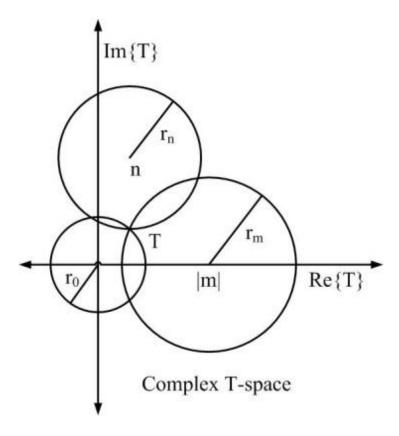

Here  $p = ||m| - n|^2$ ,  $q = |n|^2$ ,  $r = |m|^2$ ,  $A^2$ , and  $B^2$  are five real parameters to be determined in this step of the nonlinear calibration procedure. Once these calibration parameters are known, the real and the imaginary parts of the intermediate complex signal T can be determined from equation (3.7). Process of getting (3.7) is summarized in Figure 3.1 by plotting equation (3.4) in a complex-T plane.

$$Re\{T\} = \frac{r_0^2 - r_m^2 + |m|^2}{2|m|}$$

(3.7a)

$$Im\{T\} = \frac{1}{\sqrt{1-z^2}} \left[ \frac{r_0^2 - r_n^2 + |n|^2}{2|n|} - \frac{z(r_0^2 - r_m^2 + |m|^2)}{2|m|} \right]$$

(3.7b)

where  $r_0^2 = p_4$ ,  $r_m^2 = A^2 p_5$ ,  $r_n^2 = B^2 p_6$ , and  $z = \frac{q+r-p}{2\sqrt{qr}}$ .

Figure 3.1: Evaluation of T from equation (3.4) in the 'Receiver Calibration' step.